# Accelerating Financial Applications through Specialized Hardware – FPGA

By: Tri Dang John Rothermel Date: December 14, 2007

### EXECUTIVE SUMMARY

The need for computing power is continually increasing, especially in investment banks. These institutions use large clusters with many processor cores to approximate the future value of investments. Better computer performance correlates to increased accuracy and speed of calculations, which leads an edge on the investment bank's competitors and increased profit [1].

In the past, as demand for computing power increased, industry was able to keep pace; however, as processor cores increased in speed, more power was required. Higher power demands meant worsening power costs and a need for better heat dissipation. As an alternative to adding more processor cores to a system, Field Programmable Gate Array (FPGA) technology has been proposed as a possible alternative. FPGA advocates advertise fifty times speed improvements on their machines using a traditional CPU and FPGA coprocessor for Black-Scholes calculations, while using less power [2]. This project examined FPGA technology objectively in terms of speed and accuracy improvements for floating point mathematical operations.

The first objective was to evaluate current methods of floating point math in traditional CPUs and FPGAs. This base of knowledge helped us determine possible areas where FPGAs could augment traditional CPU performance. Following this research, we then developed benchmark tests for simple arithmetic on a CPU and with an FPGA coprocessor. Finally, we built on these findings by extending the benchmark tests to transcendental functions like exponentiation, logarithm, and trigonometry.

After researching current methods of processors to compute floating point math, we determined the optimal performance capabilities for the AMD Opteron (10h family) and Intel Core microarchitectures. Comparing both companies' advertized latencies and throughput for

varying SSE instructions yielded a few tables. The following table illustrates latency in clock cycles.

| Architecture/Instruction | Add | Multiply | Divide | SqRt |

|--------------------------|-----|----------|--------|------|

| AMD Opteron (10h family) | 4   | 4        | 16     | 27   |

| Intel Core               | 3   | 5        | 32     | 58   |

Table 1: Latency Comparison of Advertized Required Cycles for Opteron (10h Family) and Core

We then used a clock speed of 2.5GHz to compare theoretical execution times (in nanoseconds) of both AMD and Intel microarchitectures. Many AMD Opteron microprocessors operate between 2.4 and 2.6GHz. 2.5GHz was chosen as a reference point for comparison between the two microarchitectures.

| Architecture/Instruction | Add | Multiply | Divide | SqRt |

|--------------------------|-----|----------|--------|------|

| AMD Opteron (10h family) | 1.6 | 1.6      | 6.4    | 10.8 |

| Intel Core               | 1.2 | 2.0      | 12.8   | 23.2 |

Table 2: Latency Comparison of Advertized Required Time (ns) for Opteron (10h Family) and Core (based on

#### 2.5GHz core)

The final table displays theoretical throughput of different floating point operations in clock cycles. Throughput measures the rate of execution in clock cycles. For example, according to the following table one addition can be executed per clock cycle, due to pipelining and multiple execution units.

| Architecture/Instruction | Add | Multiply | Divide | SqRt |

|--------------------------|-----|----------|--------|------|

| AMD Opteron (10h family) | 1   | 1        | 17     | 24   |

| Intel Core               | 1   | 1        | 31     | 57   |

Table 3: Throughput Comparison (all double precision SIMD)

Both microarchitectures theoretically are able to perform an addition or multiplication every clock cycle, which for a 2.5GHz processor is every 0.4 nanoseconds. An FPGA on the other hand typically runs at about 100MHz. This comparison, however, does not take into account caching and other real world issues.

## Results

During the benchmark testing process, we first tested the speed and accuracy of an AMD Opteron 285, running at 2.6GHz. We started with basic arithmetic and then tested transcendental functions. These results include some overhead such as incrementing a pointer to an array of values and jump commands within a loop. The results of these benchmark tests are provided in the following table:

|       | Ave                                                         | erage time | per operatio | on for opera | ations and o | ptions (ns/o | op)    |        |

|-------|-------------------------------------------------------------|------------|--------------|--------------|--------------|--------------|--------|--------|

|       | Options: fastmath (f), loop-unrolling (l), sse (s), x87 (x) |            |              |              |              |              |        |        |

|       | S                                                           | х          | sf           | xf           | sl           | xl           | slf    | xlf    |

| Add   | 3.24                                                        | 3.22       | 3.22         | 3.22         | 3.22         | 3.22         | 3.22   | 3.22   |

| Sub   | 3.61                                                        | 3.58       | 3.60         | 3.62         | 3.59         | 3.59         | 3.60   | 3.57   |

| Mul   | 3.62                                                        | 3.62       | 3.62         | 3.62         | 3.62         | 3.62         | 3.62   | 3.62   |

| Div   | 3.61                                                        | 3.61       | 3.62         | 3.62         | 3.61         | 3.62         | 3.62   | 3.62   |

| Sqrt  | 10.89                                                       | 14.78      | 3.19         | 3.18         | 10.88        | 15.12        | 3.18   | 3.19   |

| Sin   | 3.25                                                        | 3.24       | 3.23         | 3.24         | 3.24         | 3.25         | 3.23   | 3.22   |

| Cos   | 3.62                                                        | 3.62       | 3.62         | 3.62         | 3.61         | 3.61         | 3.61   | 3.62   |

| Tan   | 3.62                                                        | 3.62       | 3.62         | 3.62         | 3.62         | 3.62         | 3.62   | 3.62   |

| ExpE  | 271.47                                                      | 256.72     | 3.61         | 3.61         | 282.55       | 258.65       | 108.04 | 108.29 |

| LogE  | 32.48                                                       | 32.97      | 3.92         | 35.72        | 32.62        | 32.84        | 35.67  | 35.66  |

| Log10 | 31.95                                                       | 32.75      | 3.38         | 32.43        | 32.45        | 32.11        | 32.52  | 32.51  |

#### Table 4: CPU Benchmark Results

The CPU was able to perform basic arithmetic, including division in three to four nanoseconds, while exponential functions tended to take a longer time. The fast-math compiler option was used effectively to speed up transcendental calculations, but did have some accuracy loss. When calculating trigonometric functions using the fast-math option, frequent not-a-number (NaN) results were recorded, while only an occasional error was recorded for other transcendental functions. All other comparisons yielded no recorded accuracy loss in a sample of ten thousand numbers. We concluded that a CPU is capable of high speed applications, but the fast-math option should only be used for non-trigonometric functions.

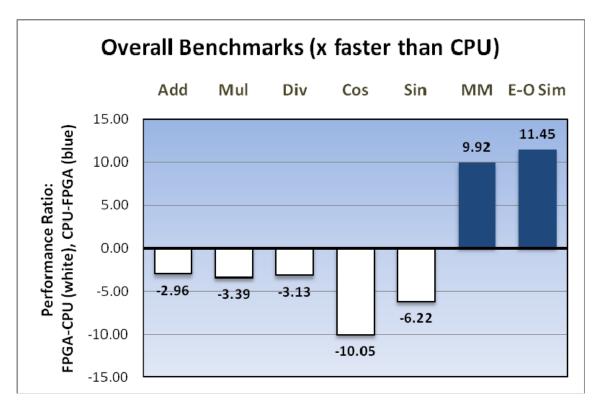

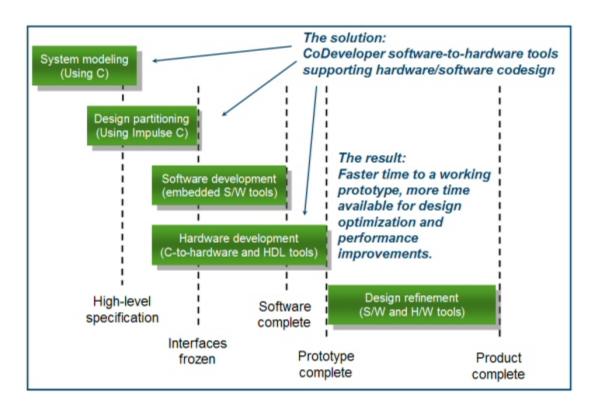

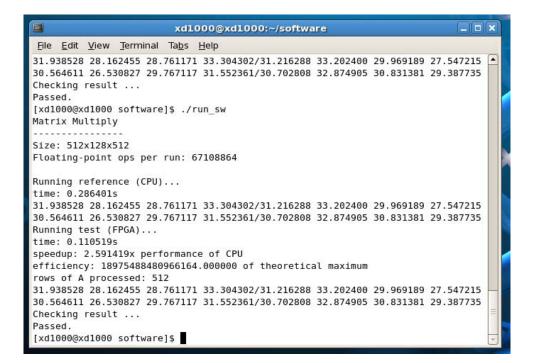

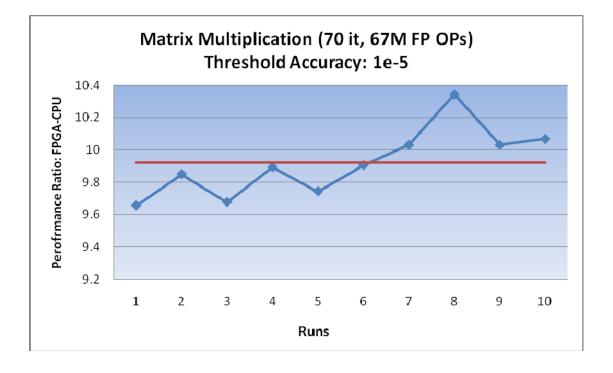

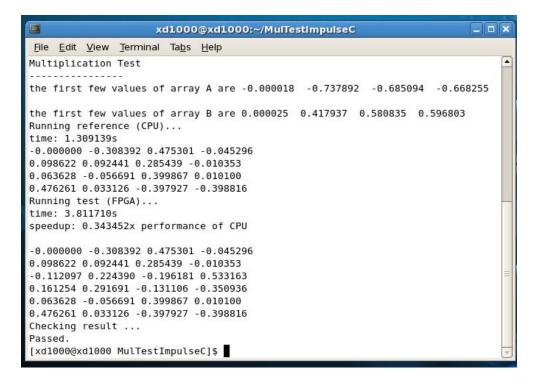

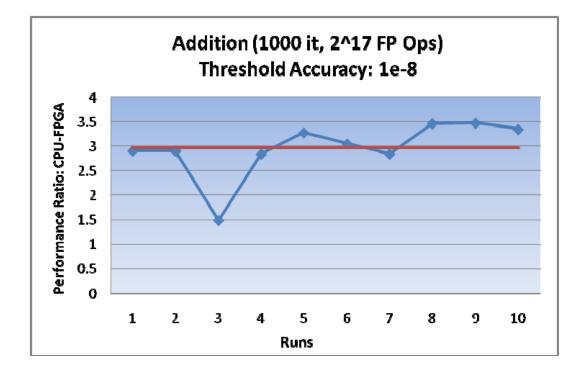

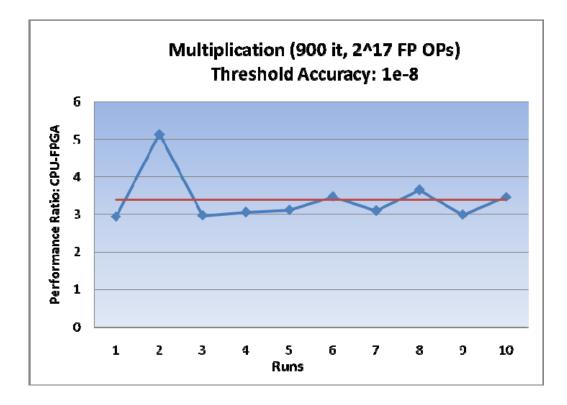

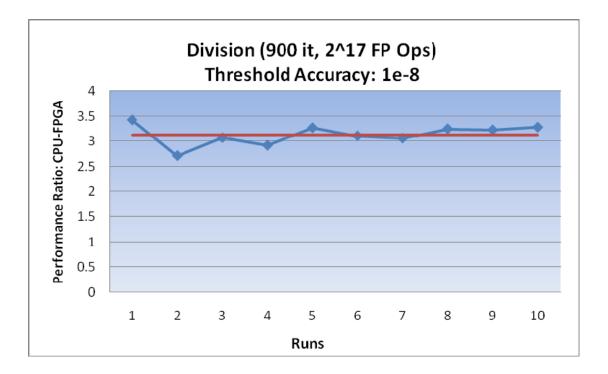

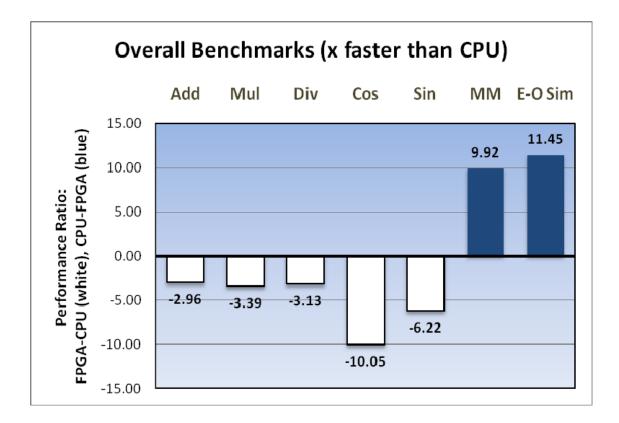

Using Impulse C, we were able to program the provided system to communicate with and utilize the included FPGA. The first example run was a matrix multiply example provided by Impulse Accelerated Technologies, which typically showed a ten times speed increase using the FPGA over the CPU. Altering this example, however, to compute basic arithmetic resulted in a three times decrease in speed of the FPGA. This is likely due to our using a larger data set, whose elements are only used once, and that these operations were too simplified to make use of parallelism. Altering the addition benchmark to use a smaller set of data and reading one entire array into the FPGA required us to remove the hardware pipeline. After this change was made, the FPGA again ran about three times slower than the CPU. Figure 1 summarizes our findings from the simple benchmark tests and the matrix multiply (MM) and European Options (E-O Sim) examples.

Figure 1: Overall Results (FPGA Times Faster than CPU)

Implementing these functions using Impulse C provided insight into the future of FPGA coprocessors. These conclusions include both the actual observed capabilities of the technology and limitations of the development tools.

- 1. FPGA coprocessors can significantly increase performance of certain mathematical operations. Certain functions, however, are better able to be run on an FPGA. The inherent ability to parallelize the function and the function's complexity factor into the FPGAs ability to outperform the CPU. Simple arithmetic and large data sets perform poorly on the FPGA compared to a modern processor. Since the FPGA has to overcome a slower clock and I/O overhead, the operations per datum must be considered. More complex operations that can be easily parallelized and use smaller data sets (like matrix multiplication, which incorporates 512 operations per datum, rather than 0.5 for arithmetic) can be accelerated to up to ten times faster than the CPU.

- 2. The XtremeData XD1000 uses a large Altera Stratix 2 FPGA, but in practice its performance was limited by several factors.

- a. The fabric of the FPGA only allows for a limited number of components. About 32 or so double precision adders or multipliers can be implemented into the FPGA, which only allows for a limited number of operations and limits precision for approximating series. In addition, the Quartus development tools occasionally run out of system memory during building of complex projects, causing it to crash. As a result, Quartus will only allow 16 parallel multiplier/adders, even though it can fit 32.

- b. The SRAM on the FPGA is only about 9Mbit, which limits the amount of data that can be loaded into the FPGA during processing

- c. The shared memory on the motherboard is limited to 4MB. This restricts the size of data on the system.

- d. After implementation, the internal clock of the FPGA typically runs at only 100-150MHz, which is many times slower than a 2-3GHz CPU.

- 3. Impulse Accelerated Technology's compiler, CoDeveloper, is useful in providing the communication interface between the FPGA and CPU; however, it has its limitations.

- a. Experience with the tools is required in order to optimize code and limit errors.

- b. The tools are fairly new and are constantly changing/evolving, so new developers need frequent support from Impulse, especially at first, before they understand the idiosyncrasies of the tools.

- c. Bugs currently in the alpha version of CoDeveloper 3.0 are substantial. Timing problems make development on the XD1000 system impossible without rolling back to a previous version. The older versions have limited capabilities and need patches to be used without errors.

- d. Current Altera and XtremeData libraries are limited to simple arithmetic. Square root and transcendental functions are not included in these libraries. Implementing these functions requires programming an approximation in VHDL with a wrapper to interface with CoDeveloper, or coding a primitive in C, which CoDeveloper then translates into HDL. In practice, bugs in the compiler did not allow us to program complex primitives (like natural log) in C and resulted in problems when programmed on the XD1000.

### **Recommendations**

Following the research conducted during this project, we developed several recommendations for future research into this technology.

- 1. Wait for a stable release of Impulse C CoDeveloper, or find an alternative for programming the system in order to avoid problems experienced using the alpha releases.

- 2. Future researchers should familiarize themselves with the currently available tools and continue the research that this project started. Improving the transcendental projects that we developed, including trigonometric, logarithmic, and exponential functions would be the next logical step. Following these evaluations they should test mathematical models with the FPGA coprocessor. In addition to these functions, testing other mathematical operations that can be easily parallelized would also contribute to this research.

- 3. Impulse provided a Black-Scholes European Options model for the XD1000 system at the end of this project. Due to time constraints, we were unable to adequately evaluate this implementation for accuracy. A continuation of this project would benefit from evaluating this design.

- 4. Our ability to test complex functions on the XD1000 was limited by our knowledge of VHDL wrappers and the development tools. Becoming familiarized with this process would open the door to testing many different mathematical operations.

- 5. FPGA technology is constantly improving. Keeping up to date on their currently available capabilities is essential. The research presented in this project was inconclusive as to the viability of FPGAs in the financial sector; however, improvements over time could make this the way of the future.

A full copy of this report can be obtained by contacting Dr. Jason Choy at JP Morgan Chase, at jason.k.choy@jpmchase.com

# Accelerating Financial Applications through Specialized Hardware – FPGA

A Major Qualifying Project Report Submitted to the Faculty of Worcester Polytechnic Institute in partial fulfillment of the requirements for the Degree of Bachelor of Science

By:

Tri Dang

John Rothermel

Date: December 14, 2007

Report Submitted To: Prof. Xinming Huang, WPI Prof. Arthur Gerstenfeld, WPI Prof. Michael Ciaraldi, WPI Dr. Jason Choy and JP Morgan Chase Inc.

### **ABSTRACT**

This project will investigate Field Programmable Gate Array (FPGA) technology in financial applications. FPGA implementation in high performance computing is still in its infancy. Certain companies like XtremeData inc. have advertized speed improvements of 50 to 1000 times for DNA sequencing applications using FPGAs, while using an FPGA as a coprocessor to handle specific tasks provides two to three times more processing power. FPGA technology increases performance by parallelizing calculations. This project will specifically address speed and accuracy improvements of both fundamental and transcendental functions when implemented using FPGA technology. The results of this project will lead to a series of recommendations for effective utilization of FPGA technology in financial applications.

In the future, FPGA technology could improve other computing as well. The data compiled during this project could be used to compare the benefits and cost of FPGA implementation for varying applications. For example, high performance computing is often essential for scientific research and military applications. This project will explore the potential for FPGA technology in the future of high performance computing.

## **AUTHORSHIP**

Tri Dang – Tri wrote the FPGA and IEEE754 standards section of the Background. In addition, Tri wrote the FPGA FPU and Impluse C section of the Methodology. Tri also contributed to the editing of the report.

John Rothermel – John wrote the Executive Summary, Abstract, Introduction, and Financial Systems and Challenges section of the Background. He also wrote the AMD Opteron (10h Family) and Intel Core Microarchitecture as well as the Benchmark Testing sections of the Methodology. In addition, he wrote the Results and Conclusions as well as the Recommendations.

## **ACKNOWLEDGEMENTS**

We would like to graciously thank the following organizations and individuals for their help in this project:

- JP Morgan Chase for their involvement in this process, including providing the facilities and tools necessary during the course of the project

- Dr. Jason Choy, our sponsor, whose advice and guidance was invaluable in the development of the project

- Our advisors, Professors Gerstenfeld, Huang and Ciaraldi for their support and guidance

- AMD, Inc. for providing XD1000 systems to JP Morgan Chase and WPI for development

- XtremeData, Inc. for their technical support during setup of the XD1000 system

- Impulse Accelerated Technologies, Inc. for their considerable support during the project using their development tools

- The New York Public Library for making their online databases and books available for our use

- The various universities, organizations, and individuals whose works were cited in this report and provided information essential to our understanding of the project

## TABLE OF CONTENTS

| EXECUTIVE SUMMARY                                                     | i    |

|-----------------------------------------------------------------------|------|

| Results                                                               | iii  |

| Recommendations                                                       | vii  |

| ABSTRACT                                                              | X    |

| AUTHORSHIP                                                            | xi   |

| ACKNOWLEDGEMENTS                                                      | xii  |

| TABLE OF CONTENTS                                                     | xiii |

| TABLE OF FIGURES                                                      | xvi  |

| TABLE OF TABLES                                                       | xix  |

| 1.0 INTRODUCTION                                                      | 1    |

| 2.0 BACKGROUND                                                        | 4    |

| 2.1 Financial Systems and Challenges                                  | 4    |

| 2.1.1 Mathematical Models and Simulations Applied in Computer Systems | 5    |

| 2.1.2 High Performance Computing (HPC)                                | 9    |

| 2.2 Field Programmable Gate Array (FPGA) Technology in HPC            | 16   |

| 2.2.1 History of FPGA technology                                      | 16   |

| 2.2.2 FPGA Architecture                                               | 17   |

| 2.2.3 Advantages and Disadvantages of FPGAs                           | 22   |

| 2.2.4 Available FPGA Programming Languages                      |     |

|-----------------------------------------------------------------|-----|

| 2.3 IEEE754 Floating point standard                             |     |

| 2.3.1 Importance and History of IEEE754 Floating Point Standard |     |

| 2.3.2 Definition and Standard Convention                        |     |

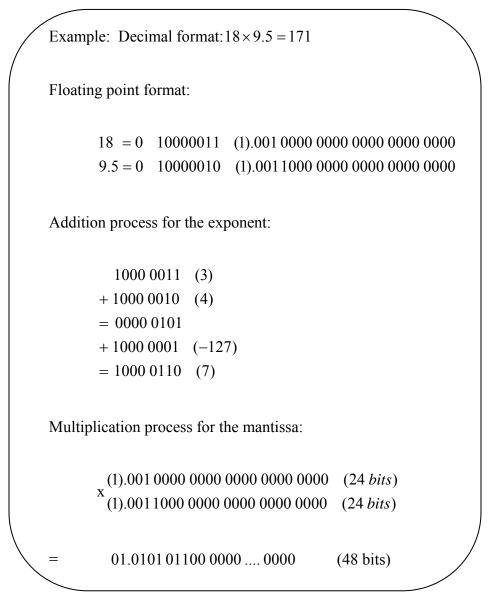

| 2.3.3 Floating point arithmetic                                 | 41  |

| 2.4 Summary                                                     | 53  |

| 3.0 METHODOLOGY                                                 | 54  |

| 3.1 Current Methods for Floating Point Calculations             | 54  |

| 3.1.1 FPGA FPU                                                  | 55  |

| 3.1.2 AMD Opteron (10h Family) Microarchitecture                | 69  |

| 3.1.3 Intel Core Microarchitecture                              | 77  |

| 3.1.4 Summary                                                   | 80  |

| 3.2 Benchmark Testing using Fundamental Mathematical Functions  | 81  |

| 3.2.1 XtremeData Inc., XD1000 System                            | 81  |

| 3.2.2 Benchmark Testing on the Opteron                          | 82  |

| 3.2.1 Measuring Accuracy                                        | 86  |

| 3.2.3 Benchmark on FPGA                                         | 87  |

| 4.0 RESULTS AND CONCLUSIONS                                     | 111 |

| 4.1 Problems Encountered                                        | 111 |

| 4.1.1 Set Up                                                    | 111 |

| 4.1.2 Communication                             |     |

|-------------------------------------------------|-----|

| 4.1.3 Impulse C Implementation                  |     |

| 4.1.4 XD1000 System Limitations                 | 116 |

| 4.1.5 System Memory Limitations on the User PC  |     |

| 4.1.6 Summary                                   | 117 |

| 4.2 CPU Benchmark Results                       |     |

| 4.3 FPGA Coprocessor Results                    |     |

| 4.3.1 Matrix Multiplication (Double Precision)  | 122 |

| 4.3.2 Addition and Multiplication               | 125 |

| 4.3.3 Division                                  |     |

| 4.3.4 Square Root and Transcendental Functions  |     |

| 4.3.5 Impulse Provided European Options Example |     |

| 4.4 Conclusions                                 |     |

| 5.0 RECOMMENDATIONS                             |     |

| 6.0 WORKS CITED                                 |     |

## TABLE OF FIGURES

| Figure 1: Overall Results (FPGA Times Faster than CPU)                   | iv |

|--------------------------------------------------------------------------|----|

| Figure 2: Monte Carlo Approx. of PI                                      | 8  |

| Figure 3: Early Computer Performance (1950-1975)                         | 10 |

| Figure 4: Performance Cost over Time                                     | 11 |

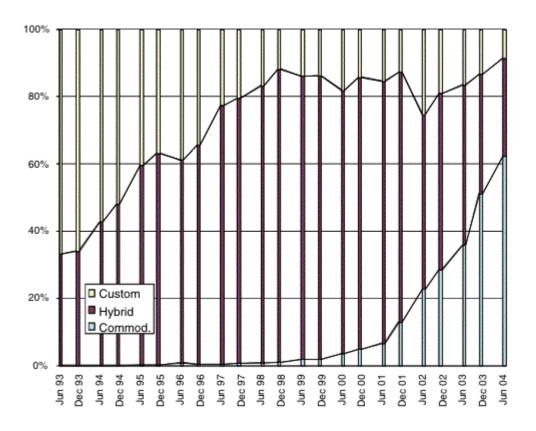

| Figure 5: Custom, Hybrid, and Commodity Processor Improvements over Time | 12 |

| Figure 6: Prevalence of Custom, Hybrid, and Commodity Based Systems      | 13 |

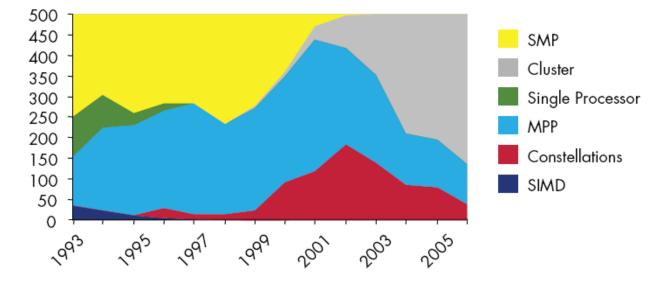

| Figure 7: HPC Arch over Time                                             | 15 |

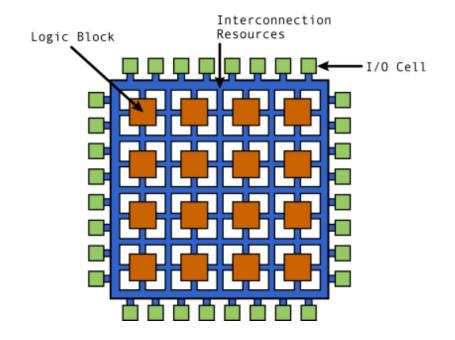

| Figure 8: Generic FPGA architecture                                      | 18 |

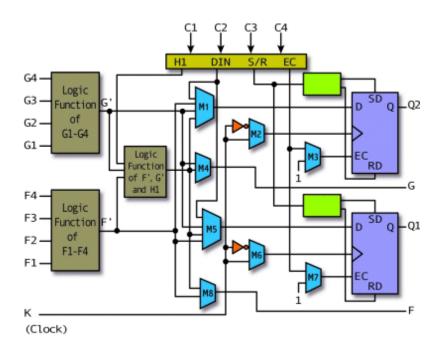

| Figure 9: Configurable Logic Block (CLB)                                 | 19 |

| Figure 10: I/O Blocks Circuitry of a FPGA                                | 20 |

| Figure 11: Programmable Interconnects                                    | 21 |

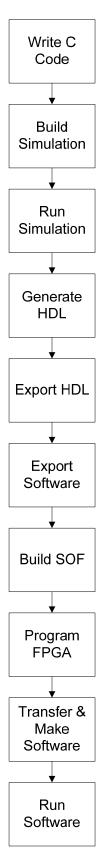

| Figure 12: Design Flow- Hardware (left) Software (Right)                 | 25 |

| Figure 13: Level of Abstraction of different languages                   |    |

| Figure 14: Hardware designing with Impulse C                             | 29 |

| Figure 15: Flush to Zero (above) and Gradual Underflow (below)           | 35 |

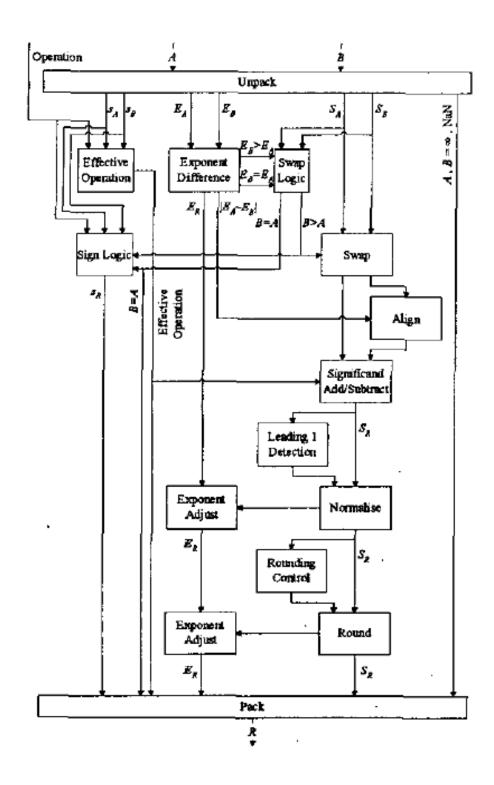

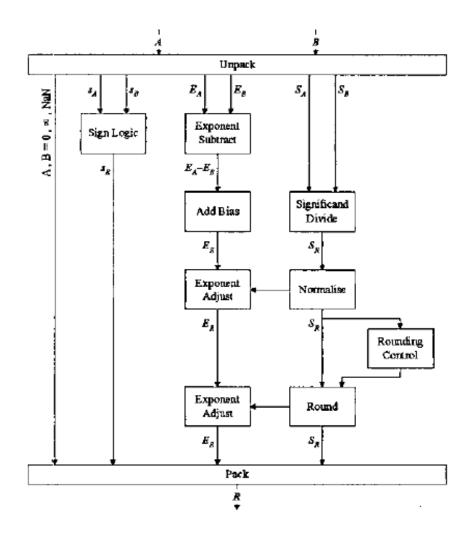

| Figure 16: FPGA's Addition/Subtraction circuit                           | 59 |

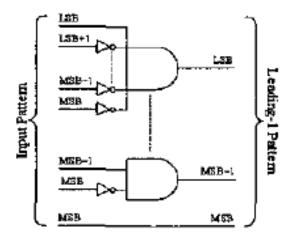

| Figure 17: Leading "1" Detection block                                   | 60 |

| Figure 18: Multiplication unit                                           | 62 |

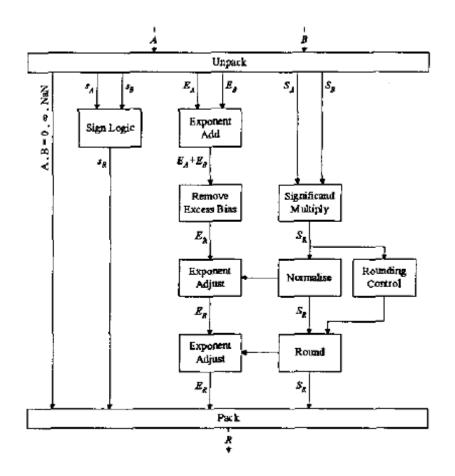

| Figure 19: Division unit                                                 | 65 |

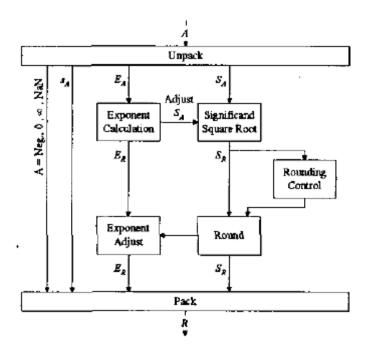

| Figure 20: Square root unit                                              | 67 |

| Figure 21: Block Diagram for AMD Opteron (10h Family) Processors         | 70 |

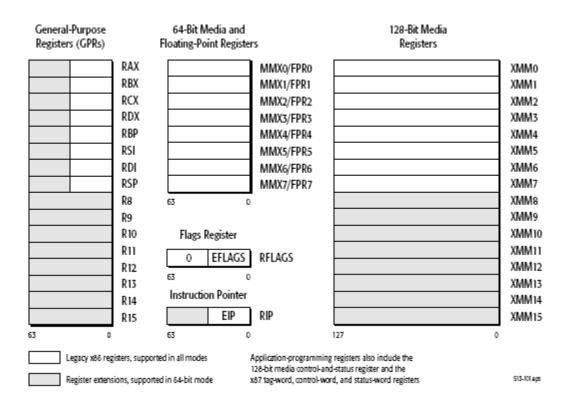

| Figure 22: Application Programming AMD Opteron (10h Family) Registers           | 73      |

|---------------------------------------------------------------------------------|---------|

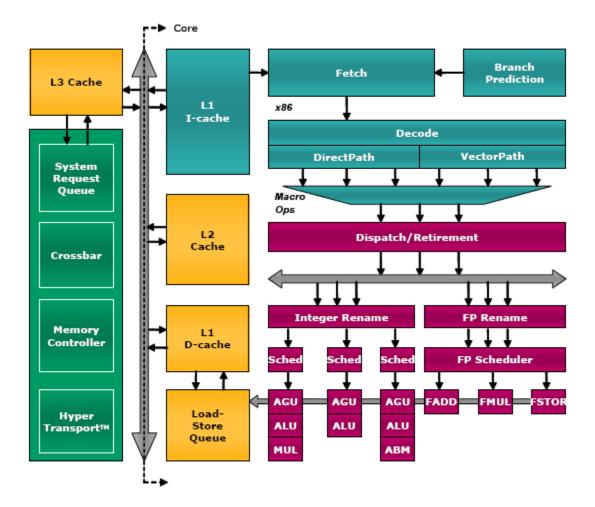

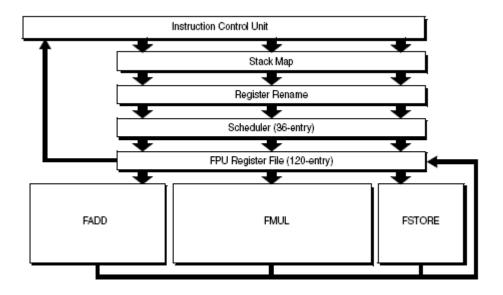

| Figure 23: FPU for AMD Opteron (10h Family) Microarchitecture                   | 74      |

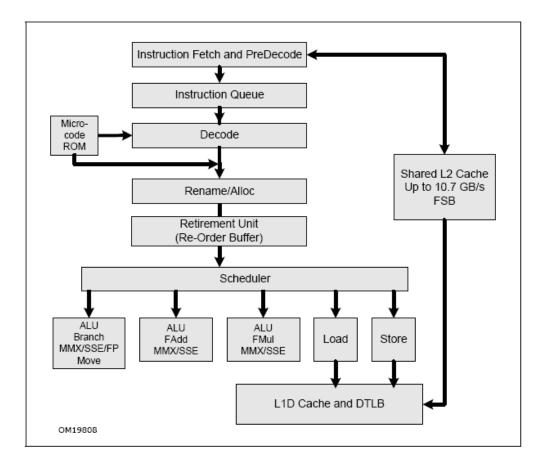

| Figure 24: Intel Core Microarchitecture                                         | 77      |

| Figure 25: XD1000 HW Specification                                              | 81      |

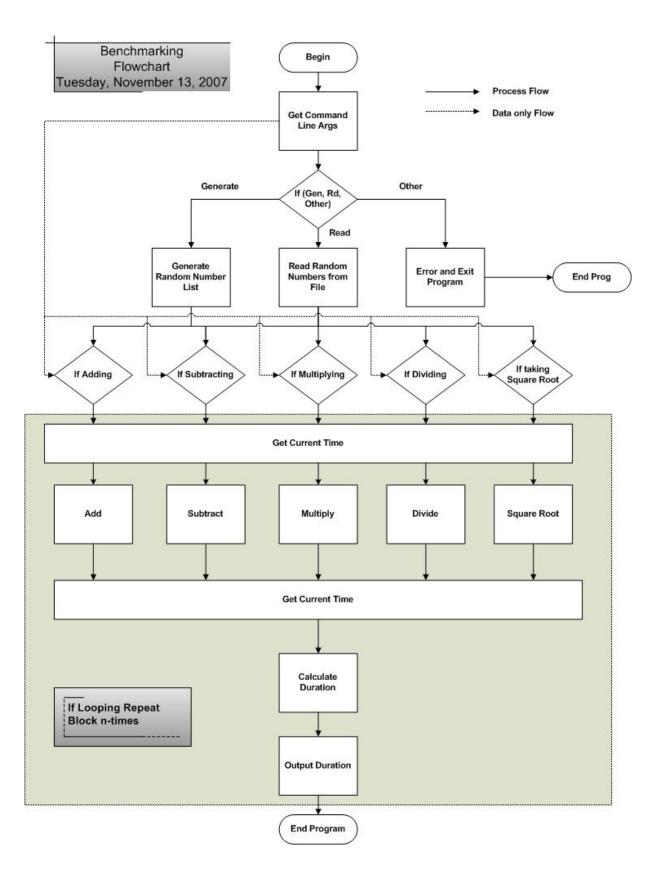

| Figure 26: Opteron Benchmark Flowchart                                          |         |

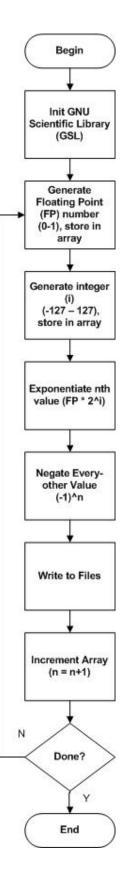

| Figure 27: Random Number Generator Flow Chart                                   | 85      |

| Figure 28: Developing Process with Impulse C                                    |         |

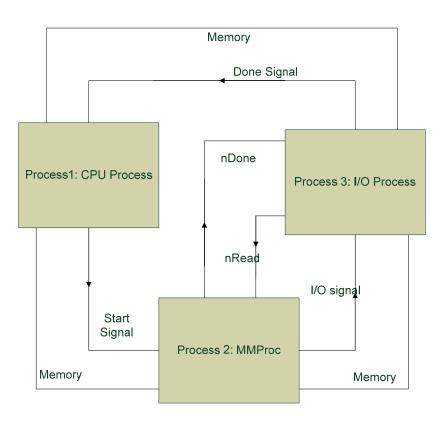

| Figure 29: Generic top level block diagram for Comparison Performance Project   |         |

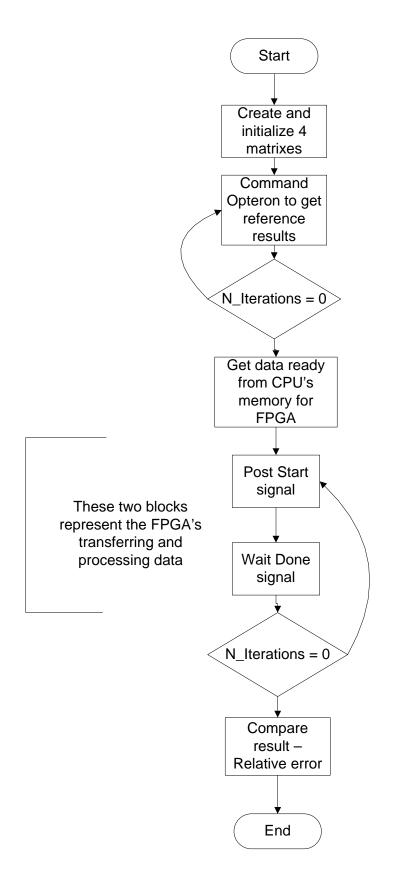

| Figure 30: CPU process flow chart                                               |         |

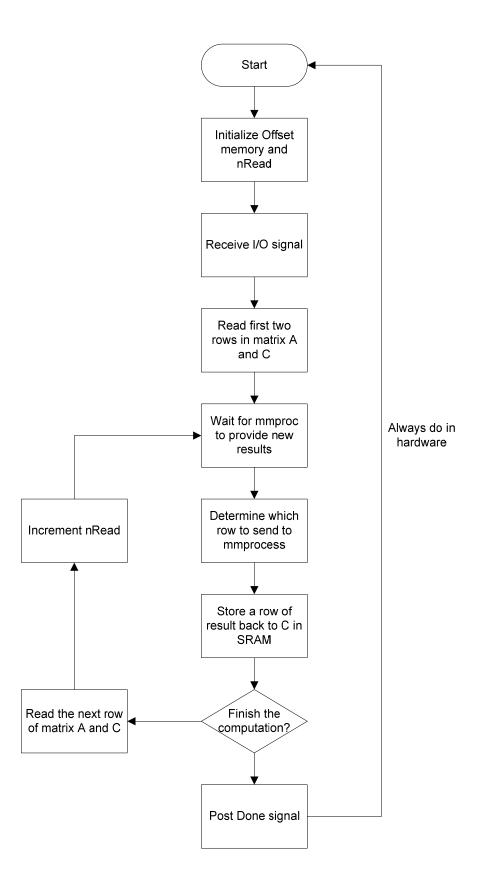

| Figure 31: Flow chart for IO process                                            |         |

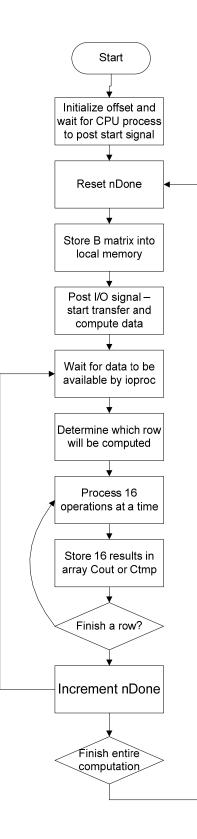

| Figure 32: Flow chart for mmproc                                                | 101     |

| Figure 33: Matrix Multiply on XD1000 (replace!)                                 | 123     |

| Figure 34: Matrix Multiplication showing runs (blue) and average (red)          | 124     |

| Figure 35: Addition Benchmark on the XD1000                                     | 125     |

| Figure 36: Multiplication Benchmark on the XD1000                               | 126     |

| Figure 37: Addition Benchmark Results, each run (red) and average (blue)        | 127     |

| Figure 38: Multiplication Benchmark Results, runs (blue) and average (red)      | 128     |

| Figure 39: Addition Test Version 2                                              | 129     |

| Figure 40: Division Benchmark Results, each run (blue) and average (red)        | 131     |

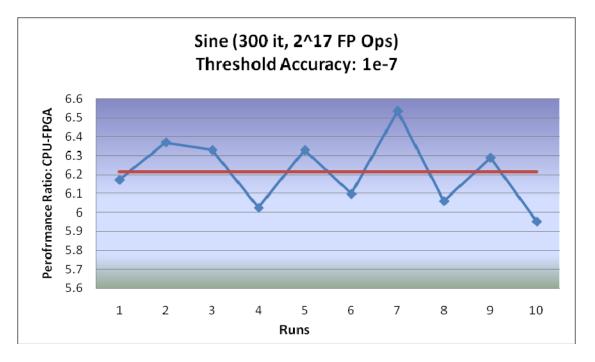

| Figure 41: Sine Benchmark Results, Results per Run (blue) and Average (red)     | 133     |

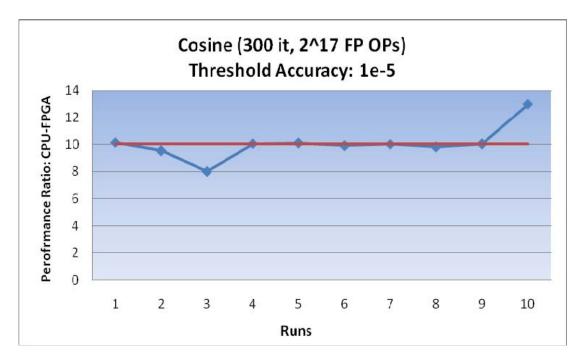

| Figure 42: Cosine Function Benchmark, Times per Run (red) and Average (blue)    | 135     |

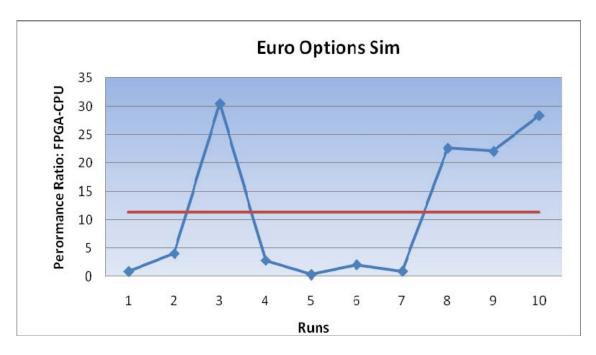

| Figure 43: European Options Simulation (FPGA Times Faster), Ind Runs (blue) and | Average |

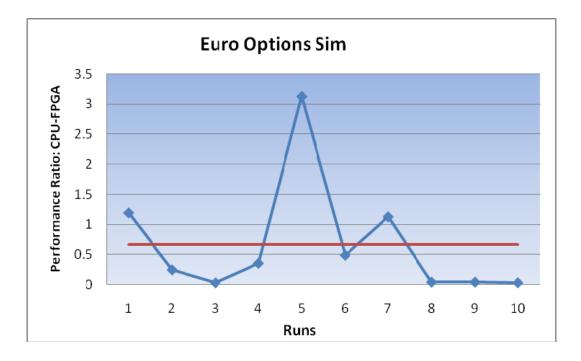

| (red)                                                                           | 138     |

| Figure 44: European Options Simulation (CPU Times Faster), Ind Runs (blue) and Average |  |

|----------------------------------------------------------------------------------------|--|

| (red)                                                                                  |  |

| Figure 45: Overall Results (FPGA times faster than CPU)                                |  |

## TABLE OF TABLES

| Table 1: Latency Comparison of Advertized Required Cycles for Opteron (1 | 0h Family) and  |

|--------------------------------------------------------------------------|-----------------|

| Core                                                                     | ii              |

| Table 2: Latency Comparison of Advertized Required Time (ns) for Opteron | (10h Family)    |

| and Core (based on 2.5GHz core)                                          | ii              |

| Table 3: Throughput Comparison (all double precision SIMD)               | ii              |

| Table 4: CPU Benchmark Results                                           | iii             |

| Table 5: Summary of Floating Point Representation                        |                 |

| Table 6: Range of Values for Floating Point Numbers                      |                 |

| Table 7: Summary of Floating Point Representation                        |                 |

| Table 8: Special Operations                                              |                 |

| Table 9: Invalid Operations                                              |                 |

| Table 10: Latency Comparison of Advertized Required Cycles for Opteron ( | 10h Family) and |

| Core                                                                     |                 |

| Table 11: Latency Comparison of Advertized Required Time (ns) for Optero | on (10h Family) |

| and Core (based on 2.5GHz core)                                          |                 |

| Table 12: Throughput Comparison (all double precision SIMD)              |                 |

| Table 13: CPU Benchmark Results                                          |                 |

| Table 14: Matrix Multiply Results (10 runs)                              |                 |

| Table 15: Addition Benchmark Test (10 runs)                              | 127             |

| Table 16: Multiplication Benchmark Results (10 runs)                     |                 |

| Table 17: Division Benchmark Results (10 runs)                           |                 |

| Table 18: Sine Benchmark Results                                         |                 |

| Table 19: Cosine Benchmark Results            | . 134 |

|-----------------------------------------------|-------|

| Table 20: European Options Simulation Results | . 137 |

### **1.0 INTRODUCTION**

Technology is continually moving forward. In today's world electronics are constantly getting smaller and more powerful. This is especially true in the computer world where speed has been improving exponentially since the 1960s. According to Moore's Law, the number of transistors on a chip doubles every two years. This exponential growth leads to ever increasing computing power at lower cost [3].

In the past, increased computing was achieved by increasing the speed of the processor. Due to physical limitations, however, this approach is no longer practical. Faster processors use more power and generate more heat, which then must be dissipated. In addition, processors are subject to certain bottlenecks due to limited memory addressing and multilayered memory [4-6].

One possible solution is implementing Field-Programmable Gate Array (FPGA) technology as a coprocessor to the existing processor in the system. FPGAs have the advantage of much lower power consumption and the ability to do tasks in parallel while sacrificing flexibility [5, 6]. According to FPGA Acceleration in HPC: A Case Study in Financial Analytics (2006):

"An FPGA coprocessor programmed to hardware-execute key application tasks can typically provide a 2X to 3X system performance boost while simultaneously reducing power requirements 40% as compared to adding a second processor or even a second core. Fine tuning of the FPGA to the application's needs can achieve performance increases greater than 10X" (p. 2).

It is possible to use the strengths of both traditional processors and FPGAs to take computing to the next level of performance.

1

In the world of finance, computing power directly translates into money. Investment banks use large clusters of computers to calculate and minimize risk. The Federal Deposit Insurance Corporation (FDIC) then determines the risk-weighted assets (RWA) based on these calculations. RWA refers to the amount of capital within banks that are weighted by risk. For large banks, this will often translate into billions of dollars [1]. Unfortunately, risk calculations must take into account many different situations, often using Monte Carlo simulation. These simulations are computationally intensive and can take days to complete [1]. Improving the computing power of these systems would decrease the time required to run simulations, allowing investment banks to run further models and better approximate risk. This lowered risk would then translate into less money held in capital reserve, which is a special fund where large amounts of money are set aside for special projects and expenses. Lower, yet sufficient capital held in the reserve fund would allow for increased available monetary resources within the bank.

The purpose of this project is to evaluate FPGA coprocessors for financial calculations in order to determine the feasibility of implementing them into existing clusters. This will be done by completing three objectives:

- Research current methods of computing in microprocessors Intel/AMD and FPGAs to determine physical limitations of both platforms.

- 2. Test microprocessor and FPGA implementations of different fundamental mathematical functions using benchmarks to find timing differences.

- 3. Implement complex functions, such as trigonometry and logarithm, whose approximations are based on fundamental mathematical functions, to determine physical limitations and timing differences between FPGA and microprocessor technology.

2

In order to meet these objectives, we will examine code for different implementations of the algorithms in which we are interested. We will determine the strengths and weaknesses of these methods and then use that data to aid further research. Following this phase, we will use a system to test performance of the CPU alone and with an FPGA coprocessor to determine improvement of the system. These tests will allow us to make recommendations to an investment bank as to further steps in developing this technology if it is found feasible.

In summary, advances in computer technology have increased computing speeds exponentially in past decades. This has usually been achieved by using more transistors and raising processor speed. As processor speeds improve, however, power requirements also increase. FPGA coprocessors have been suggested as a possible solution to continue raising processing power. This increase is especially important in the finance sector where financial risk analysis can translate into billions of dollars profit or loss. This project will address the feasibility of FPGA coprocessors in computing financial risk calculations.

### 2.0 BACKGROUND

In the following section, we will discuss several important issues in determining the feasibility of FPGA coprocessors in financial applications. First, we address how financial institutions approximate performance of different markets and the challenges inherent in this process. We then examine current methods of high performance computing and how technology has evolved. Next, we discuss FPGA technology, including its strengths, weaknesses, and the development process. Finally, in order to better understand low-level computations, we outline the current floating point standard as defined by IEEE754 as well as mathematical operations using this standard. This information will provide the base of knowledge upon which we built this project.

### 2.1 Financial Systems and Challenges

Predicting market performance is essential for investment banks. This process allows banks to maximize profits and minimize risk. The FDIC was created by Congress in order to keep the national financial system stable and to ensure customer confidence [7]. The FDIC mandates a deposit amount from banks based on its ability to predict risk and other factors. The deposit could, for instance, fall between five and eight percent [1], which would correspond to billions of dollars in a large investment bank's portfolio. Banks typically determine this risk based on financial models and computer simulation. Unfortunately, randomness is inherent in the market, so simulations need to take into account many possible outcomes.

#### 2.1.1 Mathematical Models and Simulations Applied in Computer Systems

One of the most commonly used models for determining the future value of options is the Black-Scholes model. This model has proven to be fairly accurate over time and is the cornerstone for much of the market prediction models used by investment banks. This model is then often applied in simulation in order to determine the future values based on randomness. In many cases Monte Carlo simulation is used for this purpose [8]. The combination of the Black-Scholes model and Monte Carlo simulation allows for accurate predictions that account for randomness in the market.

#### 2.1.1.1 Black-Scholes Model

The Black-Scholes Model was developed by Fischer Black and Myron Scholes around 1970 as a model for finding the future value of options, which were not common then. Although their work was not widely accepted at the time, it has become one of the most widely accepted financial models today [9].

According to Webster's Dictionary, an option is, "a right granted by a corporation to officers or employees as a form of compensation that allows purchase of corporate stock at a fixed price usually within a specified period" [10]. For example, a person receives an option from Company A. This option allows the individual to buy 100 shares of Company A's stock at the current market price of one dollar in one year. If in one year Company A's stock price is at two dollars, the individual would likely exercise the option (i.e. buy the stock), which would allow him to purchase 100 shares of Company A's stock for one dollar each, or one hundred dollars. The shares, however, are worth two dollars each. If the individual immediately sells the option at the current market price, he would earn two hundred dollars less the cost of the shares, or one hundred dollars. If, on the other hand, the stock price in a year was worth fifty cents, the

individual would not exercise the option and it would therefore be worthless. An option, therefore, for an individual cannot result in a loss, but only increases in value with a company or becomes worthless.

The Black-Scholes model for approximating future value of options is based on the Brownian motion model, which is a form of Marchov processes [8]. The Brownian motion model is given below:

$$dS = \mu S dt + \sigma S dW$$

Where S, in this case, is the value of a security,  $\mu$  is the drift rate,  $\sigma$  is the volatility, W(t) is a standard Brownian motion, and dt is a time increment [8].

The Black-Scholes model is a partial differential equation given by the following expression:

$$\frac{\partial V}{\partial t} + \frac{1}{2}\sigma^2 S^2 \frac{\partial^2 V}{\partial S^2} + rS \frac{\partial V}{\partial S} - rV = 0$$

Where the value V(t,s) changes over the interval  $0 \le t \le T$ , where T is the time at maturity. In addition, r is the risk-free interest rate, which is the rate of change for short-term non-risk securities, such as bank accounts [8].

This model, however, makes certain assumptions, which are also its limitations. It first assumes that the market has no transaction costs, which is rarely the case. It assumes market price varies according to the geometric Brownian motion process. It is assumed that the security is perfectly divisible (i.e. fractions of shares are possible). In addition, trading is continuous and the risk free rate is assumed constant. Finally, the no-arbitrage principle is held [8]. This principle states that shareholders pay for the actual cash flow, not earnings [11]. While assumptions are essential in mathematical models, it is important to realize their limitations.

In practice, the Black-Scholes model is often altered depending on the financial institution and other factors. Due to the complexity of the model, computers typically do the computations. Many spreadsheet programs are available today that utilize this model. Although other models are available, Black-Scholes is the best known model for derivatives [12].

#### 2.1.1.2 Monte Carlo Simulation

Monte Carlo Simulation is a simulation method based on random numbers, which is often used in order to determine multidimensional integrals and simulate stochastic (i.e. random) phenomena [13]. As opposed to, for instance, simply using averages, simulation allows an individual to know the probability and range of expected outcomes. This method enables an investor or manager to make better decisions that take into account the variability of the process [14].

One application of Monte Carlo simulation is determining  $\pi$  to a certain precision. This is done by first taking a unit square and then drawing a quarter circle inside it as seen in Figure 2. We then use a random number generator to pick points within the square. If the points are within the area of the quarter circle, they are recorded as hits. If one then takes the ratio of hits to the ratio of coordinates generated and multiplies by four, the result is an approximation for  $\pi$ , which becomes better with more points [13].

Figure 2: Monte Carlo Approx. of PI

Another example of Monte Carlo simulation is in predicting the market for a new product. First, assume that a new product will sell between ten-thousand and fifty-thousand units and that the probability is defined by a normal curve. A Monte Carlo approach would pick random values between these points according to a normal distribution (i.e. pick fewer values near the edges and more near the center) and then use these values for further analysis. The simulation could then multiply these values by an expected sale price less the production cost per unit to determine profit. Using this simulation, the company would know the range of possible profit and the probability of each range of profit.

While Monte Carlo simulation is useful for evaluating processes that involve randomness, the assumptions that are made can lead to inaccuracy. As in the previous example, we assumed that the sales would be between ten and fifty thousand and that the probability of sales would follow a normal distribution. If these assumptions are incorrect the simulation will be inaccurate. Care must be taken to choose values that properly represent the process.

Monte Carlo simulation is used frequently to model processes that involve randomness. Although it is a powerful tool, care must be taken to make appropriate assumptions during the simulation process. Monte Carlo simulation can be used to provide ranges and probability of outcomes, which allow an individual to make informed decisions.

### 2.1.2 High Performance Computing (HPC)

High Performance Computing (HPC) refers to the best currently available class of computing systems. Computers, however, are continuously improving, which leads to a changing HPC standard. In this section, we discuss the evolution of HPC and the current standards for supercomputers.

### 2.1.2.1 History of HPC

The development of computers began during World War 2 when the United Kingdom developed the first fully electronic, digital computer, called the Colossus Machine. This computer was used to break German ciphers and was classified until the 1970s [15, 16]. Following the development of the Colossus Machine, the better known ENIAC was finished in 1945 for calculating artillery ballistics. This trend in supercomputer development for the government would continue for years with the Department of Defense (DoD). The DoD developed the majority of the computers until the late 1950s when the National Security Agency (NSA) began using supercomputers for cryptography [15].

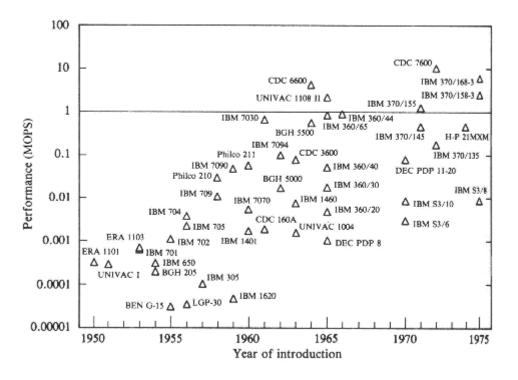

Figure 3 shows early development of high performance computing until the 1970s in millions of operations per second (MOPS). From about 1950 until 1970, the world's best computers improved from about 0.5 thousand operations per second (KOPS) to 10 MOPS, a difference of 20,000 times.

Figure 3: Early Computer Performance (1950-1975)

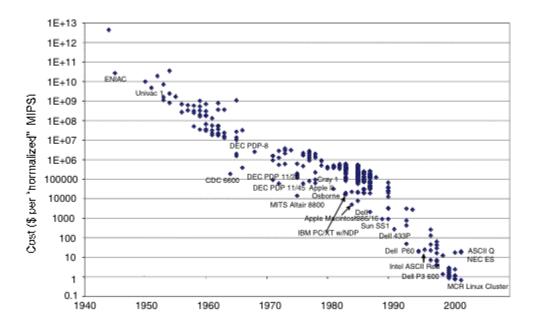

The next big development in computing would come in late 1971 with the development of the microprocessor [15, 17]. This computer processor developed by Intel was a shift in development from custom processors to lower performance general use processors. While they were not largely used in supercomputers for quite some time, general use processors allowed lower end systems to be built at much lower cost. The trend of increased processing power at lower cost has continued to the present. Figure 4 displays this trend up to 2000 [15].

Figure 4: Performance Cost over Time

In 1976 Cray Research developed the Cray-1. This supercomputer utilized an innovation known as vector architecture. This involved storing vectors of floating point data into vector registers when called, which could then be manipulated in an arithmetic unit at much higher speeds. Following vector architecture, massively parallel processor (MPP) systems began to be developed. This architecture involved increasing computing power by using large numbers of individual processors [15]. The increase in performance, however, would not be linear as Amdahl's Law states that the performance gain of additional processors is much less than the sum of the processors (e.g. it will take nine processors to triple the performance of one). [18].

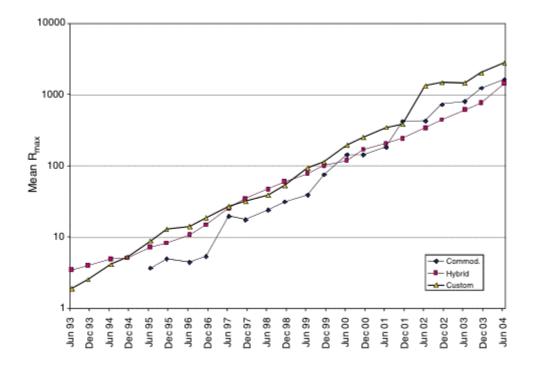

As the 1980s and 1990s progressed, custom processors and connections, once essential for HPC, began to become less practical. Complimentary metal-oxide semiconductor (CMOS) transistors began to be used in commercial processors. Large numbers of CMOS transistors could be placed on a single die, which lead to the microprocessor. These were used increasingly throughout the 1980s and 1990s in certain systems, which could perform nearly as well as customized solutions at lower cost. Figure 5 illustrates performance increases in supercomputers using customized, hybrid, and commodity (general use) processors over time for the world's best computer systems. While custom systems in the mid 1990s were significantly better than commodity systems, the rate of improvement over time for commodity processors was about 111% annually compared to 94% for custom systems [15].

Figure 5: Custom, Hybrid, and Commodity Processor Improvements over Time

Due to the increasing performance of commodity-based systems, customized solutions have largely fallen out of favor as can be seen in Figure 6. The trend of the future appears to be inexpensive HPC by utilizing commodity processors.

Figure 6: Prevalence of Custom, Hybrid, and Commodity Based Systems

### 2.1.2.2 Architecture

A supercomputer has several main components. These include processors, memory, the I/O system, and the connections. The basic function of a processor is to execute program functions including arithmetic and logical functions. The memory allows the system to store the current state of the machine. These two components make up a node, which can consist of single or multiple processors and a memory system of varying size. Typically hundreds or thousands of nodes are used in a typical supercomputer. The I/O system allows computers to access peripheral devices such as disks. Finally, the connections allow the system components to communicate with each other. All four components allow the system to work properly [15].

A number of architectures have been used in supercomputers over the years. The first and simplest is a single processor design. While single processors are rarely used even in personal computing currently, they were used in the past before computing demand exceeded their capabilities.

Another system that was used somewhat in the early nineties was single instruction multiple data (SIMD) systems, which could apply a single instruction to vectors of data to increase performance. These systems have since fallen out of favor as companies move to different methods of HPC.

One system, utilized primarily in the early 1990s, was called symmetric multiprocessing (SMP). SMP utilizes multiple processors with a common memory block per node. A system called massively parallel processing (MPP) involves having hundreds or thousands of individual processors working in parallel. Typically SMP and MPP systems utilize custom processors and/or components, which adds to their cost.

Currently the most common architecture for HPC is the cluster. Cluster architecture is achieved by connecting computers via a network so that they work similarly to a single computer. Often clusters are built by connecting several computers with the same hardware; however, clusters can be built using computers with different hardware. The advantage of this architecture is simplicity. Any group of computers can be connected using gigabit Ethernet cards, which are typically available in any new computer, or any other network interface [5, 15]. A variant on the cluster is called the constellation, which is similar, except that the individual computers contain SMP nodes [19]. Constellations seemed to be the wave of the future in the early 2000s, but recently are being used less by the world's fastest computers.

Figure 7 shows prevalence of HPC architectures over time for the 500 fastest computers in the world as rated by Top500 [20]. Cluster computing has increased substantially since 2000. SMP architecture became nearly nonexistent since 2001 in the top performing computers. In

14

addition, MPP and constellation systems decreased significantly in past years. This is likely due to the cost-effectiveness and ease of implementation of cluster computers [5, 15, 21].

Figure 7: HPC Arch over Time

Although many different architectures and technologies have developed in the past, cluster computing appears to be the way of the future. This architecture is scalable, easily implemented and less costly than its competitors. Cost-effectiveness is achieved by utilizing commodity processors, which do not require significant development to implement, unlike MPP and SMP systems. The future of computing is likely to continue balancing performance, cost, and ease of implementation.

# 2.2 Field Programmable Gate Array (FPGA) Technology in HPC

Previously we discussed a number of methods that are used in HPC. Certain methods, especially clusters, are preferred in HPC because of their cost-effectiveness. However as a system expands due to increasing demand in speed and accuracy, higher power dissipation is required as the result of increasing clock speeds and additional processors. Although there are solutions that address this problem, such as multi-core processors or improving the cooling system, they have not completely solved the issue of power consumption.

One approach to solving this problem is using FPGA technology. FPGAs are semiconductor devices that contain programmable logic components, logic blocks, and programmable interconnects. FPGAs are programmed in the field rather than at fabrication. Like gate arrays, FPGAs have arrays of uncommitted logic. As the device is programmed, the configuration of the array is determined by applying a large negative voltage to individual connections [22]. Previous FPGA generations can contain up to 60,000 free programmable logic blocks, 64 kilobits of RAM and operate at clock frequencies of a few megahertz [23], while more modern processors have considerably more RAM and may operate at a few hundred megahertz, which significantly increases their capabilities. At first sight, FPGAs may seem inferior to the current generation of processors and their application-specific integrated circuit (ASIC) counterpart. However, FPGAs utilize parallel mechanisms and are fully programmable, which are the keys for its extensive development and applications today.

# 2.2.1 History of FPGA technology

Field programmable gate array technology originated from complex programmable logic devices (CPLDs) research in the 1980s. In 1984, Xilinx co-founder Ross Freeman invented the FPGA. "The concept requires a lot of transistors, but at that time, transistors were extremely

precious", said Xilinx Fellow Bill Carter, who was the eighth employee to be hired in the company in 1984 [24]. However, Ross never worried about this problem, due to Moore's Law. As the result, in 1985, Xilinx released the first FPGA, the XC2064 chip with 1000 gates. Remarkably, by the year 2004, the size of an FPGA has already exceeded ten thousand times this size [25].

As the size of FPGAs increased, schematic design entry became less practical. Evidently, once FPGAs reached a threshold of 100,000 gates, the idea of implementing and verifying the chips through schematic entry became impossible. Consequently, hardware description language (HDL) was introduced to the field. Although HDL was invented nearly three decades ago, due to the lack of synthesis tools, application of FPGAs were limited to simple chips. As the speed of the HDL simulators increased, FPGA design shifted swiftly to HDL design entry [25]. For a better understanding of FPGAs, the following sections will provide an in depth description of generic FPGA architecture.

# 2.2.2 FPGA Architecture

Although each FPGA has its own specific architecture, the general structure consists of configurable logic blocks, input-output (I/O) blocks and programmable interconnects. In addition, the structure should have circuitry to create a clock signal. Modern FPGAs can also include simple logic blocks such as ALUs, decoders, and memory [26]. According to Zeidman, there are three types of programmable elements in an FPGA: static RAM, anti fuses, and flash EPROM. In short, most of the FPGA structures are variations of the one shown in Figure 8 below [27].

Figure 8: Generic FPGA architecture

# 2.2.2.1 Configurable Logic Blocks (CLBs)

Most of the FPGA's logic is described in the configurable logic blocks. On average, one FPGA should have a logic circuitry intensive enough to create a state machine. Figure 9 shows an example of one simple configurable logic block [27]. As shown, CLBs are required to have some memory, like RAM, to create combinational logic functions and look up tables. They contain some flip flops to provide the block's logic memory for clock storage elements. In addition, CLBs also consist of multiplexers that help to route the logic within the block to communicate with external resources and to allow options such as reset, clear and input [26].

Figure 9: Configurable Logic Block (CLB)

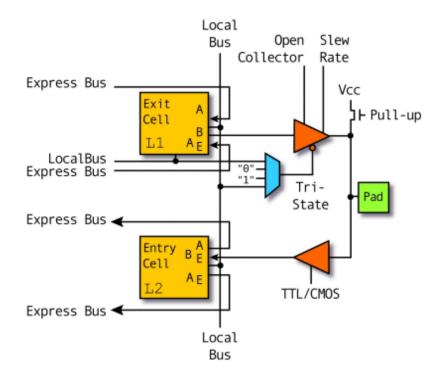

# 2.2.2.2 Configurable I/O Blocks

Configurable I/O Blocks are used to communicate with external sources apart from the FPGA. Specifically, the block brings signals to the chip and displays the output signal. Hence, I/O blocks usually contain buffers at both the input and output side (typically tri-state for output) and open collector control circuitry. The control circuit has some pull-up resistors and sometimes pull-down resistors to terminate signals as well as buses without discrete external resistors installed to the chip [26].

Designers have the option to select the output as active high or active low, depending on their needs. Moreover, FPGAs also allow designers to adjust the output's slew rate for fast or slow rise time or fall time. I/O blocks almost always have flip-flops on the output side so that the clocked signal can be outputted without delay, which helps to meet setup time requirements of other external devices. Similarly, the input sides also have some flip-flops to reduce hold time requirements of the FPGA [26]. Figure 10 below provides a simple example of the I/O blocks circuitry of an FPGA [27].

Figure 10: I/O Blocks Circuitry of a FPGA

# 2.2.2.3 Programmable Interconnects

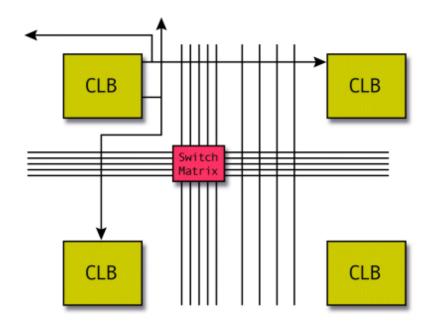

Another important component of an FPGA's structure is programmable interconnects. This component is used to connect CLBs on the chip. Figure 11 below shows a portion of a programmable interconnects network [27].

**Figure 11: Programmable Interconnects**

There are basically two types of interconnects: long lines and short lines. The long lines are used to connect CLBs that are physically far away from each other or are treated as buses within the chip. Specifically, three state buffers are used to connect CLBs with long lines to create buses. There are also special long wires, called global clock lines, which are used to connect clock buffers and clocked elements of each CLB block. These lines are designed to have low impedance for fast propagation times. This design is introduced to prevent skew between clocked signals within the chip. On the other hand, the short wires are simply used to connect closer CLBs [26].

In order to connect CLBs, connections are required to go through many transistors and switch matrices as shown in the figure above. As a result, in contrast to an ASIC where most delays come from the logic in the design, the majority of delay originates from programmable interconnects [26].

## 2.2.2.4 Clock Circuitry

The last major component of an FPGA is the clock circuitry. This circuit consists of special high drive clock buffers and clock drivers, which are distributed around the chip. The global clock lines are used to connect these drivers and clock input pads to distribute clock signals within the FPGA. Since skew and delay are not guaranteed anywhere except on these global clocked lines, FPGAs must be synchronous in design [26].

# 2.2.3 Advantages and Disadvantages of FPGAs

In 1984, Ross Freeman invented FPGA technology after being inspired to improve current ASIC technology [24]. Since then, FPGAs have become a promising technology that competes closely with ASICs. It is essential to understand the tradeoffs between these two technologies in order to make an appropriate choice in application.

Even though FPGA technology has become prominent in the semiconductor industry, it is still a new field with areas which require more investment. One of the drawbacks of FPGAs lies at its programmable interconnects component. Programmable interconnects rely on transistors or active buffers controlled by SRAM cells to work properly. These components add impedance into the route and make it impossible to estimate correct propagation delay [28]. For a logic designer, unknown delay can easily become disastrous, often consuming hours to debug. In addition, another disadvantage of FPGAs comes from the concept of the FPGA itself. As Xilinx stated in their "FPGA Embedded Processors – Revealing True System Performance" paper, design tools for FPGAs are complex because of the mixture of hardware and software platform design [29]. Moreover, most FPGA software design tools are immature and are difficult to use. In addition, device cost is also a consideration. Currently, most available processors on the market are less expensive than an equivalent embedded FPGA processor [29].

On the other hand, FPGAs have indeed proven to possess many advantages in the hardware design field. For example, FPGAs save great amounts of design time and cost compared to its ASIC counterpart. While the ASIC design process takes months to complete and one logical design flaw can result in a large expense to the vendor, FPGAs allow designers to change the logic and recompile in minutes with little effort, much like software [30]. Hence, FPGAs clearly allow engineers more options when solving a problem in the early stages of the design process and later adaptability by simply incorporating a specialized instruction set. Moreover, since each logic block, also called a processing element or PE, is designed to be as small as possible, FPGAs can maximize on-chip parallelism, which consequently increases processing time.

Another aspect that is worthwhile considering is an FPGA's architecture. For instance, the entire on chip logical resources can be used to maximize the packing density of one particular method. Thus, FPGAs do not require a predefined limit on the number of logic cells per chip [30]. In addition, because each algorithm is programmed during in-field use, each algorithm is separately optimized without on chip constraints arisen from other algorithms. As a result, FPGAs can process an algorithm as fast as one or two clock cycles. Designers can also control the chip clock rate independent of any logic designs, which provides more flexibility in approaching a problem.

When mentioning FPGAs, one cannot dismiss the abundant resources available for hardware designers. Many FPGA vendors have begun offering intellectual property (IP) cores which include special functions (this is discussed further in the next section). All IP cores are designed, verified, and characterized for specific tasks. One can always modify available cores by adding or subtracting functions based on need. Most IP cores are also provided by more than one vendor, which allows the programmer more choice. Perhaps most importantly, IP cores reduce the time and manpower required for FPGA design [26].

FPGAs are a powerful tool in computing that are used in many applications. It is important, however, to be aware of their limitations when making design decisions. Many tools exist to improve the FPGA design process, including several programming languages, which are discussed in the following section.

### 2.2.4 Available FPGA Programming Languages

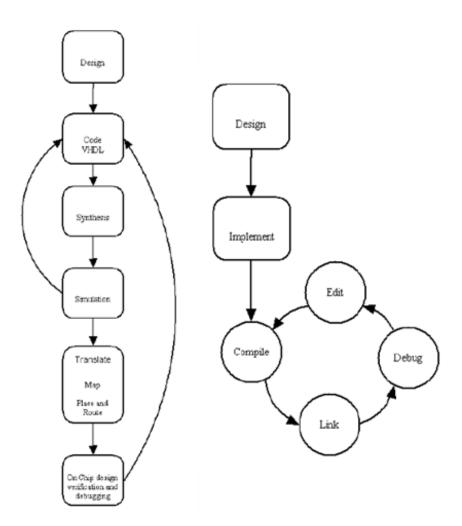

As mentioned earlier, FPGAs were originally designed by schematic design entry. However, as FPGA chip density increased exponentially, schematic design entry became less practical. Thus, hardware design languages (HDLs) came to play. The two traditional HDLs available are VHDL and Verilog.

The concept and design of these languages are completely different from the pipeline idea of most software programming languages. Figure 12 below provides a clear summary of the differences between the two language families. After designing and coding, HDLs must go through extra processes before implementation onto an FPGA. First, during the synthesis process, the code is translated into a schematic circuit, called a netlist. After synthesis, the HDL compiler will check if the design specified functions correctly in the simulation process. The netlist is then translated into binary form during the translation phase. Next, the mapping process defines the netlist connections and components into CLBs and then the device is modified to fit onto the target FPGA during the place and route phase [31].

Figure 12: Design Flow- Hardware (left) Software (Right)

# 2.2.4.1 VHDL

VHDL is one of the two traditional HDLs for FPGA programming. VHDL stands for VHSIC (Very-High-Speed-Integrated-Circuit) Hardware Design Language. VHDL was originally developed by the U.S. DoD in order to keep track of the behavior of ASIC equipment. In 1986, VHDL was transferred to the IEEE for regulation. From that time onward the IEEE standard for VHDL has been revised every five years [32]. This language is still largely used in government-related projects, but is a powerful tool in VHDL development.

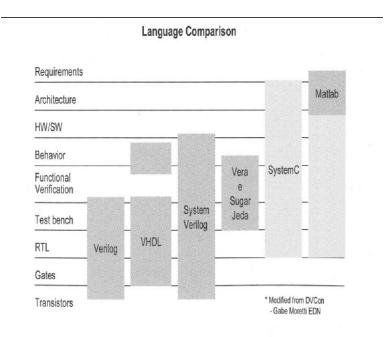

As an HDL, VHDL is used to describe electronic hardware at many levels of abstraction. Figure 13 below shows the summary of level of abstractions of some common languages [31]. From the figure, one can see that VHDL supports both low level abstraction, such as Register Transfer Level (RTLs) and Logic Gates, and relative high level abstraction, such as design behavior.

Figure 13: Level of Abstraction of different languages

According to Douglas J Smith in his report "HDL basic training: top-down chip design using Verilog and VHDL", VHDL can place procedures and functions in a package so that they are available for use by any other design. In addition, VHDL allows concurrent procedure calls. With VHDL, designers can use many languages or user defined data types, which is usually an advantage but can also be a drawback because of the need for careful conversion. VHDL also provides users with libraries, which act as storage in the host environment for entities, architectures, packages, and configurations. One can use libraries to manage multiple projects as well [33]. VHDL today is one of the two most common languages for FPGA design.

## 2.2.4.2 Verilog

Verilog is another highly successful HDL. According to "A brief history of Verilog" from Doulos Ltd., Verilog is rooted from a logic simulator, called Verilog-XL, which was created by Gateway Design Automation Company. In 1990, the language was transferred to public domain with the intention of turning Verilog into a standard HDL. Then in 1995, Verilog was introduced to the IEEE for standardization and, like VHDL, has since been revised every five years [34]. Recently, Accelera, a nonprofit organization, which was formed to maintain Verilog with the IEEE, has introduced an extended version of Verilog, named Systemverilog. As can be seen in Figure 13, Verilog can only support low level abstraction design like RTLs and Logic Gates [31]. However, Systemverilog provides a wider range than VHDL which allows behavioral and functional verification levels.

Verilog is mostly used in commercial applications, unlike VHDL, which is mostly used in the government. This is likely because it was based on the C programming language, which is widely used, whereas VHDL was based on Ada, a military programming language. In addition, Verilog data types are simpler and easier to use. Verilog clearly defines net data types, such as wires and register data types. Secondly, while VHDL is a strong type language, meaning the types of variables are emphasized, Verilog is a PL/I language, which is block oriented. PLI serves as an interface between Verilog models and other languages or Verilog software tools. Both Verilog and VHDL have their place within the FPGA design community. While VHDL is common in government contracts, Verilog is widely applied in the commercial world [33].

# 2.2.4.3 High Level Languages for FPGA Programming

Due to the parallel nature of HDL, (in contrast to the pipeline tradition of software languages) computer science engineers often find it difficult to implement designs on FPGAs. This limitation can confine FPGA development and productivity. In addition, the need for a solid link between software and hardware increases as FPGA technology grows. Various attempts have been made to achieve this goal; consequently, Electronic System Level (ESL) tools have been developed. Most noticeable successes are Systemverilog and SystemC. Figure 13 above shows that both languages can support a relatively high level of abstraction, such as behavioral and functional verification. SystemC specifically provides the designer with options between hardware/software or architecture level descriptions.

SystemC is a C++ library used for supporting system level modeling. Its libraries are designed to work with C++ to understand the concept of time, delay and concurrent processes. SystemC can also understand signals, ports and hardware data types like bit and fixed point. Along with SystemC, Systemverilog is an HDL with extensive verification capabilities. With Systemverilog, designers can experience more high level options such as design description, functional simulation, and property specification [35].

One additional high level software language for designing FPGAs is named Impulse C. Impulse C and Impulse CoDeveloper tools are used to bring the familiar C language to FPGA based programmable platforms [36]. This software allows computer science engineers and hardware engineers to describe and accelerate parallel algorithms using standard C language. Software programmers can use the automated compiler features of Impulse C and its stream oriented programming methods to design applications without giving low level hardware descriptions. Figure 14 below provides a programming flow for hardware design using Impulse C [36]. As stated by its developer, Impulse C is not meant to replace HDL for logic design purposes but rather for expressing C algorithms in an FPGA.

Figure 14: Hardware designing with Impulse C

FPGAs can be difficult to program due to their parallel nature. Several languages, from VHDL and Verilog to higher level languages like SystemC and Impulse C have been developed to make the development process easier.

# 2.3 IEEE754 Floating point standard

The IEEE754 standard lays out the convention for representing floating point numbers. Before this standard was developed, each platform developed its own method for utilizing floating point numbers. In the following sections we describe the standard in detail, including its precise representation in a binary computer. We then outline some special cases and important considerations when using this standard. Finally, we discuss floating point math, both in general and using the IEEE standard. This information will lend us insight into the computational methods involved in implementing floating point arithmetic.

# 2.3.1 Importance and History of IEEE754 Floating Point Standard

Most modern computers and calculators have a high degree of accuracy and speed. Users expect consistent and accurate answers for every calculation made on every system. The IEEE754 floating point standard is credited for maintaining consistency in computing today. One can only imagine how disastrous computations would be without standards. Before 1985 different microprocessors would provide different mathematical results. Even with today's set of standards, one minor floating point standard mistake can cause considerable damage. For example, in June 1996 a satellite rocket named Ariane 5 worth over half of a billion dollars crashed into the ground. According to Professor William Kahan, the programming language that designed Ariane 5 ignored the default exception handling specifications in IEEE754. As a result, the control system misinterpreted corrective actions and the rocket's motors exceeded their limits of mounting [37]. Had the overflow standards been followed, the software would have set a flag, delivered an invalid result, which then would have been ignored.

Before the IEEE754 standard, each manufacturer devised their own floating point rules and thus, had their own range and accuracy. Confusion occurred often from one microprocessor to another. For example, one computer can treat a value as non zero for addition and comparisons but as a zero for division and multiplication [37]. The computers, languages, compilers, and algorithms were so varied that simple joint projects would have been nearly impossible.

In 1976, Intel started its own internal arithmetic standard and hired Professor Kahan as a consultant [37]. With Intel, Professor Kahan integrated the best available floating point methods into the i8087' ROM. As the result, in 1985, the IEEE754 standard for Binary Floating Point Arithmetic was finally developed after a decade long effort [37]. Like all other IEEE standards, IEEE754 also needed revision after a certain amount of time. Fifteen years was chosen for IEEE754. This standard has been especially important with the dramatic improvements in microprocessors in recent years. Although the standards have been a great success, it is important to understand that the policies do not provide the "right" answer but rather a consistent one.

#### 2.3.2 Definition and Standard Convention

The following sections describe the IEEE floating point standard in detail. This includes the general representation convention and some special cases that need to be considered. We then discuss issues with floating point operations and mathematical methods.

# 2.3.2.1 Definition

This section provides a specific definition and explanation for the IEEE754 floating point standard. There are several ways to represent real numbers on computers. Fixed point format places a radix point somewhere in the middle of the digits and is equivalent to using integers to express portions of some unit. A rational represents any value as a ratio of two numbers. Floating point, the most common representation, represents real numbers in scientific notation, which describes a value as a base number and an exponent. According to Steve Hollasch, since fixed point format has a limited window of representation, it cannot express a very high or very small value. Moreover, fixed point format loses precision while doing division. Floating point format, on the other hand, has a wider window of representation and loses less precision during division and thus has become more common [38].

After multiple revisions, the IEEE separated floating point into four main categories, single precision (32 bits), single extended precision (minimum 44 bits, including one hidden bit), double precision (64 bits), and double extended precision (minimum 80 bits, including one hidden bit) [39]. Besides these 4 main categories, modern microprocessors also support some advanced floating point expressions, such as single precision and double precision for complex numbers. Extended formats were introduced for extra precision and exponent range.

IEEE floating point numbers have three main components: the sign, the exponent, and the mantissa, which is also known as a significand.

- The sign bit is always the most significant bit (MSB), or the furthest left bit and describes positive numbers with a 0 and negative with a 1.

- The exponent needs to represent both negative and positive numbers. IEEE754 uses a biased representation to express the exponent of a floating point number. In a case of a single precision number, the exponent has 8 bits, thus the bias is 127 (or 16 bits with a bias of 1023 for double precision). Thus, an exponent of 0 would be described as 127 in the exponent field. A stored value of 300 would indicate 173, because 127 subtracted from 300 results in 173. Two special cases are -127 and +128 which are reserved for special numbers which will be discussed later on.

32

• The mantissa represents the precision bits of the number. The mantissa consists of a hidden bit and the fraction bits.

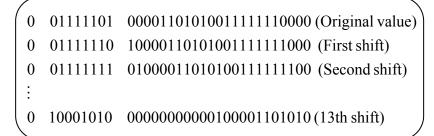

It is important to note that the base of the exponent in IEEE754 is always two. Typically during floating point arithmetic, shifting is necessary; however, the performance gained from using a larger base (which would require less shifting) is relatively small. There is therefore little gain in using a higher base. Another standardization decision of note is the hidden bit. Since binary numbers can always be represented starting with a 1 (e.g. 0100 is the same as 100), the expression can be normalized, removing any preceding zeros. Thus, we can assume there is a 1 and save one bit of storage. That format is said to use a hidden bit [39]. Overall IEEE754 states that single precision uses one sign bit, eight exponent bits and 23 bits for the significand. However, when the hidden bit is included, the significand is actually 24 bits, even though it is only encoded as 23.

Table 5 below displays a summary of floating point representation [39]. Note that even though single extended and double extended format only show a minimum 43 or 79 bits, they actually represent 44 and 80 bits, respectively, because of the hidden bit format.

| Parameter              | Format |          |        |          |

|------------------------|--------|----------|--------|----------|

|                        | Single | Single   | Double | Double-  |

|                        |        | extended |        | extended |

| Mantissa , p           | 24     | ≥ 32     | 53     | ≥ 64     |

| Max unbiased exponent, | +127   | ≥1023    | +1023  | >16383   |

| θmax                   |        |          |        |          |

| Min unbiased exponent, | -126   | ≤ -1022  | -1022  | ≤ -16382 |

| θmin                   |        |          |        |          |

| Exponent width (bits)  | 8      | ≤ 11     | 11     | ≥ 15     |

| Format width (bits)    | 32     | ≥ 43     | 64     | ≥ 79     |

**Table 5: Summary of Floating Point Representation**

## 2.3.2.2 Normalized and Denormalized Numbers

While discussing the mantissa in the previous section, the definition of binary normalized floating point numbers was introduced. Essentially, if the leading digit of the significand is nonzero, then the representation is normalized. Denormalized numbers, however, can also be used. Denormalized numbers were introduced to the floating point standard to fill in the gap between 0 and the smallest value a normalized floating point number can express. Using the binary single precision floating point representation, the smallest normalized value would be 2<sup>-126</sup>. Denormalized numbers play an important role when dealing with extremely small calculation results. Essentially, using normalized numbers, any real number smaller than 2<sup>-126</sup> would "flush into 0", which would cause large relative error for normalized number calculations [39]. IEEE754 floating point standards define denormalized numbers as the following: when the exponent bits are all 0s, but the fraction and the leading bit of the mantissa are non-zero, then the value is a denormalized number [38].

Since binary floating point standards always assume that the hidden bit is 1, a floating point number with an exponent of  $\theta_{min}$  will always have a mantissa that is greater than 1. Therefore, for consistency, the IEEE chose to keep the same exponent value (in the representation) for any floating point numbers with the exponent that is larger than  $\theta_{min} - 1$ . In the event that the exponent is equal to  $\theta_{min}$ -1, the denormalized numbers, which are smaller than 1 but larger than 0, will be represented as  $0.b_1b_2b_3b_4b_5b_6 \ge 2^{\theta min+1}$ . The additional one is needed because the denormalized numbers have an exponent of  $\theta_{min}$  not  $\theta_{min} - 1$ .

A detailed example of this concept is the representation of 0.75 in binary floating point. In fixed point binary, this number would be represented as 0.11. In order to represent this as a floating point, we would need to shift the decimal point to the right, which results in  $1.1x2^{-1}$ . Using the rules we have learned so far from IEEE754, we would then represent this number in the following way. The mantissa, in this case would need to be 10..0 and the exponent would need to be -1 (or -128 after the bias); however -128 cannot be represented using 8 bits. Therefore, we need a new method of representation. This is where the concept of denormalized numbers is important, which applies the range of numbers from -1 (non-inclusive) to near zero on the negative side and from near zero on the positive side to 1 (non-inclusive), or mathematically: (-1,0) and (0,1). This representation however limits precision for very small numbers near zero. In our example, 0.75 would be represented: exponent = 00..00, mantissa = 10..00. Since the exponent is 00..00, it is recognized as a denormalized number and so only the mantissa is looked at, which in this case is 10..00, or with the hidden bit included and decimal point added: 1.100..00.

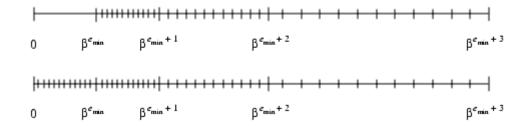

Figure 15 illustrates the range of denormalized numbers [39]. The figure also introduces the concept of gradual underflow. When the result of a calculation becomes too small for normalized numbers and is expressed as denormalized, the behavior is called "gradual underflow". On the other hand, if that result is simply rounded to 0, the behavior is called "flush to zero".

Figure 15: Flush to Zero (above) and Gradual Underflow (below)

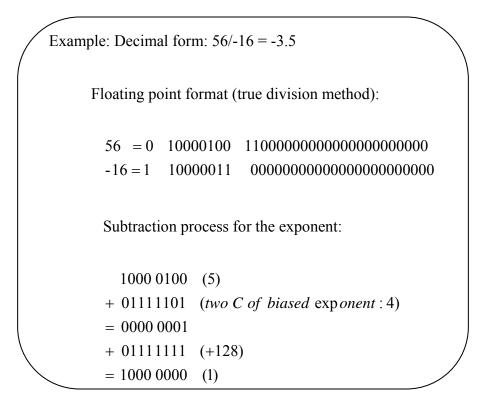

# 2.3.2.3 Precision and Range of Floating Point Numbers