# **Understanding and Countermeasures against IoT Physical Side Channel Leakage**

by

Michael Moukarzel

A Dissertation

Submitted to the Faculty

of the

#### WORCESTER POLYTECHNIC INSTITUTE

In partial fulfillment of the requirements for the

Degree of Doctor of Philosophy

in

Electrical and Computer Engineering

by

15 May 2019

APPROVED:

Professor Thomas Eisenbarth

**Dissertation Committee**

Institute for IT Security

University of Lübeck

Professor Reinhold Ludwig

Head of Department

**ECE** Department

Worcester Polytechnic Institute

Assistant Professor Matthew Hicks

Dissertation Committee

CS Department

Virginia Tech

Professor Berk Sunar Dissertation Advisor

ECE Department

Worcester Polytechnic Institute

#### **Abstract**

With the proliferation of cheap bulk SSD storage and better batteries in the last few years we are experiencing an explosion in the number of Internet of Things (IoT) devices flooding the market, smartphone connected point-of-sale devices (e.g. Square), home monitoring devices (e.g. NEST), fitness monitoring devices (e.g. Fitbit), and smartwatches. With new IoT devices come new security threats that have yet to be adequately evaluated.

We propose μLeech, a new embedded trusted platform module for next-generation power scavenging devices. Such power scavenging devices are already widely deployed. For instance, the Square point-of-sale reader uses the microphone/speaker interface of a smartphone for communications and as a power supply. Such devices are being used as trusted devices in security-critical applications, without having been adequately evaluated. μLeech can securely store keys and provide cryptographic services to any connected smartphone. Our design also facilitates physical side-channel security analysis by providing interfaces to facilitate the acquisition of power traces and clock manipulation attacks. Thus μLeech empowers security researchers to analyze leakage in next-generation embedded and IoT devices and to evaluate countermeasures before deployment.

Even the most secure systems reveal their secrets through secret-dependent computation. Secret-dependent computation is detectable by monitoring a system's time, power, or outputs. Common defenses to side-channel emanations include adding noise to the channel or making algorithmic changes to mitigate specific side-channels. Unfortunately, existing solutions are not automatic, not comprehensive, or not practical.

We propose an isolation-based approach for eliminating power and timing side-channels that is automatic, comprehensive, and practical. Our approach eliminates side-channels by leveraging integrated decoupling capacitors to electrically isolate trusted computation from the adversary. Software has the ability to request a fixed-power/time quantum of

isolated computation. By discretizing power and time, our approach controls the granularity of side-channel leakage; the only burden on programmers is to ensure that all secret-dependent execution differences converge within a power/time quantum.

We design and implement three approaches to power/time-based quantization and isolation: a wholly-digital version, a hybrid version that uses *capacitors for time tracking*, and a full-custom version. We evaluate the overheads of our proposed controllers with respect to software implementations of AES and RSA running on an ARM-based microcontroller and hardware implementations AES and RSA using a 22nm process technology. We also validate the effectiveness and real-world efficiency of our approach by building a prototype consisting of an ARM microcontroller, an FPGA, and discrete circuit components.

Lastly, we examine the root cause of Electromagnetic (EM) side-channel attacks on Integrated Circuits (ICs) to augment the Quantized Computing design to mitigate EM leakage. By leveraging the isolation nature of our Quantized Computing design, we can effectively reduce the length and power of the unintended EM antennas created by the wire layers in an IC.

#### Acknowledgements

I would like to take this opportunity to offer my sincere gratitude to those who have made this work possible and who have provided support and guidance for my efforts. First, Profs. Berk Sunar and Thomas Eisenbarth for their time, effort, and advise that they have given me as my thesis advisers at WPI. The examples that they have set for me will remain influential for the remainders of my professional and personal life.

All my colleagues in the Vernam lab thank you for the friendships, memories, and heated discussions. With a special thanks to my lab mates and friends Yarkin Doroz, Wei Dai, and Gorka Irazoqui. I could not imagine completing this journey without there friendship and support.

Kevin Bush, Associate Group Leader at MIT Lincoln Labs, for his continued support and mentoring during both my internships and graduate studies. This thesis would not have been possible if not for the contacts, funding, and research opportunities afforded during my work with Kevin.

Prof. Matthew Hicks, Assistant Professor at Virginia Tech, for his friendship, advise, and mentoring during my graduate studies. He was instrumental in evolving my thinking process to a higher level. The lessons I have learned as part of his research group will remain influential for the remainder of my professional and personal life. He is a true friend and mentor.

My parents, Anthony and Nadia Moukarzel, and my sisters, Yasmina and Lea and Moukarzel, who have never stopped pushing, encouraging, and motivating me in my personal and academic development. Their continued love and support will aid me in all my future endeavors.

To all of you my sincere gratitude!

Michael Moukarzel

# **Contents**

| 1 | Intr | oductio | on .                                     |     | 1 |

|---|------|---------|------------------------------------------|-----|---|

|   | 1.1  | Backg   | ground                                   |     | 2 |

|   | 1.2  | Proble  | em Statement                             |     | 4 |

|   | 1.3  | Summ    | nary of Contributions                    |     | 5 |

|   | 1.4  | Disser  | rtation Outline                          |     | 6 |

| 2 | μLe  | ech: A  | Side-Channel Evaluation Platform for IoT | :   | 8 |

|   | 2.1  | Side-C  | Channel Evaluation Platforms             |     | 9 |

|   | 2.2  | Overv   | iew of the Design                        | . 1 | 1 |

|   |      | 2.2.1   | Power Siphoning                          | . 1 | 2 |

|   |      | 2.2.2   | Capacitor Bank                           | . 1 | 4 |

|   |      | 2.2.3   | Sleep Mode                               | . 1 | 5 |

|   |      | 2.2.4   | Side-Channel Platform                    | . 1 | 6 |

|   | 2.3  | Data C  | Communication                            | . 1 | 7 |

|   |      | 2.3.1   | Manchester Encoding                      | . 1 | 9 |

|   |      | 2.3.2   | Transmit                                 | . 2 | 0 |

|   |      | 2.3.3   | Receive                                  | . 2 | 3 |

|   | 2.4  | Impler  | mentation Results                        | . 2 | 6 |

|   |      | 2.4.1   | Sleep Mode                               | . 2 | 6 |

|   |      | 2.4.2   | Active Mode                                               | 27 |

|---|------|---------|-----------------------------------------------------------|----|

|   |      | 2.4.3   | 128-bit AES                                               | 28 |

|   | 2.5  | Conclu  | asion                                                     | 28 |

| 3 | Qua  | ntized  | Computing: On-demand Isolation as a Power and Timing Side | -  |

|   | char | nnel De | fense                                                     | 29 |

|   | 3.1  | Backg   | round                                                     | 32 |

|   |      | 3.1.1   | Decoupling Capacitors                                     | 34 |

|   | 3.2  | Threat  | Model                                                     | 35 |

|   | 3.3  | Quanti  | ization Controller Design                                 | 36 |

|   |      | 3.3.1   | Isolation Controller                                      | 36 |

|   |      | 3.3.2   | Timing Controller                                         | 37 |

|   |      | 3.3.3   | Power Controller                                          | 38 |

|   |      | 3.3.4   | Fault Attacks                                             | 39 |

|   |      | 3.3.5   | End-to-end Flow                                           | 42 |

|   |      | 3.3.6   | Illustrative Example                                      | 43 |

|   | 3.4  | Quanti  | ization Controller Implementation                         | 44 |

|   |      | 3.4.1   | Wholly Digital Implementation                             | 45 |

|   |      | 3.4.2   | Analog Implementation                                     | 46 |

|   |      | 3.4.3   | Hybrid Implementation                                     | 49 |

|   | 3.5  | Selecti | ing a Crypto Core                                         | 49 |

|   |      | 3.5.1   | Capacitor Bank                                            | 50 |

|   |      | 3.5.2   | Preliminaries                                             | 51 |

|   |      | 3.5.3   | Computation Effects                                       | 52 |

|   |      | 3.5.4   | Memory Effects                                            | 56 |

|   |      | 3.5.5   | Analysis and Recommendations                              | 59 |

|   | 3.6  | Selecting a Microcontroller Configuration |

|---|------|-------------------------------------------|

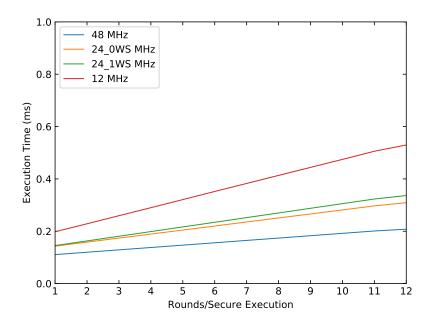

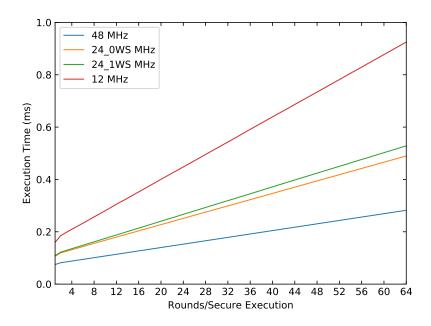

|   |      | 3.6.1 Computation Time ( $\Delta t$ ) 61  |

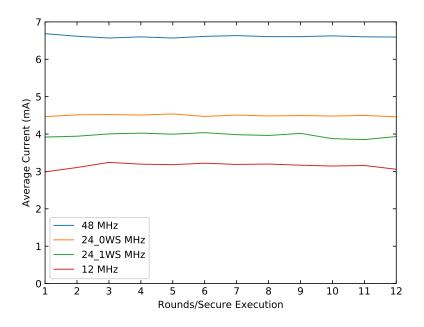

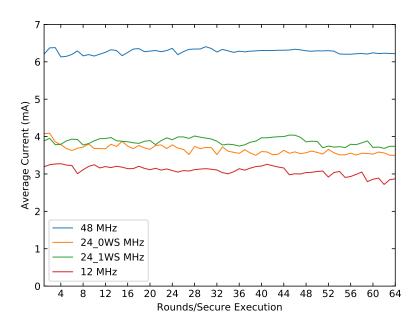

|   |      | 3.6.2 Average Current ( <i>I</i> )        |

|   |      | 3.6.3 Capacitor Size                      |

|   |      | 3.6.4 System Verification                 |

|   |      | 3.6.5 Software Overhead                   |

|   | 3.7  | Discussion                                |

|   | 3.8  | Related Work                              |

|   | 3.9  | Conclusion                                |

| 4 | Опа  | ntized Computing:                         |

| • |      | romagnetic Augmentation 71                |

|   |      |                                           |

|   | 4.1  | EM Leakage: Near-Field Radiation          |

|   | 4.2  | EM Leakage: Wire Layers                   |

|   |      | 4.2.1 Metal Layer: Modeling               |

|   | 4.3  | Metal Layer: Simulating EM-Fields         |

|   | 4.4  | Threat Model                              |

|   | 4.5  | Design                                    |

|   | 4.6  | Discussion                                |

|   | 4.7  | Conclusion                                |

| 5 | Cone | lusion 87                                 |

|   |      | 5.0.1 Summary of Results                  |

|   |      | 5.0.2 Recommendations for Future Work 90  |

# **List of Figures**

| 2.1  | Nexus 4 headset jack available power | 11 |

|------|--------------------------------------|----|

| 2.2  | Power Circuit                        | 13 |

| 2.3  | Power Circuit Analysis               | 13 |

| 2.4  | Sleep Circuit.                       | 15 |

| 2.5  | $\mu$ Leech Evaluation Board         | 17 |

| 2.6  | $\mu$ Leech Execution Cycle          | 18 |

| 2.7  | Manchester Encoding of header 0xDD   | 21 |

| 2.8  | Manchester Encoding of length 0x0A   | 21 |

| 2.9  | Manchester Encoding of data 0xFF     | 21 |

| 2.10 | Manchester Encoding of data $0x00$   | 21 |

| 2.11 | $\mu$ Leech Transmit Flow Chart      | 22 |

| 2.12 | $\mu$ Leech Transmit Circuit         | 22 |

| 2.13 | $\mu$ Leech Transmission - Zoomed in | 23 |

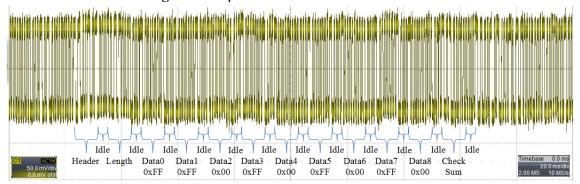

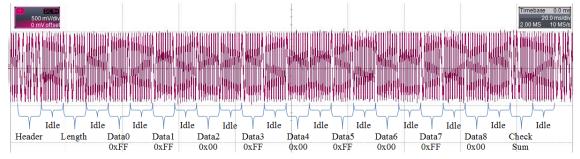

| 2.14 | $\mu$ Leech Transmission             | 23 |

| 2.15 | $\mu$ Leech Receive Flow Chart       | 24 |

| 2.16 | $\mu$ Leech Receive Circuit          | 24 |

| 2.17 | Smartphone Transmission - Zoomed in  | 25 |

| 2.18 | Smartphone Transmission              | 25 |

| 3 1  | Quantized Computing system overview  | 30 |

| 3.2  | Illustrative of the Quantization Controller's effectiveness against power  |    |  |  |  |  |  |  |  |

|------|----------------------------------------------------------------------------|----|--|--|--|--|--|--|--|

|      | and timing side-channels for RSA. Note that the noise/variation is hard to |    |  |  |  |  |  |  |  |

|      | see due to scaling                                                         | 43 |  |  |  |  |  |  |  |

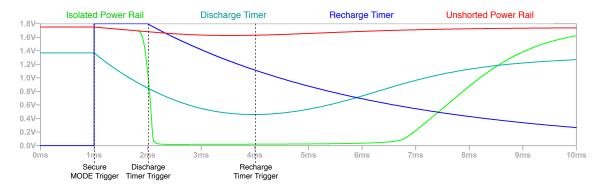

| 3.3  | RTL simulation of the wholly digital and hybrid versions                   | 45 |  |  |  |  |  |  |  |

| 3.4  | Full-custom analog Quantization Controller circuit                         | 46 |  |  |  |  |  |  |  |

| 3.5  | SPICE simulation of the full-custom analog version                         | 47 |  |  |  |  |  |  |  |

| 3.6  | SPICE simulation of the analog parts of the hybrid version                 | 48 |  |  |  |  |  |  |  |

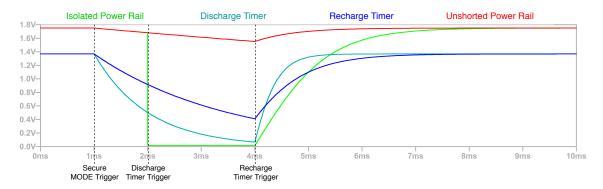

| 3.7  | Time required to write to Flash and FRAM                                   | 58 |  |  |  |  |  |  |  |

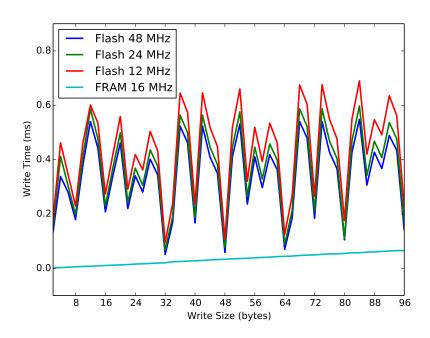

| 3.8  | Quantization Controller MSP432 prototype                                   | 60 |  |  |  |  |  |  |  |

| 3.9  | Computation time for AES                                                   | 62 |  |  |  |  |  |  |  |

| 3.10 | Computation time for RSA                                                   | 62 |  |  |  |  |  |  |  |

| 3.11 | Average current for AES                                                    | 64 |  |  |  |  |  |  |  |

| 3.12 | Average current for RSA                                                    | 64 |  |  |  |  |  |  |  |

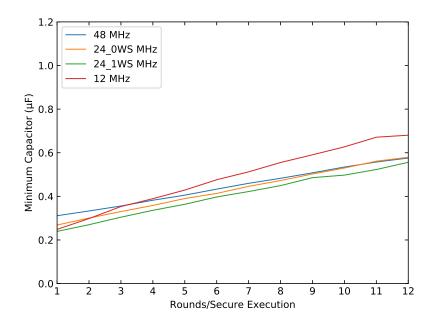

| 3.13 | Required capacitor size for AES                                            | 66 |  |  |  |  |  |  |  |

| 3.14 | Required capacitor size for RSA                                            | 66 |  |  |  |  |  |  |  |

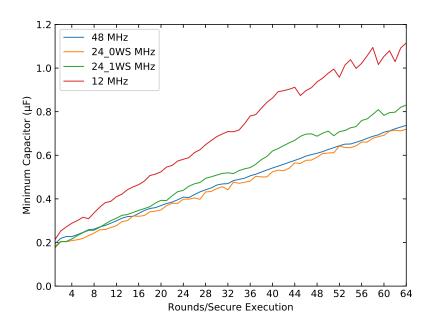

| 3.15 | Software run time overhead across a range of secure execution invocaton    |    |  |  |  |  |  |  |  |

|      | rates                                                                      | 67 |  |  |  |  |  |  |  |

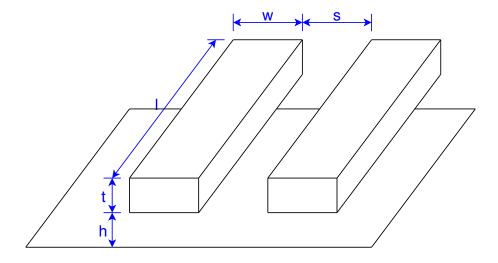

| 4.1  | Wire Layer Geometry.                                                       | 79 |  |  |  |  |  |  |  |

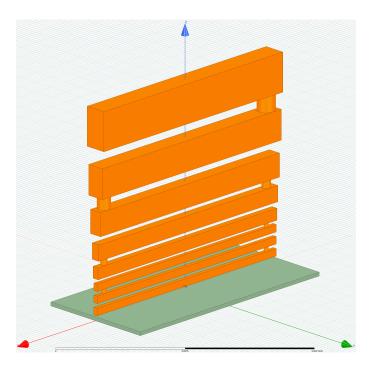

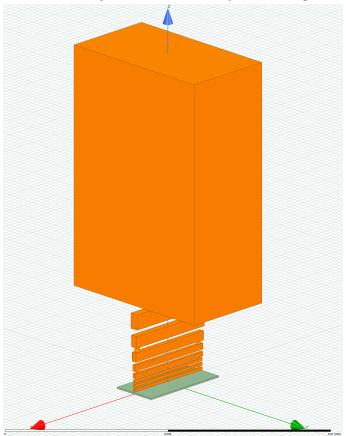

| 4.2  | HFSS model of Intel 32nm Metal Layer - exluding Metal Layer 9              | 80 |  |  |  |  |  |  |  |

| 4.3  | HFSS model of Intel 32nm Metal Layer                                       | 80 |  |  |  |  |  |  |  |

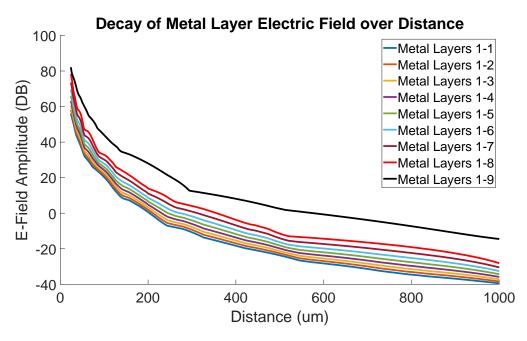

| 4.4  | Metal Layer E-Field decay over distance                                    | 82 |  |  |  |  |  |  |  |

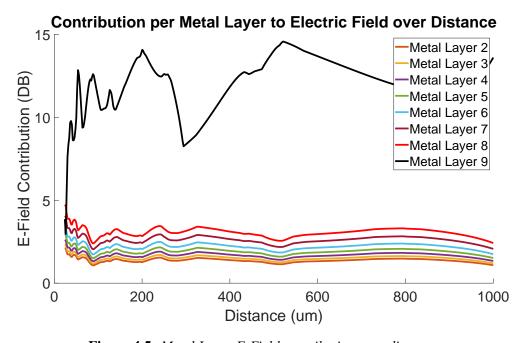

| 15   | Metal Laver E-Field contribution over distance                             | 87 |  |  |  |  |  |  |  |

# **List of Tables**

| 2.1 | Smartphone Transmission Burst                                           | 23 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | Smartphone Transmission Burst                                           | 25 |

| 2.3 | $\mu$ Leech Power Consumption                                           | 27 |

| 3.1 | Tradeoff space of the three Quantization Controller implementations us- |    |

|     | ing a 22nm process technology                                           | 45 |

| 3.2 | Summary of key properties of the processors evaluated                   | 53 |

| 4.1 | Pitch(nm)                                                               | 76 |

| 4.2 | Thickness(nm)                                                           | 76 |

| 4.3 | Aspect Ratio                                                            | 76 |

| 4.4 | Pitch(%) difference to Metal 1                                          | 77 |

| 4.5 | Thickness(%) difference to Metal 1                                      | 77 |

| 4.6 | Aspect Ratio(%) difference to Metal 1                                   | 77 |

## Chapter 1

### Introduction

With the proliferation of cheap bulk SSD storage and better batteries in the last few years we are experiencing an explosion in the number of Internet of Things (IoT) devices flooding the market, smartphone connected point-of-sale devices (e.g. Square), home monitoring devices (e.g. NEST), fitness monitoring devices (e.g. Fitbit), and smart-watches [1]. With new IoT devices come new security threats that have yet to be properly evaluated [2].

The Square point-of-sale unit, in particular, has gained traction in the market. The versatility and convenience of the design have propelled the product into widespread adoption. What makes the Square design unique is that it uses the microphone/speaker interface to power the unit as well as to facilitate the communication between the device and the smartphone. Since speaker/microphone is the only universal interface present in all smartphones the Square device is transparently interchangeable from one smartphone to the other.

The Square point-of-sale unit iterated through three edition, due to security threats [3]. The first version was susceptible to man in the middle attacks as all communication between the Square and smartphone was not encrypted [4]. To address this there next iteration implemented encrypted communication at the cost of power, requiring an internal

coin cell battery [4]. Their third edition addresses both encryption and power requirements with a customized copyrighted low power IC [4]. These version iterations were dictated by security vulnerabilities that were overlooked and compromised the intended objective of the device, i.e. secure transactions.

The focuses of this thesis are the security threat presented by physical side-channel leakage of IoTs such as the Square point-of-sale. To that end, we design and evaluate power and timing side-channel leakage of µLeech. µLeech is a custom IoT device modeled off of the Square point-of-sale that acts as a universal power scavenging Trusted Platform Module (TPM) for smartphones. We augment µLeech to serve as a side-channel evaluation platform to evaluate side-channel leakage present in lower power scavenging IoT devices. In the course of our evaluation, we propose a new countermeasure centered around isolation. Our Quantization Controller design leverages power scavenging techniques to isolate power leakage during secure execution to create uniform power and timing footprints. We augment our countermeasure to include defenses against thermal, power glitching, memory fault, and EM attacks.

### 1.1 Background

All computing devices generate side-channel emanations as a byproduct of physical implementation and computation [5]. The key to side-channel analysis is the interpretation of these leaks to reveal secrets. As such, there are many different side-channel leaks used to capture secrets. These include: power [6], timing [7], electromagnetic [8], acoustic [9], memory remanence [10], and thermal [11]. The two most commonly exploited side-channels in literature are power and timing [12]. The popularity of these two side-channels is due to the high bit rate and fine-grain (e.g., per clock cycle) information that they expose to the attacker. To gain access to this wealth of secret-revealing information,

an attacker only needs to be able to measure the current consumed by the victim device.

Side-channel countermeasures focus on reducing the signal-to-noise ratio (SNR). Techniques such as noise introduction and incorporating randomness focus on raising the noise threshold [13]. Thereby making it challenging to differentiate between the leaked signal and random noise. On the other hand techniques such as leakage reduction and obfuscation aim to reduce the leaking signal strength within the noise threshold [13]. By reducing the SNR, any countermeasure can increase the difficulty of filtering out the leaking signal from the noise level. However, the real trick with any countermeasure is to not push leakage from one channel to another, as there is a symbiotic relationship between the different side-channels:

- Power vs. Timing: Implementing any limitations on a power rail would directly correlate to any variability in execution performance. Therefore a leakage hidden on the Power rail would be exposed through timing analysis.

- **Timing vs. Power**: Implementing any timing limitations to hide execution would directly translate into power consumption. Executions that obfuscate leakage by forcing constant execution times would leak variable power draw.

- Timing vs. Fault: Implementing counters to conceal timing differences creates

opportunities for fault attacks that invert the expected ordering of system events.

Temperature-based fault attacks affect the rate of leakage of a capacitor while not

effecting digital counters.

- Power vs. Electromagnetic: Hiding the power capacitor recharge side-channel requires shorting the capacitor's voltage down to a fixed level. This creates a large current spike visible in the electromagnetic spectrum. The magnitude of this current spike indicates how much current was on the power capacitor after secure execution, thus revealing secret information.

Without care, eliminating the leak from one side-channel shifts the information to another channel. A complete solution would have to addresses these threats in unison.

### 1.2 Problem Statement

Accompanying the recent explosion of smartphones and tablets is a growing trend for new IoTs that can interface with those devices. These IoTs are designed with the express purpose of being small, easy to use, and convenient. Unfortunately, in many cases, IoTs are deployed as trusted devices in security critical applications before they have been properly evaluated. For the purposed of this work, we are interested in the physical side-channel leakage of such IoTs. While side-channel attacks have been extensively researched the effect of secure executions on such low power, embedded, and highly connected devices have not been properly evaluated. IoTs perform low power intermittent execution using energy harvesting inputs. As such IoTs have drastically different electrical characteristics that need to be properly evaluated for side-channel vulnerabilities.

Our threat model assumes an attacker with knowledge of the software running on as well as with full physical access to the IoT. The attacker's objective is to extract secret information through non-destructive, non-invasive, timing and power side-channel analysis. We assume that the attacker can also control the power supplied to the device as well as its environment to induce power and thermal faults.

We develop a custom low power IoT used for intermittent secure execution to observe any side-channel leakage, using a customized side-channel evaluation platform. In the course of our evaluation, we propose a new countermeasure centered around isolation. Our proposed design focuses on reducing the signal by leveraging power scavenging techniques to isolate power leakage during secure execution and creating uniform power and timing footprints. Following these observations, we develop and augment a compre-

hensive and mostly automatic power and timing side-channel defense that is immune to thermal and power fault attacks.

### 1.3 Summary of Contributions

- $\bullet$  Designing a custom IoT device,  $\mu$ Leech, that can mimic existing IoT communication protocols, power scavenging features, intermittent execution, and security-critical applications.

- Developed and optimized µLeech as a low power TPM module for smartphones

- Designing a side-channel evaluation platform of  $\mu$ Leech to facilitate the acquisition of physical side-channel leakage.

- Designing a countermeasure by leveraging energy harvesting techniques to isolate power and timing side-channel leakage.

- Augmenting our countermeasure to protect against temperature, fault, and powerglitching attacks.

- Prototype our countermeasure to test for side-channel leakage under real-world conditions

- Evaluating the source of electromagnetic side-channel leakage from ICs

- Modeling the primary source of electromagnetic side-channel leakage from ICs

- Extending the proposed countermeasure to reduce electromagnetic side-channel leakage

### 1.4 Dissertation Outline

- Chapter 2 describes the design of μLeech a new embedded TPM for IoTs and its development as a side-channel evaluation platform. μLeech can mimic the communication protocols, power scavenging effects, and cryptographic executions of other IoTs. While such devices are used as trusted devices in security critical applications, they have not been properly evaluated yet. μLeech can securely store keys and provide cryptographic services to any connected smartphone. Our design facilitates physical side-channel security analysis by providing interfaces to enable easier acquisition of power traces and clock manipulation attacks. Thus μLeech empowers security researchers to analyze leakage in next generation embedded and IoT devices and to evaluate countermeasures before deployment.

- Chapter 3 presents Quantization Controller, a side-channel isolation countermeasure that creates uniform power and timing side-channel footprints while protecting against temperature, fault, and power glitching attacks. Our design leverages integrated decoupling capacitors to electrically isolate trusted computation from the adversary. Software has the ability to request a fixed-power/time quantum of isolated computation. By discretizing power and time, our approach controls the granularity of side-channel leakage; the only burden on programmers is to ensure that all secret-dependent execution differences converge within a power/time quantum. We design and implement three approaches to power/time-based quantization and isolation: a wholly-digital version, a hybrid version that uses *capacitors for time tracking*, and a full-custom version. These designs are evaluated with respect to software implementations of AES and RSA running on an ARM-based microcontroller and hardware implementations of AES and RSA using a 22nm process technology. We also validate the effectiveness and real-world efficiency of our ap-

proach by building a prototype consisting of an ARM microcontroller, an FPGA, and discrete circuit components.

- Chapter 4 examines the root cause of Electromagnetic (EM) side-channel attacks on Integrated Circuits (ICs) to augment the Quantization Controller design to mitigate EM leakage. EM attacks on ICs design have long followed a black box approach. We identify and examine the root cause of EM side-channel attacks, near field radiation from an ICs wire layers that act as unintended antennas. Combining these findings with IC power management protocols, we can identify that the major contributing EM leakage are the top two wire layers that disseminate power throughout the IC. These layers are intentionally thicker to carry more current thereby maintain power and timing benchmarks. Current IC technology are only exasperating the leakage from these top power layers, as shown by examining Intel's IC technology: 180nm [14], 130nm [15], 65nm [16], 45nm [17], and 32nm [18]. We propose an augmentation to our Quantization Controller design, by leveraging its isolation nature to reduce the length and power of the unintended EM antennas created by the wire layers.

- Chapter 5 concludes this work with a summary of the results and recommendations for further work. We discuss the effectiveness of μLeech as mimicking low power IoT devices, using μLeech as a side-channel evaluation platform, leveraging isolation as a countermeasure in our Quantization Controller design, and our proposed Quantization Controller EM augmentation. Our proposed design would effectively reduce side-channel leakage by protecting against multiple side-channel attacks: power [6], timing [7], electromagnetic [8], thermal [11], power glitching [19], and Memory fault [20] attacks.

## Chapter 2

μLeech: A Side-Channel Evaluation

### Platform for IoT

With Moore's law continuing to drive down the cost of computation, we are experiencing an explosion in the number of embedded devices flooding the market, including smartphone connected point-of-sale devices, smart home devices or smart-watches. The Square point-of-sale unit, in particular, has gained traction in the market. The versatility and convenience of the design has propelled the product into widespread adoption. Such embedded, small footprint, highly connected, and low-power devices make up the backbone of the Internet of Things (IoT): they are attached to *things* in our environment we wish to track and control remotely. These devices are highly susceptible to physical attacks as there are many of them with loose isolation potentially in the reach of an attacker. Given physical access, an attacker can steal sensitive secrets, i.e. encryption keys and authentication credentials.

In this work for the first time we develop a side-channel evaluation platform,  $\mu$ Leech, which mimicks the form factor and operational characteristics of IoT devices. Our design is modeled after the Square design, i.e. it uses the microphone/speaker interface to power

the unit and to communicate between the device and the smartphone. In the development of our design we started by examining the Hijack project [21]. Ultimately our communication protocol differs as we do not need to communicate continuous sensor data, but short bursts of data, draining less power in the process. Our  $\mu$ Leech design acts as a universal power scavenging unit and may also be used as a Trusted Platform Module (TPM) for untrusted smartphones that can execute sensitive queries directly on the  $\mu$ Leech processor, e.g. by using secret keys and authentication tokens that are programmed into  $\mu$ Leech. The fact that these keys will never leave the device keeps them protected.

### 2.1 Side-Channel Evaluation Platforms

There are many platforms available that can be used to assess vulnerabilities of implementations to side-channel attacks. Some are commercially available and others developed for academic use. The following lists the most prominent:

- Side-channel Attack Standard Evaluation Boards (SASEBO) are standard evaluation boards developed by Tohoku University [22]. SASEBO Boards were developed to perform security tests for side-channel attacks. Their goal was to standardize the testing requirements of cryptographic modules. They are capable of evaluating side-channel attacks against cryptographic hardware with FPGAs and cryptographic software with microprocessor function.

- Flexible Open-source Board for Side-channel analysis (FOBOS) is an academic platform developed at George Mason University [23]. FOBOS is a platform for implementation attack resistance testing. FOBOS aims to provide an open-source platform. Their platform can be used to evaluate the effectiveness of side-channel analysis countermeasures on FPGA platforms. FOBOS supports multiple FPGA devices and the necessary software to run differential power analysis attacks.

• Side-Channel Analysis Resistant Framework (SCARF) is an open-source academic tool developed by the Electronics and Telecommunications Research Institute [24]. SCARF can be used for testing countermeasures for side-channel and fault attacks. They include a number of custom evaluation boards to test the attack resistance of smart-cards, microprocessors, and FPGAs. SCARF only supports testing of the devices included in its custom evaluation boards.

The following are a few tools that can be used with these side-channel evaluation platforms:

- The DPA Workstation is developed by Cryptography Research Inc. [25] and can be used to perform side-channel analysis including differential power or electromagnetic analysis on embedded systems. The DPA Workstation includes its own environment and proprietary software that can perform side-channel analysis on all major standard ciphers.

- InspectorSCA is a closed-source device developed by Riscure [26]. This platform can be used for side-channel analysis and fault analysis. It includes fault injection hardware and includes proprietary software that can perform side-channel and fault attacks on standard ciphers.

- ChipWhisperer is an open-source tool-chain for embedded hardware security research [27]. It can be used for side-channel power analysis and glitching and is known for its synchronous capture technology. Similar tools are commercially available but far more expensive and closed-source.

Numerous IoT devices have already been deployed as trusted devices in security critical applications, and yet they have not been properly evaluated for side-channel leakage. The existing platforms summarized above have characteristics drastically different from

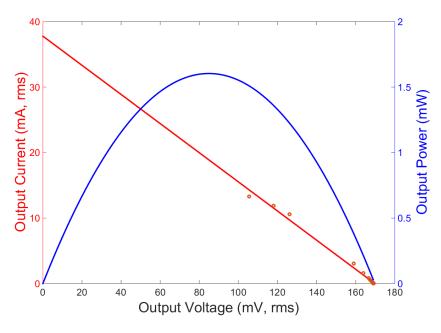

Figure 2.1: Nexus 4 headset jack available power.

IoT devices.  $\mu$ Leech is a side-channel evaluation platform representative of a power scavenging IoT device: power is scavenged from the right audio channel, two-way communication through the left audio channel and the microphone. Our platform provides the ability for security researchers to analyze side-channel leakage in next-generation mobile attached embedded devices. Just like SASEBO, FOBOS, and SCARF the  $\mu$ Leech evaluation platform will include high-quality onboard peripherals to our power and clock signals, allowing for easy access of signals necessary for side-channel analysis. This platform will allow for the development and enrollment of countermeasures.

### 2.2 Overview of the Design

Most cryptographic primitives require short and highly intensive computation. Taking advantage of this, we designed our power circuit with a capacitor bank that can be discharged and recharged. This allows our processor to perform any cryptographic operation

while draining the capacitor bank. We optimized our design to allow one round of AES to be computed before depleting the capacitor bank. Once the capacitor bank is depleted the processor will hibernate in sleep mode, allowing the capacitor bank to recharge again for another round of computations. To achieve this, we developed a low power sleep circuit that notifies the processor when to sleep and wake, thereby allowing the processor to operate off the limited power generated by our smartphone.

### 2.2.1 Power Siphoning

In keeping with the concept of a universal jack, our power has to be generated from the auxiliary jack. Therefore, we have to siphon power from an audio waveform. To determine the available power from our Nexus 4 headset port, we generated a 500 mV peak to peak AC audio waveform. A load resistance was connected between the right audio channel and the common line of the auxiliary jack. While measuring the output voltage across the resistor and the load current, the load resistance was varied from  $0\Omega$  to  $15k\Omega$ . We measured a total of 24 different resistor values. Using this data, we generated a linear fit, represented by the red linear IV curve in Figure 2.1 and the blue power transfer curve in Figure 2.1. The power transfer curves show that the maximum power transfer occurs at  $85mV_{rms}$  and  $18.87mA_{rms}$ , with an ideal load of  $4.51\Omega$ .

The data in Figure 2.1 shows that it is possible to draw 1.61mW from an ideal matched load of  $4.51\Omega$ . For this power to be useful our power siphoning circuit will have to rectify the 500mV peak to peak waveform from AC to DC, boost it, and filter it. The power siphoning circuit we implemented was modeled off of the Hijack's power siphoning circuit [21], with a few modifications. The circuit we implemented is depicted in Figure

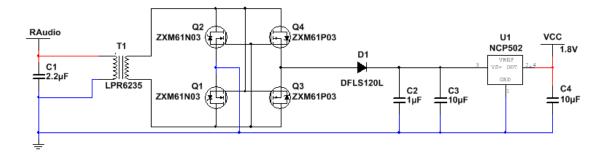

The input of the circuit Figure 2.2 is the Right audio channel of the smartphone. The app we implement will generate a continuous 500mV peak to peak audio waveform only onto the right audio line. Using this audio line and this circuit we are able to generate a

Figure 2.2: Power Circuit

Figure 2.3: Power Circuit Analysis

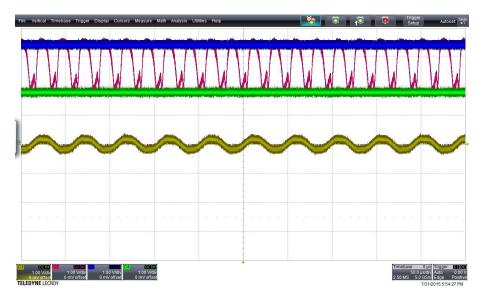

1.8V source for our processor. Key points of the transformation of the 400mV peak to peak audio waveform through the circuit in Figure 2.2 were captured and illustrated in Figure 2.3.

The yellow signal is the raw waveform coming out of the smartphone. The first step in trying to use this audio frequency is to step up the low supply voltage level. Using a 1:20 micro-transformer we step up the incoming supply voltage level as shown by the red signal. Normally the next step would be to use a Schottky diode to perform low-loss blocking. However using a combination of N and P MOSFETs depicted in Figure 2.2, we can perform a FET-based rectification from AC current to DC. This allows us to be able

to use the negative part of our input waveform to generate power as well. The spikes on the low edge of the red signal are generated by the FET bridge that would have otherwise been clipped out, optimizing our power generating capability. Using the Schottky diode to provide low-loss blocking, will prevent the capacitor bank from being discharged through the FET bridge, illustrated by the Blue signal. The final step is to use a 1.8 voltage regulator to power our processor, the Green signal.

Our goal was to allow our processor to be able to perform more power intensive cryptographic computations, without using a battery and while staying within the limitations of our smartphone power generating capability. Therefore using this power siphoning circuit and a series of capacitors, that could be discharging and recharged merely by going into sleep mode, we are capable of allowing our device to remain charged for at least one round of AES.

### 2.2.2 Capacitor Bank

Every smartphone model will have its own power draw model and ideal matched load. To aid with power management, we implemented a capacitor bank that will aid us in granting enough power for one round of 128-bit AES. As our processor implementations continue to evolve, we will continue to optimize our power consumption. However, different cryptographic operations may consume more power than our current 128-bit AES implementation. This means that our capacitor bank needs to contain enough of a charge between the time our sleep circuit switches between its wake and sleep state. Knowing that our sleep circuit activates the processor's wake state at 1.95V and sleep state at 1.65V we can calculate the necessary capacitor bank we would need for one round of 128-bit AES, if we know the current consumption and amount of time it takes. As shown later AES consumes approximately 555  $\mu$ A and takes 140 $\mu$ s for one round, see Table 2.3. Therefore we need a 0.28 $\mu$ F capacitor bank to power one AES round.

Figure 2.4: Sleep Circuit.

Currently, our capacitor bank was added after our 1.8 voltage regulator. This was done initially because our measured voltage change were measured after our voltage regulator. For optimal efficiency, the capacitor bank should be recalculated and inserted before the voltage regulator. Although the capacitor bank was initially designed for one round of 128-bit AES, the design still works with whatever implementation our processor is computing. As long as the power drops the sleep circuit will activate sleep mode allowing for the capacitor bank to recharge. Such functionally will be useful with any smartphones as the bank will aid in allowing for more continuous power.

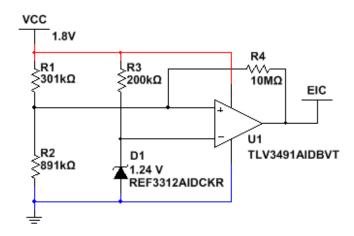

### 2.2.3 Sleep Mode

To allow the capacitor bank to recharge as efficiently as possible, we had to minimize power consumption during sleep mode. In addition, we would need a way of telling the processor to go to sleep and not to wake up until the capacitor bank was adequately recharged. For this we built a sleep circuit, illustrated in Figure 2.4, that would tell the processor through an external interrupt when to go to sleep and when to wake up.

Our sleep circuit uses a total of four 1% tolerance resistors, one low power voltage reference, and one low power comparator. This circuit has minimal power consumption

and produces one output signal from the comparator. This signal is driven either high or low, and can be used as a digital input. When connected to the external interrupt controller of our processor this signal can be used to notifying our processor when to go to sleep, low for optimal power performance, and when to wake up.

Atmel's AVR UC3-L0 has multiple interrupts and external interrupts. The UC3-L0 has a total of seven sleep modes [28]. Only the two highest power consumption sleep modes can wake up from a synchronous source, ruling out using an internal interrupt routine. However, all sleep modes, except for shutdown mode can be achieved with an asynchronous source. Connecting the external signal generated from our sleep circuit to two external interrupt pin, we can use two external interrupt routines to go to sleep (low) and wake up (high). Both of these external sleep/wake interrupts have been given the highest priority to supersede any other interrupts. This is to guarantee that when our capacitor bank is almost drained the processor will go to sleep before losing power allowing the capacitor bank to charge up again.

Our processor operates at 1.8V, but using its power thresholds our comparator will notify the processor to go to sleep at 1.65V and to wake up at 1.95V. Measuring the time it takes for one round of AES we modified our capacitor bank for ample time to complete before recharging.

#### 2.2.4 Side-Channel Platform

As a side-channel evaluation platform, our main goal was to provide easy acquisition of high-quality power signals for Differential Power Analysis (DPA). We added three  $1\Omega$  resistors in series to our design before the decoupling capacitors of our processor. The resistors were placed as close as possible to the processor's respective pins, and the copper pads were expanded, to minimize the amount of added noise. One resistor was added to the ground rail and the other two to the power rails. All three resistors can also

Figure 2.5: µLeech Evaluation Board.

be individually shorted to allow for custom measurements. The current version of our evaluation platform is illustrated in Figure 2.5. The three blue shunts are the jumpers to the three resistors. In addition, we added two external clock sources that can be selected for our Processor: a 1 MHz crystal and an SMA connector. The SMA connector can be used to feed a clock signal directly, thus also rendering the board ready for clock-glitching evaluation.

### 2.3 Data Communication

The communication protocol was modeled off of Hijack's communication protocol [21]. This design does not require any analog to digital converters, which results in less power drain but slower communication speeds. The smartphone transmits analog signals and the processor transmits in digital, but each communication is handled in the time domain, using Manchester Encoding [29].

Manchester Encoding is a form of digital encoding where bits are represented by transitions from one logical state to the other, instead of being represented by a high or

**Figure 2.6:** μ*Leech Execution Cycle.*

low signal. This means that instead of having to detect an analog high and low period, we now have to measure the periods between switches. Allowing a smartphone that can only output and read audio oscillating waveforms to transmit and receive a waveform with Manchester encoded data.

For the processor, transmitting in Manchester encoding to the smartphone is straight forward. The processor can generate a square wave at any frequency, doubling the period for a bit flipping, that can simply be interpreted by a smartphone as an oscillating waveform. On the other hand, decoding incoming data from a smartphone outputting an oscillating audio waveform instead of a digital signal to the processor is not as straightforward. The processor instead will have to determine the period lengths between the oscillations. Allowing the processor to determine if the incoming Manchester encoded data is flipping its bit, double the period, or not.

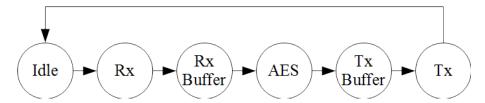

We have modified our communication protocol to work serially and in conjunction with the overall process of the processor.  $\mu$ Leech is not a continuously operating device as such it does not need to transmit and receive data continuously. We only transmit and receive data in bursts when necessary after secure execution. This allows for more computation cycles and overall less power drain on our system. Figure 2.6 depicts a flow chart of  $\mu$ Leech execution cycle for an AES implementation.

In Idle our processor is continuously waiting to receive a transmission from the smartphone. Once data is received it triggers our communication state-machine that grabs the incoming data. The state-machine then converts the raw incoming Manchester data into binary data. This incoming data includes the instructions for our processor. Using the obtained data our processor then performs it AES encryption/decryption. It then triggers the transmit state of the state machine. The state machine will then converting the raw data into Manchester encoded data and transmit this to the smartphone. The transmission burst is repeated four times by our processor, after which it returns to Idle waiting to receive further instruction from the smartphone.

Currently, we are transmitting at approximately an average of 0.9kbps. Our current transmission speeds are unfortunately severely slower than regular digital communication. This is mainly due to the fact that our data is transmitted in Manchester Encoding that doubles the number of cycles. In addition, there are delays that are added through our communication state-machine. In the next iteration we will be optimizing our communication state-machine for intermittent communication.

### 2.3.1 Manchester Encoding

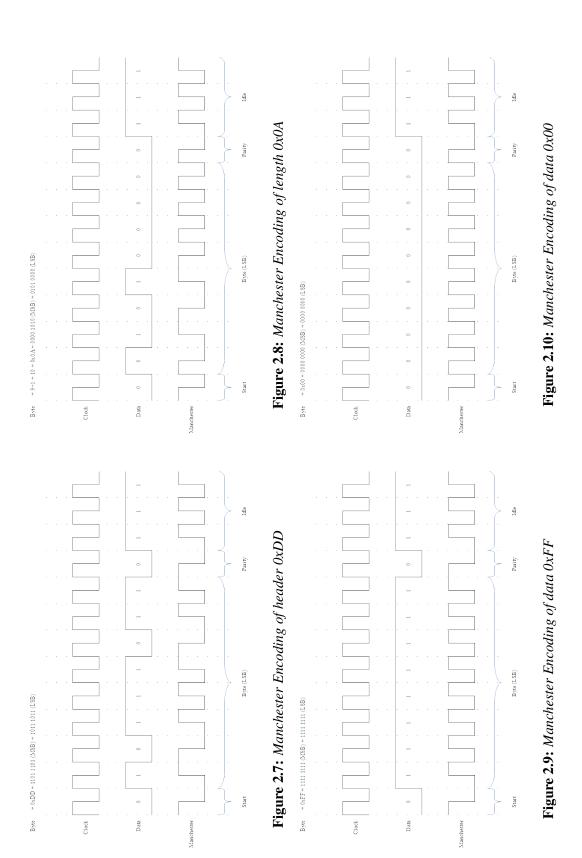

Manchester Encoding is a form of digital encoding in which data bits are represented by transitions from one logical state to the other. The encoding of digital data in Manchester format defines the binary states of a 1-bit and 0-bit to be transitions rather than static values. Manchester encoding was developed at the University of Manchester, where the coding was used to store data on the magnetic drum of a Manchester Mark 1 computer. There are two opposing conventions for Manchester encoding, both are used by numerous authors.

The first convention of Manchester Encoding was first published by G. E. Thomas in 1949. It stated that for a 0-bit the signal levels would be low-high and for a 1-bit the signal levels would be high-low. The second convention used by IEEE 802.4 and IEEE 802.3. It states that for a 0-bit the signal levels would be high-low and for a 1-bit the signal levels would be low-high. These two conventions are opposites of each other.

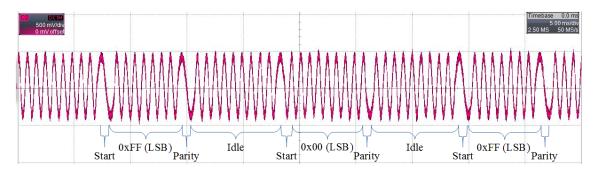

For our application, we followed the IEEE convention. Illustration examples of Manchester Encoded data can be found in Figures 6 through 9. These examples are illustrations of an implemented transmission using Hijack's communication protocol.

- Figure 2.7 is the header of the transmission.

- Figure 2.8 is the transmission byte length.

- Figure 2.9 and Figure 2.10 are two different data values that were transmitted.

We choose only to use two data values so that the illustration would be simpler to follow. The transmissions are handled one byte at a time. Each byte has a start bit of 0 and a parity bit at the end. The actual transmission streams of the processor and smartphone can be found in Figure 2.14 and Figure 2.18 respectively. The transmission captured match these illustrations.

Manchester Encoding allows for an overall reduced physical footprint and power consumption due to the lack of digital to analog and analog to digital converters. In addition, since Manchester Encoding ensures frequent line voltage transitions, which are directly proportional to their clock rate, an oscillating audio waveform can be manipulated into representing Manchester Encoded data. This makes it ideal for IoT communication systems through auxiliary jacks.

#### 2.3.2 Transmit

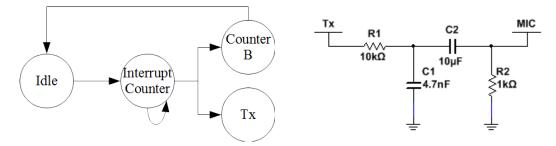

Data sent from the processor to the smartphone will be sent along the microphone channel of the auxiliary port. The communication protocols used for creating this audio waveform were modeled off of Hijack's communication protocol. The major difference being that when in this state we only use the transmit portion of Hijack state-machine, as shown in Figure 2.6. The protocol we implemented to activate the transmit portion of the state machine is illustrated in Figure 2.11.

**Figure 2.11:** μ*Leech Transmit Flow Chart.*

**Figure 2.12:** μ*Leech Transmit Circuit.*

For our transmit protocol we used one of our processors built in synchronous counter and one asynchronous counter. The counters are only activated when the processor is in the transmit state (Tx), in Figure 2.6. When the counter is activated, it will trigger an interrupt every time it reaches a predetermined value. This value is the frequency of our generated signal, every time the interrupt is triggered is one clock cycle of our output stream. This event triggered interrupt will do two things: trigger the transmit state of the state-machine and increment a second asynchronous counter B. The second counter B is used to keep track of how many transmission have taken place, after four full transmissions the counter will exit the transmission stat and turn off the counter.

At the hardware level the only important thing with the transmission circuit is to have a 1k load resistor. The 1k Ohm resistor is necessary to activate the microphone channel on most smartphones; without it, the smartphone would not know there was data coming in on the microphone channel. The processor will then output an oscillating square waveform approximately 800mv pk to pk. The transmission circuit we implemented is shown in Figure 2.12.

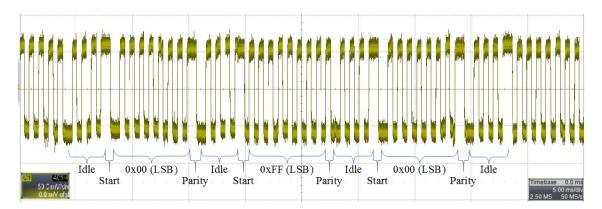

An example of a transmission stream from our  $\mu$ Leech to our smartphone was captured and illustrated in Figure 2.14. Using the Manchester encoded byte examples in Figures 2.7 through 2.10 we can see the data captured in Figure 2.14. The communication protocol of the processor transmits in the format depicted in Table 2.1.

Each byte has a start bit of 0 and a parity bit at the end. This means each byte trans-

| Byte    | 1          | 2          | 3          | 4          | 5           | 6          | 7           | 8          | 9           | 10         | 11          | 12        |

|---------|------------|------------|------------|------------|-------------|------------|-------------|------------|-------------|------------|-------------|-----------|

| Content | Header     | Length+1   | Data0      | Data1      | Data2       | Data3      | Data4       | Data5      | Data6       | Data7      | Data8       | Check Sum |

| Value   | 0xDD       | 10         | 0xFF       | 0xFF       | 0x00        | 0xFF       | 0x00        | 0xFF       | 0x00        | 0xFF       | 0x00        | -         |

| Image   | Figure 2.7 | Figure 2.8 | Figure 2.9 | Figure 2.9 | Figure 2.10 | _         |

Table 2.1: Smartphone Transmission Burst.

**Figure 2.13:** μ*Leech Transmission - Zoomed in.*

**Figure 2.14:** *μLeech Transmission*.

mission is actually 10-bits which are then transmitted in LSB in Manchester encoding. However, in between each byte transmission the state-machine goes into an idle state, where it continues to transmit digital high for a fixed four delay count. Figure 2.13 depicts a zoomed in view of the Manchester encoded captured data burst shown in Figure 2.14.

#### 2.3.3 Receive

Data sent from the smartphone to the processor will be sent along the left audio channel of the auxiliary port. The communication protocols used for interpreting this audio waveform were modeled off of Hijack's communication protocol. The major difference

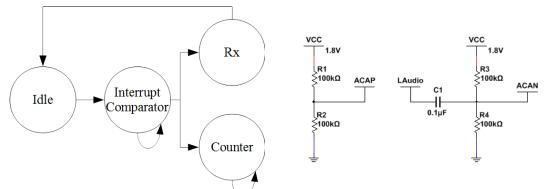

**Figure 2.16:** μLeech Receive Circuit.

**Figure 2.15:** *μLeech Receive Flow Chart.*

being that when in this state we only use the receive portion of Hijack state-machine, as shown in Figure 2.6. The protocol we implemented to activate the receive portion of the state-machine is illustrated in Figure 2.15.

For our receive protocol, we used one of our processors built in synchronous comparator driven interrupt and counter. The comparator and counter are only activated when the processor is in the receiving state (Rx), in Figure 2.6. When the comparator is activated it will trigger an interrupt every time there is a bit flip on the incoming Manchester encoded data stream. This event triggered interrupt will do two things: trigger the receiving state of the state-machine passing it the counter value and reset the counter. This will allow the state-machine to know the length of time between bit-flips. Since the incoming data is represented in Manchester encoding, the state-machine will be able to determine if the previous bit was flipped or not. Allowing us to decode the income Manchester data into binary data.

What this means for our hardware, is that we have to feed the comparator in our processor two inputs: an oscillating audio waveform from the smartphone's left audio channel and a constant signal that is the mean voltage level of the oscillating audio wave, as shown in Figure 2.16.

The smartphone will output an oscillating waveform of approximately 900mV pk to

| Byte    | 1          | 2          | 3          | 4          | 5           | 6          | 7           | 8          | 9           | 10         | 11          | 12        |

|---------|------------|------------|------------|------------|-------------|------------|-------------|------------|-------------|------------|-------------|-----------|

| Content | Header     | Length+1   | Data0      | Data1      | Data2       | Data3      | Data4       | Data5      | Data6       | Data7      | Data8       | Check Sum |

| Value   | 0xDD       | 10         | 0xFF       | 0xFF       | 0x00        | 0xFF       | 0x00        | 0xFF       | 0x00        | 0xFF       | 0x00        | -         |

| Image   | Figure 2.7 | Figure 2.8 | Figure 2.9 | Figure 2.9 | Figure 2.10 | -         |

**Table 2.2:** *Smartphone Transmission Burst.*

Figure 2.17: Smartphone Transmission - Zoomed in.

Figure 2.18: Smartphone Transmission.

pk with a lot of noise. The first step in our receive circuit is to drain out the noise with a capacitor, then using a pull-up resistor and a pull-down resistor we can generate an 800mV peak to peak oscillating at a mean of 800mV. However, when you take into account the additional pull-down resistor built into the processor, on the input pin, the signal is oscillating at a mean of approximately 900mV. This means, for our comparator to trigger we need to feed it another constant 900mV signal. Since our processor is operating at 1.8V using a simple voltage divider on our voltage source with equal resistors, we can divide the voltage level by half and generate a constant input signal of 900mV, with minimal power loss. This will allow our comparator to trigger exactly when our oscillating audio signal is switching from low to high, allowing us to retrieve the period length determining if the Manchester encoded audio waveform is bit flipping or not.

An example of a transmission stream from our smartphone to our  $\mu$ Leech was captured and illustrated in Figure 2.18. Using the Manchester encoded byte examples in Figures 2.7 through 2.10 we can see the data captured in Figure 2.18. The communication protocol of the smartphone transmits in the format depicted in Table 2.2.

Each byte has a start bit of 0 and a parity bit at the end. This means each byte transmission is actually 10-bits which are then transmitted in LSB in Manchester encoding. However, in between each byte transmission the state-machine goes into an idle state, where it continues to transmit digital high for a fixed twenty delay count. Figure 2.17 depicts a zoomed in view of the Manchester encoded captured data burst shown in Figure 2.18.

### 2.4 Implementation Results

The performance of our device is evaluated with a focus on power consumption. Our device is designed to operate solely off of the power generated from an audio waveform. As a result, we have made numerous modifications to optimize performance within our power generating capabilities. We optimized for power by modifying our capacitor bank to at least allow for one round of AES encryption before depletion. For this, we measured the power consumption of our different modes: idle, sleep, communication, and AES. Then we measured the duration of each of these modes so that we could accurately estimate our capacitor bank.

### 2.4.1 Sleep Mode

There are many different sleep modes available to the UC3-L0. Table 2.3 shows the power consumption of the lowest three power consumption sleep modes available for a single supply mode design. The main differences between these three sleep modes are

**Table 2.3:** µLeech Power Consumption

| Processor State         | <b>Power Consumption</b> |  |

|-------------------------|--------------------------|--|

| Idle                    | 539 μΑ                   |  |

| Receiving Data          | 588 μΑ                   |  |

| Transmitting Data Burst | 575 μΑ                   |  |

| 128-bit AES Encryption  | 555 μΑ                   |  |

| 128-bit AES Decryption  | 555 μΑ                   |  |

| Sleep Mode              | <b>Power Consumption</b> |  |

| Stop                    | 92.6 μΑ                  |  |

| DeepStop                | 68.3 μΑ                  |  |

| Static                  | 56.7 μΑ                  |  |

which clock sources are left enabled. For this reason, our design uses an external clock crystal that allows us to use DeepStop and Static sleep modes. Static mode requires us to reinitialize some of our clock signals, and therefore the modules using them, on every wake-up. For this reason currently, our design uses DeepStop which is less of a power drain on the overall system for every wake-up cycle.

### 2.4.2 Active Mode

In active mode, our UC3-L0 is: idling, communicating, or performing AES. Our processor only checks for incoming data when it is idling and waiting for instructions. Computations are only executed when the processor receives new incoming data or new instruction sets. The processor transmissions are executed only when there is a change in the outgoing data and computations have been completed. The transmissions are in short bursts repeated four times for redundancy error checking. The measured power consumption of these processor states is listed in Table 2.3. Currently, our design's highest power consumption is in our communication protocol.

### 2.4.3 128-bit AES

Atmel's AVR UC3-L0 combines low power consumption and computational capacity. 128-bit AES was implemented in software and tested for power consumption. The power consumption of 128-bit AES encryption and decryption are shown in Table 2.3. The measured performances of our processor are operating at a clock speed of 1 MHz. This clock is generated using an external 1 MHz clock crystal. Encryption and decryption were timed at 1.378 ms and 1.400 ms respectively. Modifying this external crystal we can achieve higher performance implementations of AES, but in the process increase our power consumption.

# 2.5 Conclusion

$\mu$ Leech is a low power IoT side-channel evaluation platform. As such, it was optimized for minimal power consumption. The power consumption of  $\mu$ Leech was optimized by utilizing the various sleep and active states of the processor.  $\mu$ Leech provides a secure low power scavenging trusted cryptographic platform for any smartphone. Our design also includes interfaces to facilitate easy acquisition of high-quality power signals for Differential Power Analysis, as well as an SMA connector to manipulate the clock source.  $\mu$ Leech enables security researchers to analyze leakage in next-generation mobile attached embedded devices and to develop and enroll countermeasures to protect future IoT devices.

# Chapter 3

# Quantized Computing: On-demand Isolation as a Power and Timing Side-channel Defense

Side-channel emanations compromise secure execution by revealing secret data [5]. There are a wide range of side-channels attackers use to extract secrets, with power [6] and timing [7] side-channels being the two most readily exploited [12]. All electronic devices generate power and timing information during execution. This information is observable by monitoring the power rail—using relatively pedestrian equipment—to capture execution emanations [6]. Attackers analyze these captures either directly or using differential analysis [6] to deduce otherwise secret information. The fundamental issue is that the power rail provides *fine-grain* information about security-critical execution.

Existing side-channel defenses focus on the attacker's signal-to-noise ratio: increasing the noise or decreasing/hiding the signal. Countermeasures include: reducing the magnitude of side-channel emanations [30], the addition of noise to mask side-channel emanations [31], obfuscation to hide the relative timing of the secret-revealing emana-

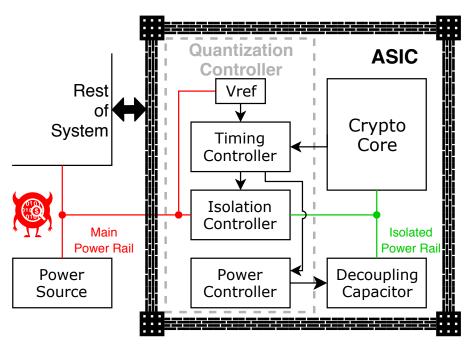

Figure 3.1: Quantized Computing system overview.

tion [32], and incorporating randomness at the software level [13].

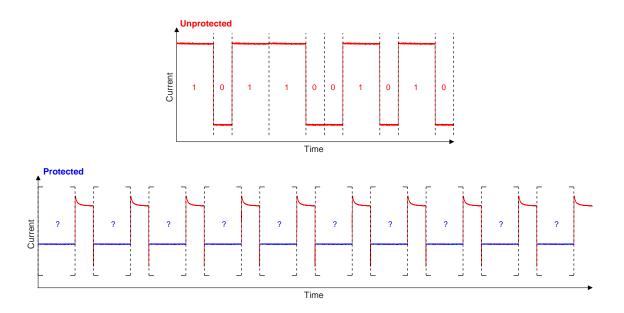

Alternatively, we advocate *isolation*. Our countermeasure works by performing computation with secret-revealing side-channels in fixed-sized power/time chunks isolated from the rest of the system—and the attacker. By forcing secure execution into uniform power/time chunks, we effectively quantize the information revealed by power and timing side-channels. Thus, our approach provides control over the granularity of attacker-visible side-channel information. Assuming no secret-dependent execution-differences span quantized executions, then, from the attacker's perspective, the power and timing requirements are uniform and secret-independent. The challenge is to design an isolation system that eliminates both power and timing side-channels.<sup>1</sup> We achieve via a Quantization Controller: on-chip control logic that sits between a security-critical core and the rest of the system. As shown in Figure 3.1, the Quantization Controller dictates a secure

<sup>&</sup>lt;sup>1</sup>Many techniques for eliminating power side-channels result in increasing the information in timing side-channels and vice versa [33, 34, 35]. Given that there is *no* added burden for an attacker capable of measuring power to measure time, a defense must address both.

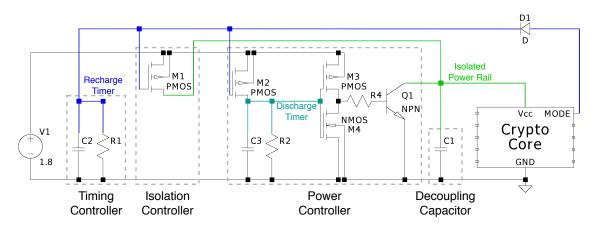

processor's power source; either from the system's main power rail—attacker visible—or from an internal—attacker invisible—energy storage capacitor (by repurposing existing integrated decoupling capacitors). To ensure uniform (hence secret independent) secure execution times, the Quantization Controller employs execution-agnostic counters (either digital or analog). To avoid leaking information during decoupling capacitor recharge, the Quantization Controller incorporates a discharge circuit to remove any charge remaining on the decoupling capacitor after secure execution. To protect against thermal fault attacks, we use state versioning to ensure secure computation atomicity [36, 37]. Lastly, to prevent voltage fault attacks, we add an internal voltage reference.

To demonstrate the effectiveness of our approach and explore its trade-off space, we implement three Quantization Controllers: a wholly-digital, a hybrid, and a full-custom variant. For the hybrid and full-custom controllers, we use capacitors and their natural leakage as execution-independent counters—as opposed to digital logic. All three designs quantize power and timing to eliminate their respective side-channel leakage, but our analysis reveals that the hybrid design is preferred due to its compactness and simplicity. We show that our approach defends against power and timing side-channels in software implementations of AES and RSA running on an ARM Cortex-m4-based microcontroller and hardware implementations of AES and RSA on an FPGA. Our evaluation also shows that existing decoupling capacitors provide ample energy for our defense. Lastly, we analyze the software run time overheads of real software running on a complete (e.g., capacitor powered) prototype of our system.

Quantized Computing makes the following contributions:

- We use execution-independent counters to quantize secure execution time. This eliminates external fine-grain timing side-channels.

- We replace digital counters with capacitors to protect against thermal faults and

decrease area and power.

- We leverage on-demand isolation to make side-channel protection a dynamic and software-level decision.

- We design and implement three variants of our proposed Quantization Controller;

we evaluate the effectiveness and efficiency of these implementations against both

software and hardware implementations of AES and RSA.

- We verify our approach with a capacitor-powered prototype that we use to understand the software run time overheads experienced by software that relies on AES functionality.

# 3.1 Background

All computing devices generate side-channel emanations as a byproduct of physical implementation and computation [5]. The key to side-channel analysis is the interpretation of these leaks to reveal secrets. As such, there are many different side- channel leaks used to capture secrets. These include: power [6], timing [7], electromagnetic [8], acoustic [9], memory remanence [10], and thermal [11]. The two most commonly exploited side-channels in literature are power and timing [12]. The popularity of these two side-channels is due to the high bit rate and fine-grain (e.g., per clock cycle) information that they expose to the attacker. To gain access to this wealth of secret-revealing information, an attacker only needs to be able to measure the current consumed by the victim device. Given our goal is to counter these side-channels comprehensively and automatically, we address the following:

• Power Analysis: non-invasive analysis of the power rail during execution to reveal unintended leakage through current consumption. Depending on the signal-

to-noise ratio, attackers employ one of three power analysis techniques (in order of increasing complexity): Simple Power Analysis (SPA) [6], Differential Power Analysis (DPA) [6], and High-order Differential Power Analysis (HO-DPA) [38]. SPA is useful when the difference in current due to secure information is large relative to noise. When the signal is burried in noise, DPA uses statistical analysis of multiple executions to detect differences. To address cases of extremely small signal-to-noise ratios, HO-DPA extends DPA by correlating the statistical changes in multiple variables to uncover secret-dependent current changes. No matter the power analysis technique used, the measurment system consists of an oscilliscope and a probe; common equipment, even for university labs.

- Timing Analysis: non-invasive analysis of execution to reveal untended leakage through response latency or performance. Attackers use timing analysis when an algorithm or processor has secret-dependent execution time. Possible sources of timing variation include performance optimization [39], branching and conditional statements [7], processor instructions [40], RAM [41], and cache hits [42]. The infrastructure required for timing analysis varies depending on the granularity of the timing difference in secret-dependent execution. In the most extreme case, timing analysis requires the same complexity setup as power analysis.

- Fault Attacks: induce faults via unexpected environmental conditions to reveal unintended leakage through inconsistent system state. Depending on the target system there are many ways of inducing faults, including: temperature [43], power [19], overclocking [44], electromagnetic fields [45], and ionizing radiation [46]. Our design defends against temperature and power fault attacks since these can have a targeted effect and are available to a side-channel attacker.

Addressing all three threat vectors at once is a challenging task, but essential for

true improvements in security. Creating a comprehensive countermeasure is challenging due to the inherent reciprocal relationship between side-channels. Mitigating one side-channel in isolation often results in shifting the information to another side-channel. For example, consider a *broken* version of our approach that uses only isolation from the power rail to protect against fine-grain power analysis. This means that secure execution time—hence the time the crypto core is disconnected from the power rail—is dictated by secret information. Thus, the attacker sees a square wave on the power rail that divulges the exact execution time of the secure execution. Therefore, we must eliminate both power and timing side-channels and guard against thermal and power fault attacks.

# 3.1.1 Decoupling Capacitors

System designers add decoupling capacitors to an Integrated Circuit (IC) to filter out noise from the power supply. Conceptually, the power supply provides a constant voltage to the chip. Practically, the highly-variable load caused by different amounts of switching transistors results in voltage drops as the power supply struggles to supply enough current to maintain the desired voltage. Making matters worse, power rails are shared by many ICs on the same Printed Circuit Board (PCB). Large voltage drops cause the IC to have a power fault; resulting in an inconsistent state or a reset.

To protect against voltage drops, system designers add capacitors between the power rail and the IC. These capacitors decouple the IC from the power rail, acting as a filter for power supply noise; when voltage would drop, the decoupling capacitor sources additional charge to maintain the desired voltage. We leverage the observation that even when the power rail goes to 0V, the decoupling capacitor supplies enough current to keep the IC running for a short amount of time.

Traditionally, system designers add decoupling capacitors external to the IC as part of the PCB layout. Recent advances in IC integration enable adding decoupling capacitors inside the IC [47, 48, 49]. Internally-integrated decoupling capacitors have the advantage of lowering the cost of adding the IC to a PCB, reducing the chance of layout errors, and providing IC designers quality guarantees about incoming power. We leverage internal decoupling capacitors to hide current consumption information from an attacker who is unable to non-destructively interpose between them and the IC.

# 3.2 Threat Model

Our threat model assumes an attacker with knowledge of the software running on as well as with full physical access to an IC. The attacker's objective is to extract secret information through non-destructive, non-invasive, timing and power side-channel analysis. We assume that the attacker can also control the power supplied to the device as well as its environment to induce power and thermal faults.

On the other hand, we assume that the attacker has no capability to non-destructively interpose between the crypto core and the Quantization Controller. Traditionally, the external nature of decoupling capacitors made it easy for attackers to interpose by removing them from the circuit board. With the recent trend of integrated decoupling capacitors, they are now an integral part of the circuit itself, making interposing destructive. In cases of nation-state adversaries, it is common to employ anti-tamper techniques to prevent attackers from non-destructively analyzing the contents of the chip [50].

Following our observation on isolating integrated decoupling capacitors, we develop a comprehensive and mostly automatic power and timing side-channel defense that is immune to thermal and power fault attacks.

# 3.3 Quantization Controller Design

At the core of our Quantization Controller design is the observation that isolating integrated decoupling capacitors from the external power rail prevents the attacker from seeing fine-grain power side-channel information. Unfortunately, isolation alone is insufficient as coarse-grain information still reveals secrets. To form a comprehensive solution that addresses power and timing side-channels completely, we layer on top of isolation components that mask variations in timing and power by ensuring that the power and time required by secure execution is execution-invariant—from the attacker's perspective. Lastly, we address several thermal and power fault attacks created by our approach. This section details each component of our Quantization Controller.

### 3.3.1 Isolation Controller

The trend of integrating decoupling capacitors into the Integrated Circuit (IC) enables our approach. We observe that decoupling capacitors provide enough energy for modern low-power devices to continue execution for a short period after all power is removed. This presents an opportunity, because, as our evaluation shows (Section 3.6), decoupling capacitors provide enough energy to execute popular cryptographic algorithms. As Figure 3.1 shows, our Isolation Controller uses this opportunity by selectively isolating (in an electrical sense) a crypto core from the main power rail when it performs secure execution (i.e., execution that requires protection from power and timing side-channels). During regular (i.e., insecure) execution, the external power rail continuously provides power to both the crypto core and the decoupling capacitor; allowing the decoupling capacitor to charge. Isolation is triggered by the crypto core when it is ready to start secure execution, allowing the software to balance security guarantees and performance dynamically. Thus, the Isolation Controller ensures that all fine-grain power and timing side-channel

information generated by the crypto core is hidden from an attacker with access to the main power rail and only exposed as coarse-grain information. System designers have the ability to control the granularity of side-channel information exposed to an attacker by changing the size of the decoupling capacitor.<sup>2</sup>

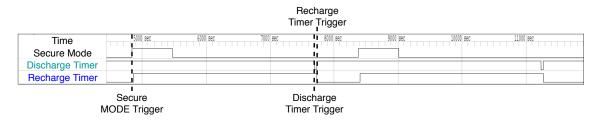

# **3.3.2** Timing Controller

Although isolating the crypto core from the main power rail eliminates fine-grain power and timing side-channels, it makes coarse-grain power and timing side-channel information more evident to the attacker. One source of coarse-grain side-channel information is the amount of time required for secure execution; an attacker measures this as the amount of time the crypto core is isolated from the main power rail. The mitigation for coarse-grain timing side-channels is computation-invariant secure execution length.

To eliminate coarse-grain timing side-channels, the Quantization Controller includes a Timing Controller that uses a timer to equalize time spent in secure execution—making it computation invariant. When the crypto core requests secure execution, the Timing Controller resets the timer to a seed value. As secure execution occurs, the timer decrements. Once the timer reaches zero, the Timing Controller ends secure execution by reconnecting to the main power rail. The only constraint is that the secure computation completes before the timer reaches zero. In Section 3.3.4 we employ data versioning to address cases where, through fault attacks or poor software design, secure computation does not complete before reconnecting to the main power rail.

From a high level, the Timing Controller quantizes secure computation into a series of fixed-time isolated executions. *Thus, adding the Timing Controller makes each secure execution constant time with respect to an attacker.*

<sup>&</sup>lt;sup>2</sup>Larger decoupling capacitors have benefits beyond enabling longer periods of secure execution in our approach: larger decoupling capacitors are more effective at filtering power supply noise and are also a power source for a range of anti-tamper techniques.

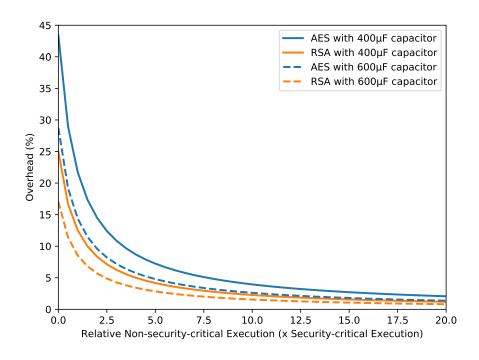

### 3.3.3 Power Controller

While adding the Timing Controller eliminates coarse-grain timing side-channels, coarse-grain power side-channels remain. One example of a coarse-grain power side-channel that isolation creates is the amount of charge required to recharge the decoupling capacitor once the Timing Controller reconnects to the main power rail. The amount of charge required for recharge indicates how much energy the crypto core consumed during secure execution—revealing secret-dependent differences in computation. Uniform-time secure executions do not mitigate this threat, because, from an energy perspective, they act as a constant energy expenditure (the idle current times the time of the secure execution) on top of which a security-dependent delta energy is added.

To eliminate coarse-grain power side-channels, the Quantization Controller includes a Power Controller that ensures that secure executions are uniform energy from an attacker's perspective. The Power Controller achieves this by removing any remaining charge from the decoupling capacitor before reconnecting to the main power rail. We call this Discharge Mode. To support Discharge Mode, we add a timer to the Timing Controller. Going into secure execution mode is the same, expect both timers are loaded with their seed value. When the first timer reaches zero, the Timing Controller goes into Discharge Mode, shorting the decoupling capacitor. When the second timer reaches zero, the Timing Controller goes into Recharge Mode by connecting the decoupling capacitor to the main power rail. The difference in seed values between the two timers must guarantee that there is enough time to completely discharge the decoupling capacitor.

Adding the Power Controller makes our secure execution both uniform in time and power with respect to an attacker.

### 3.3.4 Fault Attacks

Although the goal of our design is to eliminate power and timing side-channels, we realize that our defense also defeats power-based fault attacks, as well as creating a range of new attacks based on injecting faults around secure execution. Thus, our design also addresses a range of fault attacks: Power [19], Memory [20], and Thermal [11].