# **FPGA-Based Graphics Acceleration**

# A Major Qualifying Project Report

December 20, 2010

Submitted to the Faculty

of the

WORCESTER POLYTECHNIC INSTITUTE

in partial fulfillment of the requirements for the

Degree of Bachelor of Science

on this day of December 20, 2010

by

Eric Nadeau

Skyler Whorton

R. James Duckworth, Major Advisor

Emmanuel Agu, Co-Advisor

## Abstract

The goal of this project was to develop an FPGA-based 3D graphics accelerator. Research of previous work in the field preceded the development of a full hardware implementation of a graphics platform capable of realizing 3D graphics with an FPGA. Furthermore, a graphics application programming interface (API) and various rendering algorithms were implemented in software. We tested these implementations and verified that our goal was achieved with reasonable performance. Methods explored by this project showed promise for future customizable and portable 3D graphics platforms that may be utilized within mobile and embedded applications.

## Acknowledgments

We would like to sincerely thank the individuals who guided us through our Major Qualifying Project and made this experience a memorable one.

We would like to thank our project advisors, Professor R. James Duckworth and Professor Emmanuel Agu for their continuous help and support throughout the project.

## **Executive Summary**

The growing trend in the popularity of mobile computing has led to an increase in the demand for mobile graphics platforms. While graphics accelerators using Application-Specific Integrated Circuit (ASIC) designs have historically constituted the industry standard, they have presented roadblocks to developers who have wished to reconfigure the hardware or develop the platform in an open environment. Additionally, the long development cycle for ASIC designs has implied that only the leading hardware developers were able to produce worthy products. Although some open graphics acceleration platforms existed, these implementations (such as Mesa 3D, or Vincent 3D for embedded systems) were defined primarily as software systems. One possible option for a graphics acceleration platform was a design using a Field-Programmable Gate Array (FPGA). The FPGA presented design advantages such as its suitability for parallel processing applications, for example certain graphics operations, and its accessibility to developers who wish to modify the hardware platform to fit their specific needs. For these reasons, we explored a design of a graphics accelerator using an FPGA.

Our goals for a fully realized FPGA implementation of a graphics accelerator included a Hardware Descriptor Language (HDL) graphics hardware core, an accessible graphics software API using the OpenGL 1.1 specification and a basic implementation of the 3D graphics pipeline in Register Transfer Level (RTL) hardware. Finally, to test and verify the capabilities of our custom graphics platform, we needed to benchmark the system's performance using OpenGL-based applications.

The hardware we chose to use for this project was the Spartan-6 LXT FPGA residing on the Xilinx SP605 Development Board. Our implementation included a full Graphics Processing Unit (GPU), rasterizer, and video interface on the FPGA. Furthermore, we utilized the board's 128MB of DDR3 component memory for storing two framebuffers. We used the FPGA's MicroBlaze Central Processing Unit (CPU) to execute the platform's software driver, API and user graphics applications. The driver and API, implemented in C, included all of the functions necessary for a programmer familiar with the OpenGL specification to easily execute graphics applications on our platform. The platform implemented point, line, and triangle drawing, triangle filling, and color interpolation. Furthermore, we used the software to realize affine transformations of vertices and realistic ambient and diffuse lighting effects according to the Phong Reflection Model.

Additionally, we used OpenGL graphics applications to benchmark the performance of our graphics accelerator platform. Furthermore, we tested each demo application on both the hardware implementation and a custom, fully-realized software emulator designed to use precisely the same driver and libraries as the hardware. We found that the limitations of the CPU at only 75 MHz, and being responsible for the preparation of each primitive rendering, was often responsible for a bottleneck in performance. We concluded that this performance limitation was indicative of a shortcoming in the processor speed rather than in the FPGA's theoretical capability for graphics processing. Quantitatively, each of our simple graphics application demos achieved reasonable performance marks over thirty (30) Frames-Per-Second (FPS).

Considering the final architecture of our platform and the positive results of our test applications, we concluded that a graphics accelerator may be effectively realized through an FPGA design. For this reason, we recommended that future research be considered in the area of graphics applications of FPGA systems.

## Contents

| Τa       | Table of Contents |        |                                         | vi |

|----------|-------------------|--------|-----------------------------------------|----|

| Li       | st of             | Figur  | es                                      | ix |

| Li       | st of             | Table  | 5                                       | xi |

| 1        | $\mathbf{Intr}$   | oducti | on                                      | 1  |

| <b>2</b> | Bac               | kgroui | nd Research                             | 4  |

|          | 2.1               | Graph  | ics Rendering Pipeline                  | 4  |

|          |                   | 2.1.1  | Front End                               | 5  |

|          |                   | 2.1.2  | Vertex Processing                       | 5  |

|          |                   | 2.1.3  | Primitive Assembly                      | 6  |

|          |                   | 2.1.4  | Rasterization and Interpolation         | 6  |

|          |                   | 2.1.5  | Frame Buffer                            | 9  |

|          | 2.2               | 3D Ma  | athematics                              | 10 |

|          |                   | 2.2.1  | Transformation                          | 10 |

|          |                   | 2.2.2  | Fixed-Point Computations                | 12 |

|          | 2.3               | Target | Platforms                               | 13 |

|          |                   | 2.3.1  | Spartan-6 FPGA and SP605 Evaluation Kit | 13 |

|          | 2.4               | Graph  | ics Application Programming             | 14 |

|          |                   | 2.4.1  | OpenGL                                  | 15 |

|          |                   | 2.4.2  | Lighting in OpenGL                      | 15 |

|          |                   | 2.4.3  | Mathematics of Lighting                 | 16 |

|          | 2.5               | Relate | ed Work                                 | 18 |

|          |                   | 2.5.1  | Mesa 3D                                 | 18 |

|          |                   | 2.5.2  | Vincent 3D                              | 19 |

|   |      | 2.5.3 Manticore                | 20 |

|---|------|--------------------------------|----|

|   | 2.6  | Summary                        | 20 |

| 3 | Pro  | ject Overview and Design       | 21 |

|   | 3.1  | Goal                           | 21 |

|   | 3.2  | Objectives                     | 21 |

|   | 3.3  | Design Requirements            | 22 |

|   | 3.4  | Design                         | 23 |

|   |      | 3.4.1 Software Design Overview | 24 |

|   |      | 3.4.2 RTL Design Overview      | 26 |

|   | 3.5  | Summary                        | 30 |

| 4 | Eml  | pedded Platform Implementation | 31 |

|   | 4.1  | Hardware Implementation        | 31 |

|   | 4.2  | Software Implementation        | 33 |

|   | 4.3  | Summary                        | 33 |

| 5 | RTI  | Graphics Core Implementation   | 34 |

|   | 5.1  | Architecture and Features      | 34 |

|   | 5.2  | Implementation                 | 36 |

|   |      | 5.2.1 Graphics Processing Unit | 36 |

|   |      | 5.2.2 Memory Interface         | 39 |

|   |      | 5.2.3 Video Interface          | 41 |

|   |      | 5.2.4 Rasterizer               | 42 |

|   | 5.3  | Summary                        | 46 |

| 6 | Driv | ver and API Implementation     | 47 |

|   | 6.1  | Architecture and Features      | 47 |

|                           | 6.2   | Hardw   | vare Command Interface        | . 49 |

|---------------------------|-------|---------|-------------------------------|------|

|                           |       | 6.2.1   | Memory Management             | . 49 |

|                           |       | 6.2.2   | Graphics Driver               | . 50 |

|                           | 6.3   | OpenO   | GL Implementation             | . 51 |

|                           |       | 6.3.1   | State Management              | . 52 |

|                           |       | 6.3.2   | OpenGL Features               | . 53 |

|                           | 6.4   | Summ    | ary                           | . 55 |

| 7                         | Test  | ting an | nd Results                    | 57   |

|                           | 7.1   | Frame   | buffer                        | . 57 |

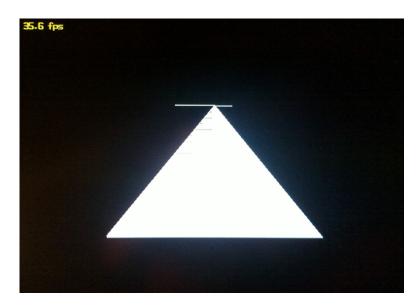

|                           | 7.2   | Simple  | e Triangle Drawing            | . 59 |

|                           | 7.3   | Transf  | formation                     | . 60 |

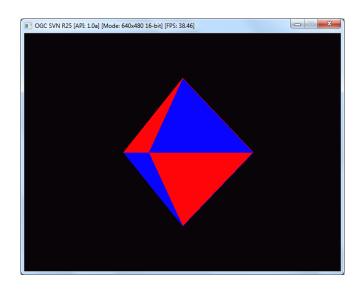

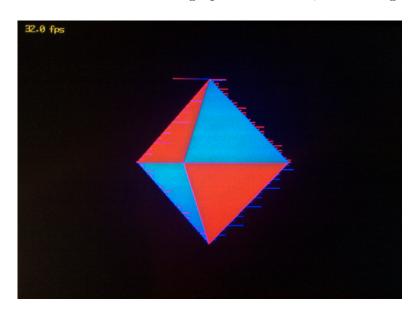

|                           | 7.4   | Color   | Interpolation                 | . 62 |

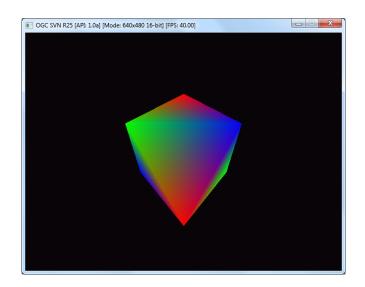

|                           | 7.5   | Lightin | ng                            | . 63 |

|                           | 7.6   | Compl   | lex Mesh                      | . 65 |

|                           | 7.7   | Summ    | ary                           | . 67 |

| 8                         | Con   | clusio  | ns and Recommendations        | 68   |

| R                         | efere | nces    |                               | 71   |

| $\mathbf{A}_{]}$          | ppen  | dix A:  | Hardware Synthesis Reports    | 73   |

| $\mathbf{A}_{]}$          | ppen  | dix B:  | Graphics Accelerator Emulator | 78   |

| $\mathbf{A}_{\mathbf{j}}$ | ppen  | dix C:  | Graphics Formats              | 81   |

| $\mathbf{A}_{\mathbf{j}}$ | ppen  | dix D:  | OpenGL Source                 | 83   |

| $\mathbf{A}_{]}$          | ppen  | dix E:  | Simple OpenGL Demo Source     | 97   |

# List of Figures

| 1  | A high level representation of the graphics pipeline used in realtime rendering | 4  |

|----|---------------------------------------------------------------------------------|----|

| 2  | Illustration of Bresenham's line algorithm                                      | 7  |

| 3  | Wireframe teapot mesh                                                           | 8  |

| 4  | Illustration of the triangle filling algorithm                                  | 8  |

| 5  | Spartan-6 SP605 Evaluation Kit                                                  | 14 |

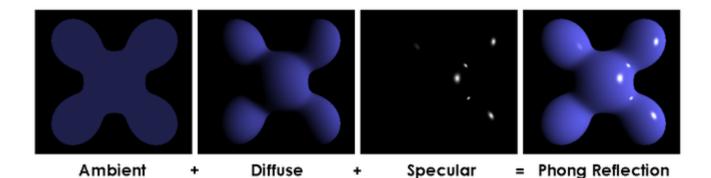

| 6  | Observable Components of the Phong Reflection Model                             | 17 |

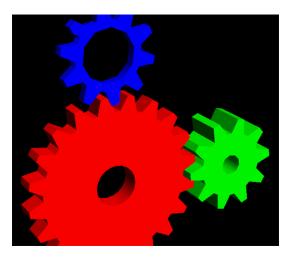

| 7  | OpenGL gears rendered with Mesa 3D                                              | 19 |

| 8  | Vincent3D running on a mobile device                                            | 20 |

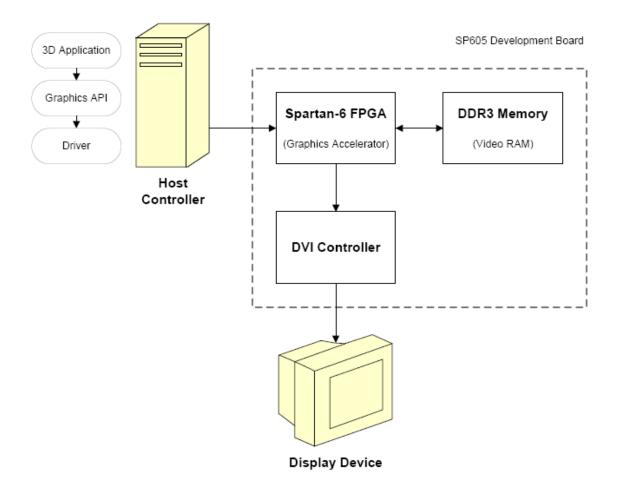

| 9  | System overview                                                                 | 24 |

| 10 | RTL design overview                                                             | 26 |

| 11 | Embedded platform block diagram                                                 | 32 |

| 12 | Hierarchical look at the RTL hardware core architecture                         | 35 |

| 13 | GPU tiered architecture                                                         | 36 |

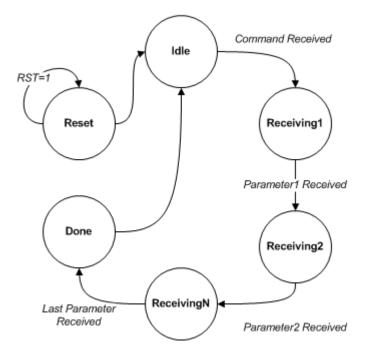

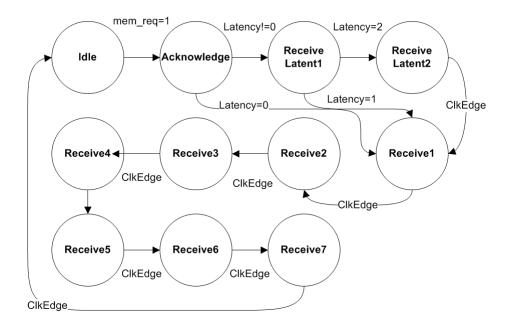

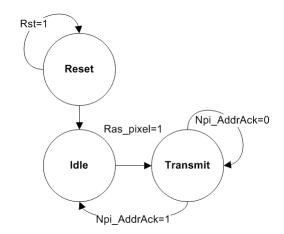

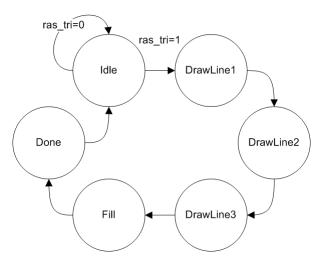

| 14 | GPU command decoder state machine                                               | 38 |

| 15 | Memory Interface state machine                                                  | 40 |

| 16 | Rasterizer pixel write state machine                                            | 43 |

| 17 | Triangle rasterization state machine                                            | 45 |

| 18 | Driver and API data flow                                                        | 48 |

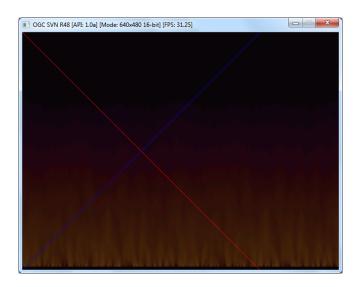

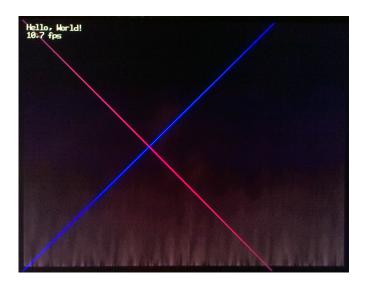

| 19 | Framebuffer demo running in the emulator                                        | 58 |

| 20 | Framebuffer demo running on the FPGA                                            | 58 |

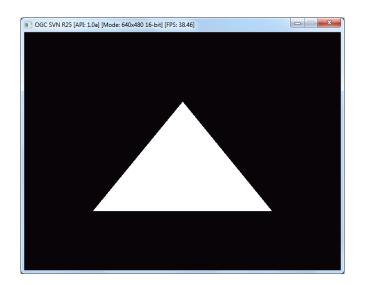

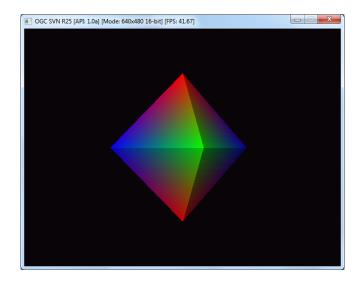

| 21 | Triangle demo running on the emulator                                           | 59 |

| 22 | Triangle demo running on the FPGA                                               | 60 |

| 23 | Transformation demo running on the emulator                                     | 61 |

| 24 | Transformation demo running on the FPGA                                         | 61 |

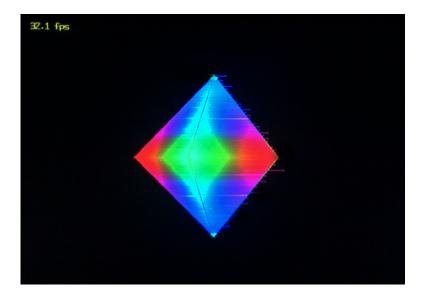

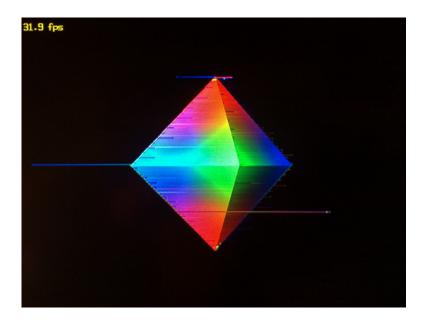

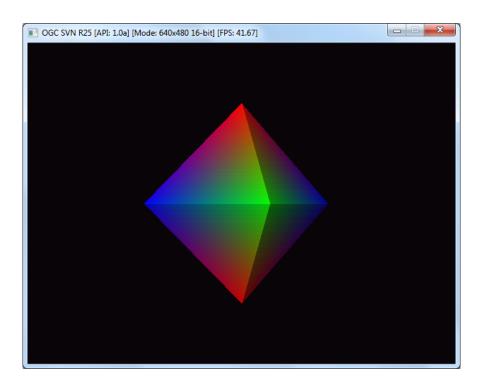

| 25 | Transformation demo running on the emulator  | 62 |

|----|----------------------------------------------|----|

| 26 | Color interpolation demo running on the FPGA | 63 |

| 27 | Lighting demo running in the emulator        | 64 |

| 28 | Lighting demo running on the FPGA            | 64 |

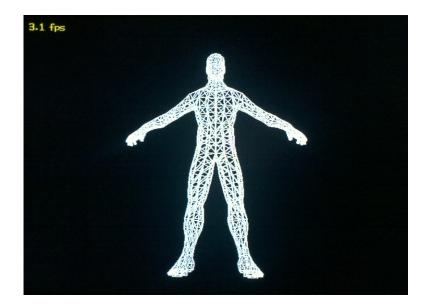

| 29 | Humanoid model rendering on a PC             | 65 |

| 30 | Humanoid mesh demo running on the FPGA       | 66 |

| 31 | Emulator running an OpenGL demo              | 80 |

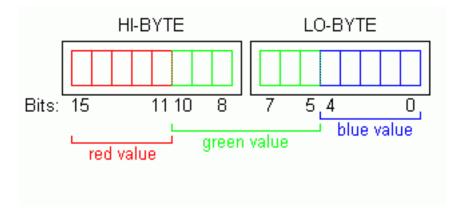

| 32 | RGB565 color encoding                        | 81 |

| 33 | X32 number encoding                          | 82 |

## List of Tables

| 1 | The major components of the design requirements | 22 |

|---|-------------------------------------------------|----|

| 2 | Command parameter decodings                     | 39 |

| 3 | VGA timing signals                              | 41 |

| 4 | Graphics hardware memory management             | 49 |

| 5 | Hardware register memory map                    | 49 |

| 6 | Graphics hardware FIFO commands                 | 50 |

| 7 | Graphics hardware driver functions              | 51 |

| 8 | Implemented OpenGL states                       | 52 |

| 9 | OpenGL Function Implementations                 | 53 |

## 1 Introduction

When considering the growing popularity of a wide variety of mobile and embedded devices capable of three-dimensional (3D) graphics, it's prudent to consider the direction of the evolution of such devices. Current technology trends have precipitated newer graphics processing units (GPUs) that can produce 3D visualizations on compact and portable devices. These may reside on a single chip and can typically perform advanced 3D rendering techniques, including programmable pixel and vertex processors. As computing technologies have advanced, companies including NVIDIA and Texas Instruments have offered high end graphics systems with increased portability and functionality (with the Tegra and OMAP system-on-chip families, respectively). However, such implementations are only realizable by the few major graphics hardware vendors due to the substantial costs of developing such devices. Furthermore, once such hardware is developed, it may only be further customized or improved with a subsequent generation of chips.

While many devices capable of realizing 3D graphics currently do so through the implementation of application-specific integrated circuit (ASIC) designs, it may be worth considering the implementation of field-programmable gate arrays (FPGA) for future designs of mobile 3D graphics devices. An FPGA design may implement a hardware descriptor language (HDL) and may be fully configurable, making this option appealing to developers. Because the FPGA is a relatively small and powerful type of chip, its applications are intrinsically scalable and portable. These characteristics make the FPGA ideal for mobile and embedded devices. Furthermore, the use of parallel processing on the FPGA is conducive to applications such as graphics rendering. For these reasons, implementing FPGA designs to realize the rendering of 3D graphics in mobile devices could potentially herald great advances over current ASIC technology.

Research into an FPGA-based 3D graphics platform has yielded some new promising undertakings, but none of these had been fully developed and distributed to consumers. One such of these projects, Vincent 3D, had attempted to develop an open source implementation of the OpenGL ES API family with some success. However, at this time, Vincent 3D had only implemented a few components of the 3D graphics pipeline in HDL, with the majority of the API implemented as much slower software rendering. Another such project, Manticore, attempted to implement a 3D graphics accelerator on an FPGA, with complete triangle rasterization and VGA output. However, development on Manticore had completely ceased, leaving the project lacking even the most basic but essential abilities of a 3D accelerator.

In this project, we described and tested an FPGA-based 3D graphics accelerator design. With this design, we implemented various stages of the graphics pipeline and its necessary subsystems on an FPGA using hardware descriptor languages. These stages included command and vertex processing, primitive setup, color shading, triangle rasterization, and video output. Taking advantage of the FPGA's parallel processing, various advanced 3D mathematical algorithms were executed in parallel to rendering operations on a separate Microblaze softcore microprocessor. We used a double-buffering based approach to implement smooth, animated visualizations to an output display device via the Digital Visual Interface (DVI). Finally, we adapted a graphics API from the OpenGL specification. This implementation allowed for communication with the 3D graphics hardware via a platform-independent device driver. Within this software layer, we also implemented the Phong lighting model using the hardware's color shading abilities.

Through the completion of this project, we made significant contributions to the development of a complete 3D graphics platform on an FPGA. We met our goal of realizing 3D graphics output using a single chip with a platform that is both configurable and portable. However, time and resource constraints on the project resulted in several performance flaws. These shortcomings primarily included the implementation of the graphics perspective transformations on a softcore microprocessor rather than using HDL. With additional development time, a complete hardware implementation of these transformations would have yielded a substantial performance increase. Future work on this project could also include implementing the lighting model and more complex rendering techniques in hardware for optimal performance.

The remainder of this report first provides the reader with background research (Chapter 2) in the relevant areas of graphics processing and algorithms, FPGA technology, and related work. Chapter 3 then describes an overview of the project including goals, objectives, and a high level design. Chapter 4, 5, and 6 discuss the details of the embedded platform, the hardware graphics core, and the software and driver components of the project, respectively. Chapter 7 describes system testing and results. Chapter 8 contains the conclusions we drew about the process we used as well as our recommendations for

future work. Finally, Chapter 8 contains our analysis of the opportunities to apply the knowledge we gained through realizing this system. Following the body of the report, the appendices contain additional technical information such as selected source code that support the project, but were too large to include as inline elements in the main text.

## 2 Background Research

In order to formulate an appropriate design, it was vital to understand the current state of portable graphics hardware and technology. This chapter discusses the graphics pipeline both in concept and with specific details about implementing it with an FPGA.

#### 2.1 Graphics Rendering Pipeline

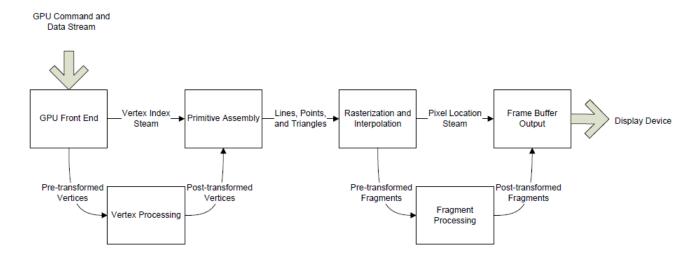

The graphics rendering pipeline traditionally refers to an abstraction for the process which modern Graphics Processing Units (GPUs) use to produce visualizations. Computer graphics hardware typically implement six stages within the pipeline and often various substages within these. At a very basic level, these six stages in sequence are: (1) the front end, (2) vertex processing, (3) primitive assembly, (4) rasterization and interpolation, (5) fragment processing and (6) frame buffer output. These stages all run in parallel, however it is important to note that vertices pass through each of them sequentially. *OpenGL*, a standard specification defining a cross-platform computer graphics API, implements the graphics pipeline as seen in the figure below:

Figure 1: A high level representation of the graphics pipeline used in realtime rendering (Source Adapted from: NVIDIA Cg User's manual, 2010)

This figure shows all of the major components of the graphics rendering pipeline for modern graphics hardware. This pipeline typically starts at the front end, where commands and vertices are sent from a host system. The graphics data will then filter through the pipeline, while the hardware performs necessary processing and transformation to produce raw displayable data. The graphics commands control how each stage conducts these processes and transformations. The output of this system is an image updating in real time that can be drawn by a display device. This section describes the high level functionality of these stages, and how they interact with each other.

#### 2.1.1 Front End

The front end of graphics hardware provides the necessary interface for all commands and data sent to the GPU. This block typically consists of a number of basic layers: (1) a device driver on the host system, (2) a hardware interface physically connecting the GPU to the host system, and (3) a command processor that receives and decodes commands and data from the hardware interface. After this third layer, decoded commands and data are then used to define the operations of the GPU and render visualizations by distributing them to the other components within the graphics hardware. This may be implemented with only a write interface, but it is often advantageous to have certain read signals, for example, to initiate an interrupt request upon the completion of each frame drawing.

#### 2.1.2 Vertex Processing

In 3D graphics processing, a vertex is typically specified in the form of an (x,y,z) triple as a discrete position within the 3D coordinate system. These are often accompanied by many other parameters and vectors, representing such data as shading color, texture coordinates, or normal direction. The vertex processing block is responsible for decoding this data received by the GPU and preparing them to be assembled as primitives and then rasterized. The vertex positions must be transformed from their 3D coordinates into 2D space as approximated by a display device for this to be done. This occurs in two distinct transformation phases. In the first phase, the *modelview* transformation, vertices are transformed within the 3D coordinate system, thus providing hardware accelerated rotation, translation, and scaling of objects.[11, 13] In the second phase, *perspective* transformation, vertices are transformed to be drawn as they appear on a 2D plane from the viewer's perspective.

#### 2.1.3 Primitive Assembly

A primitive consists of one or more vertices to form a point, line, or closed polygon. This stage takes the perspective-transformed vertices from the vertex processing stage and groups them into primitives.[14] In the stage immediately following primitive assembly, primitives are clipped to fit just within the viewport or view volume and then prepared for rasterization to the display device, typically within some form of buffer.

#### 2.1.4 Rasterization and Interpolation

In computer graphics, a raster image is a 2D array of discrete pixels that represent intensity samples.[13] As such, *rasterization* is the stage within the graphics rendering pipeline where a 2D image is generated from transformed primitive data. More formally, rasterization is defined as converting a line drawing, mathematical expression in space, or a 3D scene into intensity values of a group of pixels to be written to the frame buffer, which is then propagated to an output device. As part of rasterization, *interpolation* is the process of constructing intermediate data points in the form of color intensity values within the interval connecting two vertices.[5] Interpolation is necessary in computer graphics for generating vertex colors and fog, among other effects.

There are two main challenges that designers often face when creating a rasterizer: (1) determining the pixel(s) that accurately describe the current primitive being rendered, and (2) efficiency.[13] For this project, rasterization of primitives is limited to simply points, lines, and triangles. This section describes ideal algorithms for rasterizing these, as well as proper methods of clipping and Z-buffer generation.

**Points** In rasterization, point primitives represent a single pixel drawn to the framebuffer. Points are rasterized by writing the pixel's color to the framebuffer memory at the address specified by the pixels X- and Y-coordinates. This is expressed as the equation:

$$Address_{pixel} = BaseAddress_{framebuffer} + (y_{pos} * Width_{framebuffer}) + x_{pos}$$

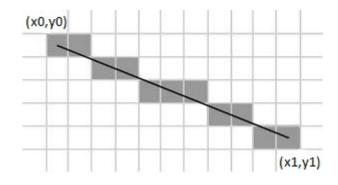

**Lines** Line primitives are two points on the framebuffer connected by the pixel approximation of a straight line. One of the more common and simple methods for ras-

terizing a line is Bresenham's algorithm, which is able to correctly approximate a line primitive.[13][6] This algorithm computes a line starting at a pixel at location (x0, y0) and approximates subsequent pixels downward until reaching the ending location, (x1, y1). The algorithm is initially defined for the first *octant* (the first of eight divisions of a 2D coordinate system) such that the line extends downward and to the right. As such, seven separate versions of the algorithm must also be implemented to rasterize a line within the remaining seven corresponding octants. The illustration below shows a line approximation computed by Bresenham's algorithm.

Figure 2: Illustration of Bresenham's line algorithm (Source: http://www.jobscochin.com/introduction-computer-graphics-algorithms, 2010)

Bresenham's line algorithm selects the next pixel integer Y-coordinate that is closest to the fractional Y- for the same X-coordinate. Successively, Y- can as such remain the same or increase by one. Pixels chosen by Bresenham's algorithm are then rasterized to the framebuffer as point primitives.

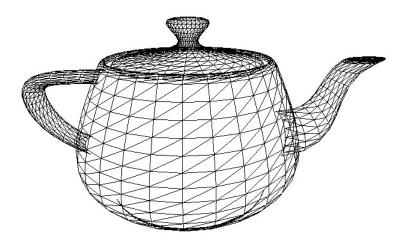

**Triangles** Triangles are the base primitive for rendering complex 3D meshes. An example of how a complex mesh can be constructed from simple triangle primitives can be seen in the figure below.

Figure 3: Wireframe teapot mesh (Source Adapted from: http://caig.cs.nctu.edu.tw/course/CG2007/, 2007)

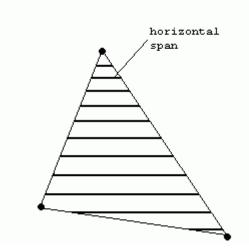

One very simple method of rasterizing a triangle can be performed by first computing the wireframe of the triangle (three connected lines). This can be done by connecting the three vertices of a triangle using Bresenham's Line Algorithm and saving the Xcoordinate, Y-coordinate, and color value for each pixel in that wireframe. Next, the triangle wireframe can then be filled by using a scan line rasterization algorithm to draw horizontal lines across the triangle (with the saved pixel data) for each vertical pixel in the triangle wireframe. Figure 4 illustrates this concept below.

Figure 4: Illustration of the triangle filling algorithm (Source: http://www.devmaster.net/articles/software-rendering/part3.php, 2004)

Consequently, all primitive rasterization stems from the ability to put a single pixel in the

framebuffer - point rasterization. Line rasterization can then be performed by successive points, and triangle rasterization can be performed by successive lines. Complex scenes can then be constructed by rasterizing a series of triangles.

#### 2.1.5 Frame Buffer

After the GPU has produced a synthesized image and performed on it the necessary pixel transformations, the pixels are stored in an image buffer - the *frame buffer*. As its name suggests, the frame buffer stores the current "frame" to be rendered, in an animation sequence.[13] This intermediate storage between the graphics pipeline and the output display is necessary because the two are not synchronized with each other. Displays are typically clocked, which depend on both the display resolution and refresh rate. Display updates are synchronous processes that perform continuously and sequentially by a constant clock signal. The GPU conversely produces data asynchronously in a manner depending on the CPU sending it data or commands.

The frame buffer for a graphics accelerator is generally either pre-allocated in a systems main memory, or in a dedicated memory device onboard the graphics accelerator. Specifically, with realtime graphics systems, the frame buffer is where all pixel color data from rasterization is stored before being drawn to the display. Furthermore, this is necessary because rasterization is performed on primitives and there is no guarantee that the rasterized primitives are actually drawn to the display.[13] For simplicity and efficiency, pixel color data within the framebuffer is typically encoded in a format most compatible with the input signals of the display device.

Many issues can arise due to the conflict between a GPU's sporadic access to the frame buffer and the display device's sequential access. First and foremost, it is likely that the display device will begin reading a *scanline*, the a horizontal pixel line traced by a display's rasterbeam, before the GPU has finished drawing it.[13] An ideal solution to this problem would be for the output circuit of the graphics accelerator to wait for the rendering of a frame to be completed before starting to read the frame buffer. However, this is not possible because the output image must be updated at a very specific rate that is independent of rasterization time.

The solution to this problem is to introduce *double buffering*, which is the use of two frame

buffers by the GPU.[13, 6] The first frame buffer, the back buffer, is used for writing only from the rasterizer and therefore may accept data liberally. The second framebuffer, the front buffer, is used only for reading from the output circuit, and can therefore be read sequentially and independently from the time at which data is written. When the current frame is finished rendering to the back buffer, the two buffers then switch their positions and the next frame is drawn. This mechanism prevents the buffer currently being drawn from ever being overwritten.

Basic double buffering may fail to prevent all frame buffer-related artifacts. The most common of these, *tearing*, occurs when the buffers swap before the sequential reading of the front buffer has completed the frame.[13] This results in some lower portion of the display coming up a frame ahead of the upper portion. Tearing may be avoided by only swapping the buffers in the refresh interval, the vertical blank count (VBLANK), between the previous and next frames. Swapping during the VBLANK period, however, introduces potentially significant latency in this process. On many modern graphics accelerators, this is a setting that can be disabled in order to maximize speed.

#### 2.2 3D Mathematics

Graphics accelerators exist to perform the mathematical calculations that render 3D visualizations more efficiently than computer CPUs. These mathematics are often complex as they provide all of the necessary routines to build a 3D scene and animate it as needed. This section describes the fundamental concepts of these operations, as well as the necessary considerations for implementing such routines on an FPGA.

#### 2.2.1 Transformation

Modern computer graphics accelerators typically take advantage of highly optimized math co-processors to perform floating point transformations of objects in 3D space. Transformation is divided into two categories. The first of these is *modelview* transformation, which provides the necessary operations to translate, rotate, and scale objects.[5] The second of these is *perspective* transformation, which transforms objects in 3D space so that they will appear on a 2D display as if they were being viewed from the camera's perspective. All of these transformations are implemented as matrix multiplications with specially defined scale, rotate, translate, and perspective matrices.

In a modelview transformation for 3D objects, quaternions given as four-by-four matrix specify the movements of each vertex in a homogeneous coordinate space.[5] Although a vertex represents an imaginary point in space with no visible size, the notion of scaling its position refers to the modification of the distance from the origin to that point. For example, the distance of a point along a single axis at position 2 scaled by a factor of 2 would result in 2 \* 2 = 4. In 3D space, a point specified by an ordered triple (x, y, z) may be scaled by the matrix:

$$T = \begin{bmatrix} S_x & 0 & 0 & 0\\ 0 & S_y & 0 & 0\\ 0 & 0 & S_z & 0\\ 0 & 0 & 0 & 1 \end{bmatrix}$$

where each S value corresponds to the factor by which each distance value will be scaled. A given vertex will be scaled by the multiplication:

$$T = \begin{bmatrix} S_x & 0 & 0 & 0 \\ 0 & S_y & 0 & 0 \\ 0 & 0 & S_z & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} * \begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} S_x x \\ S_y y \\ S_z z \\ 1 \end{bmatrix}$$

In a vertex rotation, the vertex is typically rotated about one of the axes of the coordinate space. The transformation matrix used to rotate each vertex is dependent upon the axis used for the rotation. For example, a rotation of n degrees counterclockwise about the x-axis, called an x-roll, is given by the transformation matrix:

$$T = \begin{bmatrix} \cos(n) & -\sin(n) & 0 & 0\\ \sin(n) & \cos(an) & 0 & 0\\ 0 & 0 & 1 & 0\\ 0 & 0 & 0 & 1 \end{bmatrix}$$

Finally, vertex translation is accomplished by specifying the vector by which the vertices are translated in the rightmost column in the transformation matrix. To translate a vertex by the vector  $[T_x, T_y, T_z]$ , one may use the following transformation matrix:

$$T = \begin{bmatrix} 1 & 0 & 0 & T_x \\ 0 & 1 & 0 & T_y \\ 0 & 0 & 1 & T_z \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

Using this combination of *affine* transformations as they are called, one may describe any movement or reshaping of vertices in a 3D space.[5] In 3D graphics using 2D display devices, however, it becomes necessary to simulate the third dimension or axis through a series of *perspective transformations*. Using perspective projection, objects far away from the viewer will have a smaller projection and objects close to the viewer will have a larger projection. A perspective projection is defined by a series of parameters that define the dimensions of the view volume: l and r as the left and right boundaries, b and t as the bottom and top boundaries, and n and f as the near and far boundaries, respectively. The following transformation matrix is valid as long as  $l \neq r$ ,  $b \neq t$ , and  $n \neq f$ :

$$T = \begin{bmatrix} \frac{2n}{r-1} & 0 & \frac{r+1}{r-1} & 0 \\ 0 & \frac{2n}{t-b} & \frac{t+b}{t-b} & 0 \\ 0 & 0 & \frac{-(f+n)}{f-n} & \frac{-2fn}{f-n} \\ 0 & 0 & -1 & 0 \end{bmatrix}$$

By combining these affine and perspective transformations, graphics software and hardware may convert mathematical data in the form of 3D vertices into a 2D mapping of objects that faithfully represent a scene in space.

#### 2.2.2 Fixed-Point Computations

Floating-point units (FPUs), the components of CPUs used to natively perform arithmetic operations on floating point numbers, are often unavailable on FPGAs and are few and far between on low-power micocontrollers and microprocessors. In these cases, floating point math may be implemented in software, or simply not used at all. On such devices, acceptable computational performance may be achieved using fixed-point arithmetic operations for 3D mathematics rather than using a software-defined FPU.[9][8] With fixed-point arithmetic, the decimal point of a number is "fixed" before a specific digit. For example, during integer math, the decimal is placed after the least significant bit (LSB), meaning that there is no memory allocated for a possible fraction.[9] In this scenario, the fraction is discarded and the result of a computation is rounded to whole numbers. However, it is possible to fix the decimal point at a different position within the number. This allows for fractions to be represented, even if they are still just rounded approximations. With this form of number representation, math can be done by a traditional arithmetic logic unit (ALU) and 3D vectors may still be approximated enough to render realistic visualizations. This incorporates simple integer math, along with some additional steps to account for the decimal point position.

For the application of 3D mathematics, it is seldom ideal to represent fixed numbers with equal allocation for both whole numbers and fractions.[9]This is due to the frequent need for a signed most significant bit (MSB), which constrains the integer component of the number. Instead, a format such as 18.14 or 17.15 (in the format M.N, where M represents the integer component in bits and N represents the fractional component in bits) is often much more effective for 32-bit 3D fixed-point math.[15] For 16-bit math, the format 10.6 is ideal to ensure a substantial enough integer component.

#### 2.3 Target Platforms

This project required two concentric platforms: the FPGA development board upon which the system was developed, and the embedded system that served as the host device, which utilized the graphics accelerator to render 3D visualizations. This section identifies the selected platforms and discusses how the selected devices met the needs of the project.

#### 2.3.1 Spartan-6 FPGA and SP605 Evaluation Kit

The Spartan-6 is the latest iteration of Xilinx's Spartan family of low-cost, low-power FPGAs. Xilinx, the leading FPGA manufacturer, has designed the Spartan 6 with high performance and cost-sensitive applications in mind.[2] Using 45nm, 9-metal copper layer, dual-oxide process technology, the Spartan 6 includes advanced power management and memory support, among other features. The selected XC6SLX45T-FGG484-3C FPGA includes 150,000 logic cells and supports integrated hard memory, block RAM, high performance clocking and serial IO, and an integrated PCI-Express (PCI-E) endpoint block.

The Spartan-6 LTX is Xilinx's ideal offering for FPGA-based graphics acceleration as it balances both price-point and the resources necessary for GPU computations.

The SP605 Evaluation Kit enables developers to easily prototype designs with the XC6SLX45T FGG484-3C Spartan-6 FPGA. The kit includes all the basic components of the Xilinx Base Targeted Design Platform in one package. [2] With the SP605, developers can easily take advantage of the features of the Spartan 6. Additionally, the kit includes DVI video output, a 200MHz oscillator, 128MB of DDR3 memory, and various expansion connections. The figure below shows the SP605 board.

Figure 5: Spartan-6 SP605 Evaluation Kit (Source: http://www.xilinx.com/products/devkits/EK-S6-SP605-G.htm, 2010)

The support for the Spartan-6 LXT FPGA, digital video output interface, and 200MHz clock all made the SP605 an appropriate choice for FPGA-based graphics acceleration. Additionally, its support for PCI-E created an additional advantage for potential applications in a desktop PC environment.

### 2.4 Graphics Application Programming

Developing graphics applications necessitates the consideration of portability. A graphics acceleration system must provide an accessible interface to allow its users to develop high-level programs that are easily maintained and may potentially be ported to and from other systems.

#### 2.4.1 OpenGL

OpenGL is an open source graphics library originally developed specifically to enable device-independent graphics programming. Its free and open nature combined with its widespread use in industry and academia additionally have made it an ideal choice for many computer graphics systems. [6]

As an Applications Programming Interface (API), OpenGL specifies a library of functions and data types that interact together to enable a wide range of simple or complex computer graphics applications. Its definition as an interface provides developers with a powerful basis to structure a graphics system while providing users with flexibility and the assurance that their application may be compiled and run on any two OpenGL-compliant systems. In this way, the user has access only to the interface and need not consider the underlying graphics driver or hardware. The developers, in turn, need only focus on rigorous compliance to the standard rather than providing support for users of a graphics driver. In this way, such an interface is a valuable tool to both developers and users.

#### 2.4.2 Lighting in OpenGL

OpenGL provides the tools to develop many visual effects to enhance the images attainable with basic modeling. Among these features is the capability for lighting in scenes rendered by OpenGL as a means of increasing scene realism and enriching the viewer experience. Lighting effects are accomplished in OpenGL through the use of shading models. The shading model or *shader* describes how light is scattered or reflected from a surface. [6][11]

Most shaders use two types of light sources to illuminate objects in a scene: *incident* and *ambient* light sources.[11] While incident light sources model the physical behavior of light in the real world, ambient light sources simulate the seemingly nondirectional background light that is difficult and expensive to model accurately. Ambient light may also be considered to be the background glow in the surrounding environment. [6]

In OpenGL implementations of 3D lighting, there are two categories of incident light:

• *Diffuse scattering*, which describes the effect of light slightly penetrating a surface and radiating uniformly in all directions. Since the light has such a strong interac-

tion with the object's surface, the qualities of the surface material, such as color, are very important to this effect. Reflections from diffuse scattering are independent of the position of the viewer in relation to the surfaces or lights.[6]

• Specular reflections, which describe the mirror like reflections of light off of an object's outer surface. This effect produces bright highlights on a surface and suggests a shiny quality. In general, the color of the highlights observed on a surface are determined by the color of the light rather than the color of the surface. Reflections from specular highlights are inextricably related to the position of the viewer in relation to the surface and light sources.[6]

In general, most objects in a scene will include varying levels of both diffuse and specular reflections. The specific amounts of each reflection type depend upon the material properties defined as part of the scene. [6][11]

Ambient light is included in shading models address the inability of diffuse and specular reflection to accurately simulate background light in an environment. When considering the effects of only incident light on a scene, any unaffected surface will appear totally black. This creates deep shadows on objects that give the scene a harsh look. Ambient light is therefore used to provide an approximation of the light that is reflected from many directions from many different surfaces in the scene. This effectively provides a soft glow that acts on all objects in a scene and provides a more realistic effect.[6][11]

#### 2.4.3 Mathematics of Lighting

To apply the shading model to a scene, a series of calculations are performed upon each user-defined vertex in the scene based on the lights' properties as objects in the scene, the vertices' positions, colors and orientations and the camera's position and orientation in the scene. The color of a vertex is a simple sum of the lighting contributions for all lights, i, acting on it:

$$Vertex \ color = \sum_{i}^{lights} (ambient_i + diffuse_i + specular_i)$$

Each lighting component, as seen in the figure below, has a unique effect on the scene.

Figure 6: Observable Components of the Phong Reflection Model (Source: http://en.wikipedia.org/wiki/File:Phong\_components\_version\_4.png, 2010)

Ambient lighting is mathematically the simplest of these components since it acts as a linear scaling effect on the vertices' material properties.[6] The ambient light contribution is a simple product of the ambient material color and the ambient light value:

#### $Ambient \ contribution = ambient_{light} * ambient_{material}$

Diffuse lighting intensity depends on the dot product of the unit vector pointing from the vertex to the light position,  $\mathbf{L}$ , and the unit normal vector of the vertex,  $\mathbf{n}$ . If the dot product is negative, then the vertex is not acted upon by diffuse light and the diffuse component is 0 by default.[6] The diffuse lighting component for each light is thus defined as:

$$Diffuse contribution = diffuse_{light} * diffuse_{material} * max (\mathbf{L} \bullet \mathbf{n}, 0)$$

Similarly to the diffuse component, the specular component only applies if the dot product of the light and normal vectors is greater than zero. The specular term is further dependent upon the dot product of normalized sum of the light and view vectors,  $\mathbf{s}$ , and the unit normal vector,  $\mathbf{n}$ . This sum is then raised to the power of a user-defined term, shininess, which is a number between 0 and 128 that controls the focus of the specular highlight.[6]

$$Specular contribution = \begin{cases} specular_{light} * specular_{material} * (max (\mathbf{s} \bullet \mathbf{n}, 0))^{shininess} & \mathbf{L} \bullet \mathbf{n} > 0 \\ 0 & \mathbf{L} \bullet \mathbf{n} \le 0 \end{cases}$$

These contributions are then added together to define the final vertex color. According to the Phong model, the colors of the intermediate pixels between these vertices may be determined by a variety of shading or interpolation methods. One method of coloring objects in the scene is on a *per-vertex* basis, that is, each pixel's color in the displayed scene is determined by lighting through linear interpolation of colors from vertex to vertex. Given the 2D coordinates and the color value of two vertices, the *color slope* between them is defined as:

$$m = \frac{\Delta C}{\Delta X}$$

where  $\Delta C$  specifies the change in color values and  $\Delta X$  specifies the change along the independent axis (i.e. X-axis for mostly horizontal lines or Y-axis for mostly vertical lines). Using this color slope, the formula of a line functionally determines each intermediate point's color value as follows:

$$y = mx + b$$

where y is the intermediate color value, x is the independent axis position and b is the color value of the first or "source" vertex taken in the interpolation.

#### 2.5 Related Work

Several projects have attempted to implement the OpenGL specification and computer graphics pipeline as discussed in this chapter. However, the majority of these have consisted primarily of software implementations rather than FPGA-based implementations. This section discusses a few of these related works.

#### 2.5.1 Mesa 3D

Mesa is an open-source implementation of the OpenGL specification, providing a system of rendering interactive 3D graphics[1]. Originally started in 1993 by Brian Paul, Mesa has evolved to a very comprehensive set of libraries used in a variety of device drivers, software emulators, and modern GPUs. In addition to being cross-platform, Mesa has been one of the most advanced and complete implementations of OpenGL. However, Mesa consists entirely of a software implementation, which would be much slower than a potential hardware implementation (on either an ASIC or an FPGA). At the time of this project, Mesa had implemented the complete OpenGL 2.1 specification, as well as various extensions from OpenGL 3 and 4. The figure below shows a scene rendered entirely by the Mesa 3D library.

Figure 7: OpenGL gears rendered with Mesa 3D (Source: http://www.icewalkers.com/Linux/Software/534890/Mesa3D-for-MiniGUI.html, 2010)

#### 2.5.2 Vincent 3D

The Vincent 3D Rendering library, like Mesa, is an open source graphics library that implements the OpenGL specification. However, unlike Mesa, Vincent instead had implemented the OpenGL ES 1.1 API specification, published by the Khronos Group[3]. While Vincent had recently shifted its focus to various HDL implementations of the graphics pipeline, at the time of this project the current release of Vincent was entirely software-based. Like Mesa, this made the project much slower than a potential hardware implementation of a graphics accelerator. Figure 8 shows a visualization produced by the Vincent 3D renderer on a mobile device.

Figure 8: Vincent3D running on a mobile device (Source: http://www.vincent3d.com/software/software.html, 2010)

#### 2.5.3 Manticore

The Manticore project was an attempt at an open source hardware design for a 3D graphics accelerator written entirely in VHDL[4]. At the time the project was discontinued, Manticore was capable of triangle rasterization, framebuffer support, VGA support, and an SDRAM controller. This implementation was tested on a Altera APEX20K200E FPGA[4]. However, while Manticore was one of the earliest and only strictly HDL implementations of a 3D graphics core, it never implemented enough of the graphics pipeline to render a complete 3D scene. The project has not been updated since 2002.

#### 2.6 Summary

The main purpose of this chapter was to present the background research of elementary 3D graphics processing. Furthermore, the necessary information to implement these graphics principles and algorithms on an FPGA were also discussed. The next chapter (Chapter 3: Project Overview and Design) discusses goals, objectives and a high-level design of the project.

## **3** Project Overview and Design

This chapter presents a general overview of the project, discussing its goal and the objectives that had to be met. Additionally, this chapter presents a high level design, describing how we implemented the project's various components and met the design requirements.

#### 3.1 Goal

The main goal of this project was to implement a portable graphics accelerator on an FPGA. This device needed to provide single-chip 3D graphics acceleration for low-power and space-conscious environments, such as with mobile and embedded systems. Implemented in Hardware Description Language (HDL), this accelerator need to be entirely open and configurable, providing a graphics system that could be easily adapted or optimized for specific system requirements.

#### 3.2 Objectives

To achieve the goal of this project, three primary objectives had to be met. The graphics accelerator needed to:

- Provide a fast and simple input interface

- Generate an image at reasonable speeds from graphics data

- Provide a display output interface

These objectives were completed through the design and implementation of a number of subsystems.

The first objective was to interface with other systems that needed to display graphics. The device needed to easily connect to other systems through a standard input/output (I/O) format, wherein it would use an easy and intuitive means of communication.

The second objective was to rasterize a two-dimensional (2D) image from the three dimensional (3D) data provided by another system. This needed to be accomplished efficiently because many images needed to be generated per second to produce smooth animated visualizations. Consequently, the device needed to use optimal algorithms to perform these operations.

The third and final objective was to provide a means to display the generated image. This needed to adhere to a standardized display format, allowing the graphics accelerator to be used with many different platforms. Also necessary were an output connection and the underlying hardware controller for the selected format.

### 3.3 Design Requirements

| Input Interface    | Provided a cross-platform interface for graphics             |

|--------------------|--------------------------------------------------------------|

|                    | commands and data.                                           |

| Graphics Processor | Decoded, transformed, and rasterized 3D primitive data       |

|                    | to a 2D pixel buffer.                                        |

| Output Interface   | Implemented a standardized display output.                   |

| Device Driver      | Provided the interface between software and the graphics     |

|                    | hardware.                                                    |

| Graphics API       | Abstracted the driver interface to a cross-platform graphics |

|                    | programming specification.                                   |

The design for this project included five subsystems. These systems and their responsibilities are described in the table below.

Table 1: The major components of the design requirements

Each subsystem had its own specific requirements. The *input interface* provided a communication connection for graphics commands and data to the accelerator. This hardware implemented the link between a host system and the the graphics processing unit (GPU). This interface needed to be independent of the platform used with the accelerator, adhering to a known and standardized I/O format. This format needed to transfer graphics commands and data at a fairly high rate such that 3D visualizations could be realized at smooth frame rates.

The graphics processor needed to render 3D primitive data to 2D space and was fulfilled by the functional implementation of a GPU. The GPU implemented the 3D graphics pipeline and all of its components. The GPU received encoded commands and data from the input interface and decoded these and their required parameters. Next, it performed necessary modelview and perspective transformations on them and rasterized the result to a pixel buffer. These components needed to run efficiently and integrate seamlessly with the desired input and output devices. The GPU needed to also implement optimal rasterization and transformation algorithms that run in parallel to each other and achieve the highest possible speeds for the target platform. The *output interface* needed to implement a standardized display output format, providing the interface between the GPU and a target output device. This interface implemented a digital video out standard ensuring that it could be used for multiple different displays. This required a hardware implementation of the display format controller to generate necessary output signals.

The *device driver* needed to provide the software interface between the graphics API and the hardware input interface. The device driver implemented the defined functionality of the API by sending commands and data to the input interface. This driver needed to be compatible with multiple hardware systems by being implemented within a standard driver model.

The graphics API (Application Programming Interface) needed to define an abstraction layer that allowed a user to easily send graphics commands and data to the accelerator from their applications. This API needed to be implemented in a standard programming language and follow a consistent and logical specification. The API implemented all configuration settings of all graphics features of the accelerator. The API needed to also provide an intuitive interface for drawing and manipulating graphical data using the GPU.

#### 3.4 Design

This section describes the overall system design for the project, implementing the requirements previously discussed. The core of the system, the graphics processor and all of its necessary subsystems, was implemented within the Xilinx Spartan-6 LXT FPGA on the SP605 Development Board (described in Chapter 2: Background Research).

To render 3D visualizations, data flowed first from the application, then to the graphics driver, and then to the FPGA. The FPGA performed all necessary processing to rasterize the 3D visualizations to a framebuffer located in memory. Due to project time and resource constraints, certain stages of the transformation (including the lighting and normal transformations) were implemented in driver-space.

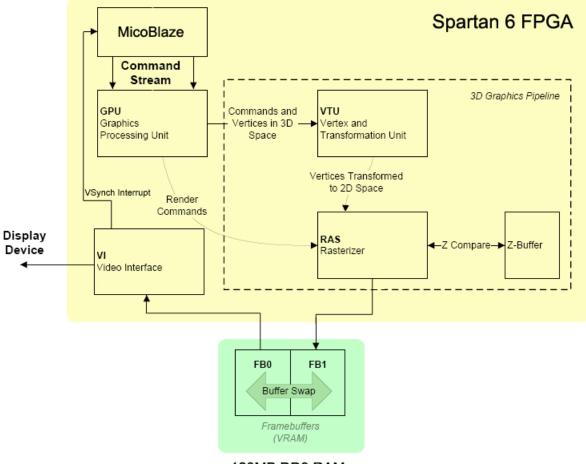

We selected the 128MB DDR3 component memory, located on the SP605, to hold all video memory. This memory synchronously sent framebuffer data to the display device via the SP605's Digital Visual Interface (DVI) control circuitry. Figure 9 provides a simple overall system diagram of the graphic hardware and its input and output interfaces.

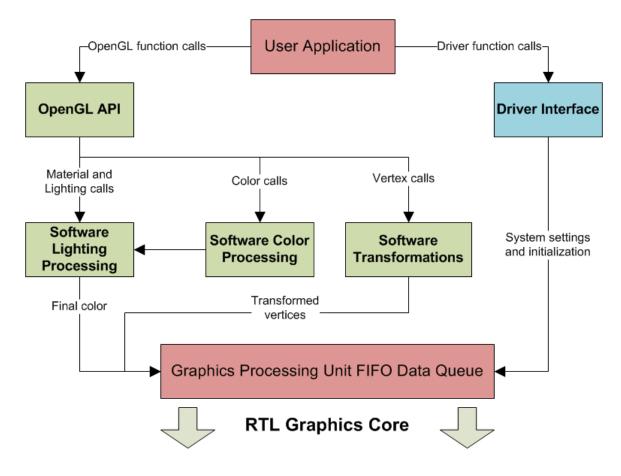

Figure 9: System overview

#### 3.4.1 Software Design Overview

The software design for this project implemented all of the necessary abstractions for an application programmer to render 3D data with the graphics accelerator. This composite system consisted of: (1) the graphics API as a wrapper for (2) the softcore graphics driver commands, and (3) the stages of the graphics pipeline that could not be implemented in hardware. Additionally, the software designs for this project included various test modules whose purpose was to qualitatively and quantitatively benchmark the FPGA-based graphics accelerator, and an implementation of the Phong lighting model.

**Graphics Driver** The graphics driver served as the software interface to the softcore GPU, allowing 3D visualizations to be drawn for an application by invoking a logical and standardized set of functions. In the interest of hardware independence and streamlined use, the system partially implemented OpenGL 1.1 as the graphics API rather than

designing a custom software interface. However, many functions of the OpenGL library had been left out due to missing hardware features. The API itself simply served as a high-level wrapper for users familiar with the widely used OpenGL specification to communicate in terms of the graphics core's instruction set. In this way, the API and the graphics driver comprised an inseparable link between the user's 3D graphics application and the data transfer to the graphics core. The graphics driver also implemented various essential API functions that do not exist within OpenGL, including frame swapping, initialization, and cleanup.

The scope of this project included the implementation of those functions that could be defined within the constraints of the graphics hardware features in addition to several advanced features that serve to extend the capabilities of the hardware. Vertex lighting, for example, would have required complex trigonometric calculations in a hardware implementation that were much more easily handled by the software. The remaining functions in the API were implemented as blank stubs to ensure compatibility with OpenGL applications and to increase the potential for future scalability.

Lastly, certain phases of the hardware modelview and perspective transformation were implemented on a softcore CPU within the driver-space due to RTL limitations on the Spartan 6 LXT. This specifically included the matrix/vector multiplications necessary to calculate 2D screen coordinates from 3D space coordinates, which required signed 48-bit multiplication.

**Test Modules** A series of test modules were written to qualitatively and quantitatively benchmark the graphics hardware. These were written as 3D demos, and performed the following:

- Identified the maximum performance limitations of the graphics hardware, and produced quantified data on these (e.g. triangles-per-second, etc.)

- Implemented test cases to demonstrate and validate each individual feature of the graphics hardware

- Created a final, presentable, 3D visualization that took full advantage of the graphics hardware to produce an animated scene, demonstrating all of the capabilities of the system

### 3.4.2 RTL Design Overview

The Register Transfer Level (RTL) design for the graphics accelerator implemented a number of subsystems to control the various stages of the graphics pipeline and its necessary input and output interfaces. The figure below provides a system diagram for the RTL hardware design of the project. This system performed the necessary steps to render 3D graphics to an output display device from an input command stream provided by a user application.

128MB DD3 RAM

Figure 10: RTL design overview

Commands controlling the graphics accelerator were first pushed into the GPU by the graphics driver over the Processor Local Bus (PLB), followed directly by their relevant parameters or other data. The GPU then dispersed the commands and data to the necessary subsystems, specifically the *Vertex and Transformation Unit* (VTU) and the

*Rasterizer* (RAS). These two units ran in parallel, albeit sequentially on data. Transformed and rasterized data were then read sequentially by the *Video Interface* (VI), which ran independently of the other subsystems, constantly refreshing the output display device signals. An example execution for a program that draws simple 3D primitives with the proposed implementation is as follows:

- 1. Initialization routine

- (a) Set clear color and other state values

- (b) Set viewport

- (c) Set view transformation mode (perspective or orthogonal)

- 2. Draw primitives

- (a) Translate, scale, and rotate the modelview matrix

- (b) Send vertex position and color data

- 3. Wait for vertical synchronization (last frame to finish being displayed)

- 4. Repeat steps 2 and 3 indefinitely

**Graphics Processing Unit** The GPU processed the stream of data and commands (graphics instructions) sent to the graphics accelerator. Acting as the frontend for the entire system, the GPU implemented the various instructions needed to control the states of the remaining subsystems and draw primitive data. These instructions were queued into the GPU by a First-In First-Out (FIFO) buffer, and then decoded and executed sequentially by the GPU. Consequently, the FIFO stored the sequence of instructions to be executed, as well as the necessary parameters these commands provided to the graphics accelerator. The GPU instruction set that defined all control over the graphics accelerator is presented below.

| Name        | Description                                              |

|-------------|----------------------------------------------------------|

| NOP         | No operation                                             |

| DISPCNT     | Sets GPU control register                                |

| DISPSTAT    | Sets GPU status register                                 |

| DRAWDONE    | Denotes the end of a frame being drawn (swaps buffers)   |

| VIEWPORT    | Sets the viewport width, height, and X- and Y- locations |

| CLEAR_COLOR | Sets the clear color                                     |

| PIXEL       | Draws a pixel directly to the framebuffer                |

| VTX_BEGIN   | Begins a vertex list                                     |

| VTX_END     | Ends a vertex list                                       |

| VTX_POS_X32 | Set XYZ vertex coordinates, signed fixed-point 32-bit    |

| VTX_COL_565 | Set RGB vertex color, 565 mode 16-bit                    |

For the graphics accelerator to process a command, the opcode first needed to be sent through the FIFO followed by its necessary parameters. The parameters for each command are discussed in Chapter 5: RTL Graphics Core Implementation.

**Vertex and Transformation Unit** The Vertex and Transformation Unit (VTU) defined two primary subsystems: (1) the Matrix Processor (MP) and (2) the Geometry Processor (GP). All vertex and matrix commands decoded by the GPU were processed by the VTU.

The Matrix Processor implemented all matrix operations and stored two matrices to define how primitives were transformed in 3D space and how 3D space was converted to the 2D viewing window (modelview and projection matrices, respectively). The MP implemented all of its matrix transformations by multiplying the current matrix by another matrix, which could be defined for translation, scaling, rotation, or orthogonal and perspective projection. All matrices were 4x4 32-bit fixed point, with the fractional part in the lower 16 bits (signed 16.16 format).

The Geometry Processor performed all of the necessary routines to prepare incoming vertex streams to be rasterized to the frame buffer. Upon receiving a VTX\_BEGIN command, the GP began processing a vertex list of the specified primitive type (points, lines, or triangles). To do this, the VTU invoked the following sequence of events:

- 1. Upon receiving the VTX\_BEGIN command, the VTU entered geometry processing mode, and could not receive any non-VTX commands until completion

- 2. The VTU then received a VTX\_POS command for the specified X, Y, and Z

vertices of a primitive, and executed the following:

- (a) Transformed the X, Y, and Z vertices of the primitive by the modelview matrix

- (b) Transformed the X, Y, and Z vertices of the primitive by the projection matrix

- (c) Sent the resulting 2D primitive X and Y values to the rasterizer, as well as the last color data specified by the VTX\_COL command

- 3. The VTU then repeated step 2 for the remaining vertices that had been sent to the GPU

- 4. The VTU then exited geometry processing mode upon receiving the VTX\_END command

At the completion of all drawing, the VTU would then wait to be signaled that drawing of the current frame was completed with the DRAWDONE command.

**Rasterizer** The Rasterizer's (RAS) main purpose was to perform all of the drawing to the framebuffer. The RAS performed this in two steps: (1) primitive rasterization, the process of computing the necessary pixels to be written to approximate points, lines, and triangles, and (2) color rasterization, the process of determining the necessary pixel color via interpolation. The core functionality of the rasterizer was the implementation of a line rasterization algorithm, which was then used to draw the other primitives. For example, a single point could be rasterized with a line of length 1, and a triangle could be rasterized by drawing a series of horizontal lines (see Chapter 2: Background Research for discussion on these methods). The rasterizer received data from the VTU and rasterized all vertices to the framebuffer.

Upon completion of rasterization, the rasterizer then waited until the Video Interface entered the vertical blanking period, the time elapsed between two frames being drawn to the display device. During this window, the framebuffers swap addresses, and the new framebuffer is subsequently cleared. The Rasterizer would then proceed to process the next frame upon receiving new data from the VTU. **Video Interface** The Video Interface provided all of the necessary interfacing to the output display device. This primarily included, (1) timing synchronization of the whole system with the display rate, and (2) sequential generation of the RGB signals to the output display device from framebuffer 1. The VI operated completely independent of the entire system on its own 25MHz clock, constantly outputting the data from framebuffer 1 synchronously with the vertical and horizontal timing signals. This resulted in smooth, 60 frames per second (FPS) visualizations. The VI fed back a single active-high control signal to the GPU, indicating when it is in the VBLANK phase, for synchronization purposes. This ultimately triggered the entire system's only interrupt to prevent the CPU from starting to send the next frame of data.

## 3.5 Summary

This chapter discussed the goals and objectives of this project. Furthermore, a high level design of this project was detailed. In the next chapter (Chapter 4: Embedded Platform Implementation) the hardware design and implementation of the embedded platform is described. It focuses on how the graphics core was implemented within an embedded system.

# 4 Embedded Platform Implementation

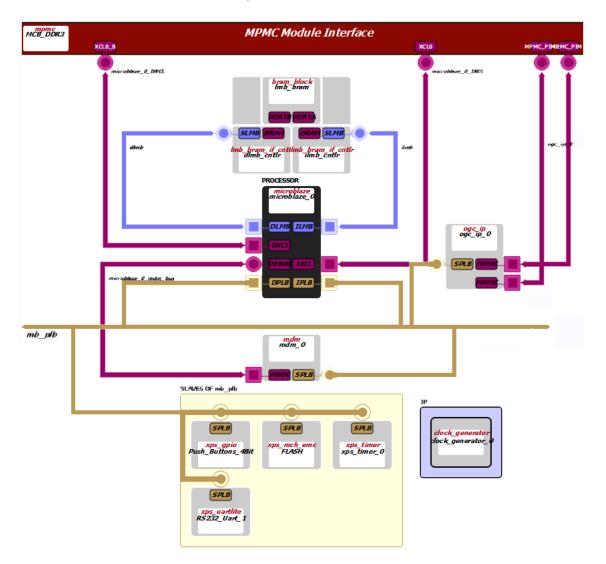

After developing an overall design of the system, we implemented a hardware platform that would drive the graphics acceleration core. For the hardware platform, we used the Xilinx Embedded Development Kit (EDK) to generate a single-core Microblaze system. Furthermore, this system utilized Xilinx's Multi-Port Memory Controller (MPMC) to arbitrate memory transactions and minimize time that we would have needed to spend on implementing a custom memory interface. This chapter describes the embedded platform.

### 4.1 Hardware Implementation

With the hardware implementation of the embedded platform, we made a few key design decisions to allow for all necessary functionality of the graphics core and to ensure speed and efficiency. Primarily, the system needed to utilize a bus for peripherals that supported FIFO-like write access and external interrupts. Based on these needs, we chose the CoreConnect Architecture Processor Local Bus (PLB) v4.6 as the interface to our graphics hardware core.

The Processor Local Bus not only allowed for a configurable FIFO interface and an external interrupt signal, but it also provided register space that could be mapped to main memory. As such, this allowed for a simplified graphics command set, as certain graphics commands could be designated a register rather than being queued into the FIFO. This additionally provided for near-immediate hardware response, as there is a several-cycle delay before command data is popped off the FIFO, decoded, and executed.

Furthermore, we also generated a few key peripherals that ensured complete functionality of the system. In addition to the MPMC, we added a RS232 UART core for debug communication, as well as the Xilinx Clock Generator core to generate the bus and pixel clocks. For the development platform, we chose a clock frequency of 75MHz to drive the peripheral bus and Microblaze CPU. However, this frequency could very easily be increased or decreased, depending on the performance and power consumption requirements of the system. We chose a constant pixel clock of 25MHz, as the graphics hardware core was designed only to use a single resolution.

With the essential hardware components included in the embedded platform, we added

a few other Xilinx cores for extra miscellaneous features. These included the Xilinx Platform Studio General Purpose Input/Output (GPIO) for the development board's (SP605) LEDs, push buttons, and DIP switches. This was so that they could potentially be used as debug tools within the software stack, or for more complex user-controlled demos. Lastly, we added the Compact Flash core as a potential storage medium for application data that would use the graphics core.

The figure below shows the EDK generated block diagram of the embedded platform. This entire system was synthesized and loaded on to the Spartan 6 FPGA. With the exception of the OGC\_IP\_0 (Open Graphics Core) peripheral instance, we generated all components of the system with the Xilinx toolset. OGC implemented the custom VHDL that describes the implementation of the RTL hardware graphics core (See Chapter 5 - RTL Graphics Core Implementation).

Figure 11: Embedded platform block diagram

### 4.2 Software Implementation

As part of the software implementation of the embedded platform, we used a scriptbased scheme to automatically generate the hardware's Board Support Package (BSP). This script, invoked by the Eclipse IDE, would automatically fetch all of the latest driver sources (based on the hardware platform specification) for all peripherals used (including both the Xilinx cores and our custom graphics core), and then rebuild it for use with the current application being loaded on the platform. Such a scheme allowed us to easily make driver modifications to the graphics core without having to manually reconstruct the BSP each time. Furthermore, this allowed for a more modular graphics source base, which opened the possibility for the core to be shared among multiple embedded hardware platforms.

Each individual application written to run on both the hardware and graphics platform was created as a C stand-alone application. The stand-alone option was chosen for simplicity, as none of the implemented demos required any OS-centric features (e.g. no threading or extensive memory management requirements). Alternatively, for more complex applications, the Linux operating system or Xilkernel (a lightweight Microblaze kernel and software stack) could possibly have been used with the platform. Each standalone demo statically linked the BSP libraries and could be independently loaded and executed on the hardware platform. The BSP included our custom graphics hardware driver.

### 4.3 Summary

This chapter discussed the hardware design and implementation of the embedded platform. It focused on the design decisions we made to construct the environment to implement the hardware graphics core. The next chapter (Chapter 5: RTL Graphics Core Implementation) discusses the hardware architecture and implementation of the graphics core peripheral.

# 5 RTL Graphics Core Implementation

We implemented the RTL graphics core, the center of the FPGA-based graphics acceleration platform, as a custom intellectual property (IP) core within the Spartan 6 FPGA. The core adhered to the Xilinx specification for PLB v4.6 cores, making it entirely portable to other Xilinx platforms. We implemented this core primarily in VHDL. Additionally, we used Verilog for several digital video control modules. This chapter discusses the hardware implementation of the RTL graphics core.

## 5.1 Architecture and Features

The implementation of the graphics core met and exceeded the initial design criteria. The following features were implemented in hardware:

- 1. Graphics Processing Unit

- (a) Command Processor running at 75MHz

- (b) 32-bit FIFO command and data interface

- 2. Video Interface

- (a) Digital Video Out (DVI) and VGA support (25MHz, 640x480 resolution)

- (b) Framebuffer (16-bit color depth, format RGB565)

- (c) Double buffering with a video-synchronization interrupt

- 3. Rasterizer

- (a) Point, line, and triangle primitive rasterization

- (b) Color interpolation (16-bit)

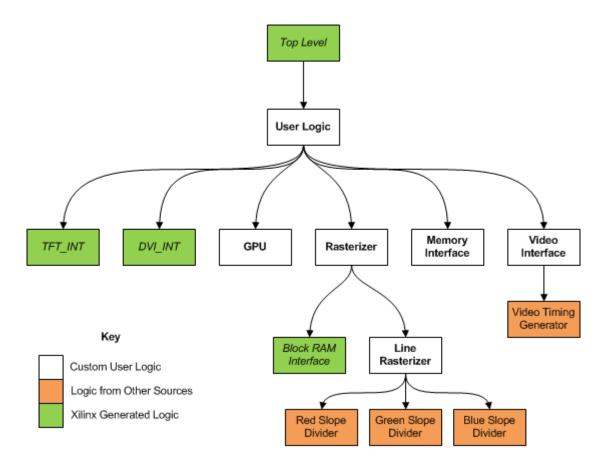

We implemented these features within a hierarchical architecture. As a Xilinx PLB peripheral, a top level VHDL module was generated that interfaced with the Microblaze system and processor bus. This interface was constant and as such not at all modified during the development of the peripheral. It did, however, instantiate a user logic module

that served as the top level for all of the custom user logic that described the functionality of the graphics hardware core. The four main modules that it instantiated were: (1) the Graphics Processing Unit (GPU), (2) the Memory Interface (MI), (3) the Video Interface (VI) and (4) the Rasterizer (RAS). The hierarchical structure of this implementation can be seen in Figure 12.

Figure 12: Hierarchical look at the RTL hardware core architecture

Additionally, the system instantiated several other logic blocks that were not custom user logic. These were: (1) a Block RAM interface, (2) a TFT interface and (3) a DVI interface. These modules were all Xilinx generated interfaces. Additionally, there were two other modules that were utilized within the project: the serial division module by John Clayton (licensed under the GNU Lesser General Public License) and the 640x480 video timing module by Ulrich Zoltán (licensed by Diligent, Inc). These modules were used to implement the red, green, and blue slope dividers (of the rasterizer) and the video timing generator (of the video interface), respectively.

## 5.2 Implementation

We divided the implementation phase of the RTL graphics core into the five main custom user modules. This section discusses their specific implementations.

### 5.2.1 Graphics Processing Unit

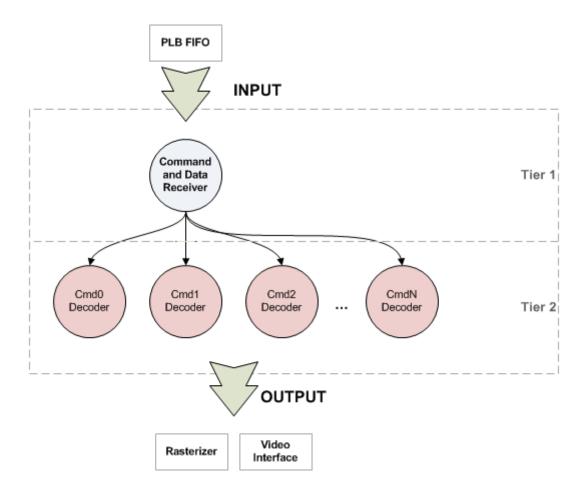

The Graphics Processing Unit (GPU) interfaces all input data streams to the graphics hardware, decodes these data, and subsequently sends these data to the other modules within the core. Consequently, we implemented the GPU in two tiers. With the first tier, the GPU received the command and data stream from the PLB FIFO. With the second tier, it decoded and dispatched the commands and data received to the various other subsystems. This two-tier architecture is illustrated by the diagram in Figure 13.

Figure 13: GPU tiered architecture

In Figure 13 above, each circle represents a VHDL process running concurrently. As

such, there is one process that implemented the command and data receiver, and another process for each command decoder.

We implemented the first tier of the GPU, the command and data receiver, using a simple VHDL process that synchronously checked whether a new data word had been enqueued in the FIFO (the WFIF02IP\_RdAck signal of the FIFO interface will go high). If this signal went high, the GPU would then assume that the first word is the command data, and that every subsequent word received would be parameter data for that command. Each GPU command (see Chapter 3: Project Overview and Design) has a fixed size, so subsequently the GPU would count received words until it has received all necessary data. At this point, it would then assume that the next word received is a command, and the process would continue.