# Reconfigurable Software Defined Radio Platform

# A Major Qualifying Project Report: Submitted to the Faculty of the WORCESTER POLYTECHNIC INSTITUTE

in partial fulfillment of the requirements for the Degree of Bachelor of Science by

| Francesco            | Bivona                                    |

|----------------------|-------------------------------------------|

| Alexander            | r Camilo                                  |

| Date: Marcl<br>Appro |                                           |

|                      |                                           |

|                      | Professor Xinming Huang, Major Advisor    |

|                      |                                           |

|                      | Professor Alexander Wyglinski, Co-Advisor |

# Abstract

The goal of this Major Qualifying Project is to provide the framework for integration of a Virtex series field programmable gate array (FPGA) into GNU Radio, allowing GNU Radio to have control over both FPGA and non-FPGA components of the pipeline. In this report, we address the following: our research into the which FPGA series would be most beneficial to our project, an outline of the evolution of our design over the course of the past 21 weeks, and a summary of the final outcomes in various subsets of project development.

# **Executive Summary**

The concept of modular reconfigurable radio has spanned decades, beginning humbly with hardware-based reconfigurable radio such as the Joint Tactical Radio System and the Speakeasy Project, and progressing to software-defined radio application programming interfaces (APIs) such as GNU Radio [1][2]. Our project seeks to take this a step further, and integrate reconfigurable hardware (a field programmable gate array) into a software-defined radio pipeline.

To this end, we conducted significant research and development with regard to FPGA architecture for SDR applications. This consisted of attempts at implementing a bidirectional peripheral component interconnect express (PCIe) interface and basic dynamic reconfiguration using the internal configuration and access port (ICAP) interface. Eventually, the decision was made to streamline the architecture using the XILINX Embedded Design Kit (EDK)

[22]. At this stage, we have a functional bidirectional PCIe interface (with the driver still being a work-in-progress), and dynamic reconfiguration via ICAP functioning in a test bench environment.

Additionally, we have conducted experimentation into the application of GNU Radio to specific tasks. This began with simple frequency modulation (FM) radio transmission, and then moved on to more complex digital waveforms and information transfer between two computers. This experimentation also accommodated for the presence of an FPGA (in tandem with simultaneous FPGA architecture development), either in the form of passing a data through unhindered or

being used as a signal generator. Additionally, an investigation into the inner workings of GNU Radio signal processing blocks was carried out.

Finally, our focus was directed toward FPGA integration with GNU Radio. This involves finalizing filter architecture for the FPGA using DSP48e slices, final debugging of the FPGA's hardware device driver, and writing up a GNU Radio pipeline to wrap FPGA and PC signal processing components together to complete a task.

The end product of this project consisted of a functional GNU Radio pipeline, implementing the FPGA to carry out filtering. We were able to synthesize a lowpass filter on the FPGA, followed by a raised cosine filter when the hardware driver was debugged with the lowpass filter example. File I/O still remains slightly buggy, and the destination file for the output did not store information. However, GNU Radio was capable of controlling and making use of the FPGA in all other respects, and functionality was confirmed by displaying filter output in the terminal. While integrating an FPGA (independent of the front-end's FPGA) has been accomplished before, this is the first seen of it within a widely-used environment such as GNU Radio. The current platform sets the framework for future research into implementing dynamic reconfiguration of the radio pipeline.

# Table of Contents

| ABSTRACT                                                               |    |

|------------------------------------------------------------------------|----|

| EXECUTIVE SUMMARY                                                      | 2  |

| 1. INTRODUCTION                                                        | 6  |

| 2. LITERATURE SURVEY                                                   | 7  |

| 2.1 ORIGINS OF RECONFIGURABLE RADIO                                    | 7  |

| 2.2 THE INTRODUCTION OF SOFTWARE DEFINED RADIO                         |    |

| 2.3 SPECTRUMWARE AND GNU RADIO [6] [7]                                 |    |

| 2.4 FPGAs and Dynamic Reconfiguration.                                 |    |

| 2.5 FPGAs and Software Defined Radio                                   |    |

| 2.6 PLATFORM APPLICATIONS                                              | 13 |

| CHAPTER SUMMARY                                                        | 14 |

| 3. INITIAL DESIGN CONCEPT                                              | 15 |

| 3.1 CHOICE OF FPGA                                                     | 15 |

| 3.2 Possible Choice of Board                                           |    |

| 3.3 Bus Interfaces                                                     |    |

| 3.3.1 Option 1: USB                                                    |    |

| 3.3.2 Option 2: PCIe                                                   |    |

| 3.4 DYNAMIC RECONFIGURATION                                            |    |

| 3.4.1 Hardware                                                         |    |

| 3.5 PROPOSED METHODS OF DYNAMIC RECONFIGURATION                        |    |

| 3.5.1 Single Module Dymanic Reconfiguration                            |    |

| 3.5.2 Multiple Difference Bitmaps                                      |    |

| 3.5.3 Independent Application                                          |    |

| CHAPTER SUMMARY                                                        |    |

| 4. PROJECT DEVELOPMENT: GNU RADIO                                      | 25 |

| 4.1 INTEGRATING THE FPGA AND A HOST APPLICATION (GNU RADIO)            | 25 |

| 4.2 AN EXERCISE – FM TRANSMISSION WITH GNU RADIO                       | 29 |

| 4.3 Preparing FM Transmission applications for FPGA Integration        | 32 |

| 4.4 THE GNU RADIO SIGNAL PROCESSING BLOCK                              |    |

| 4.5 DIGITAL COMMUNICATIONS – IMPLEMENTING DBPSK                        |    |

| 4.5.1 A Demo – DBPSK Modulation over TCP/IP                            |    |

| 4.5.2 Initial Attempts at a Lower-Level Approach                       |    |

| 4.6 THE CURRENT CONCEPT – A PACKET-BASED APPROACH                      |    |

| 4.6.1 Unidirectional Communication                                     |    |

| 4.6.2 Bidirectional Communication                                      |    |

| 5. FPGA ARCHITECTURE AND GNU RADIO INTEGRATION                         |    |

|                                                                        |    |

| 5.1 DRIVER DEVELOPMENT                                                 |    |

| 5.1.1 PCI Initialization                                               |    |

| 5.1.2 Character Device Initialization                                  |    |

| 5.1.4 Driver Debugging                                                 |    |

| 5.1.4 Diver Deologying  5.2 PCIE Interface Development Initial Attempt |    |

| 5.2.1 Hardware and Environment Testing Using Reference Bitmap          |    |

| 5.2.2 Compiling the Provided Example Code in ISE                       |    |

| 5.2.3 Generating a Bitmap with Only the PCIe MAC/PHY                   |    |

| 5.2.4 Addressing Throughput Issues in the Project                      |    |

| 5.2.5 The ICAP Interface                                | 60 |

|---------------------------------------------------------|----|

| 5.3 PCI RE-IMPLEMENTATION USING EDK                     | 60 |

| 5.3.1 The PCIe to PLB Bridge and Its Role in the System | 60 |

| 5.3.2 The FSL Link and Interfacing to the Pipline       | 61 |

| 5.3.3 Test Environments                                 | 63 |

| 5.4 Platform Efficiency                                 | 66 |

| 5.4.1 Driver Efficiency                                 | 66 |

| 5.4.2 PCIe Transfer Efficiency                          | 66 |

| 5.5 DEMO FILTER IMPLEMENTATION                          |    |

| 5.5.1 FIR Filters                                       |    |

| 5.5.2 FIR Filter Implementation                         |    |

| CHAPTER SUMMARY                                         | 69 |

| 6. FPGA/GNU RADIO INTEGRATION                           | 70 |

| 6.1 LOOPBACK                                            | 70 |

| 6.2 LOWPASS AND RAISED COSINE FILTERS                   |    |

| 6.2.1 System Design                                     |    |

| 6.2.2 COMPARISON TO GNU RADIO ONLY                      |    |

| 6.2.3 FPGA FILTER TESTING                               | 82 |

| CHAPTER SUMMARY                                         | 91 |

| 7. FUTURE WORK                                          | 92 |

| 8. CONCLUSION                                           | 94 |

| 9. REFERENCES                                           | 96 |

| 10. APPENDICES                                          |    |

| -v                                                      |    |

## 1. Introduction

Software-defined radio (SDR) is a very active field in the world of digital signal processing. It is used in a variety of scenarios, where either mobile or easily adaptable systems are required. Thus, we have chosen this field, since it is a useful subject to be knowledgeable about and to contribute data toward. For the purposes of this project, we intended to integrate a field programmable gate array into an otherwise strictly software-composed pipeline. This would delegate hardware resources away from the host computer, without losing the reconfigurable nature of software. To prepare for this, we implemented FPGA loopback in a variety of GNU Radio applications, and ultimately implemented filtering of signals on the FPGA. In future work, it would be possible to adapt the FPGA component of the pipeline such that it can be dynamically reconfigured, which is less complicated to implement on reconfigurable hardware than in software. The primary motivation for this project was to accelerate the development of software defined radio, integrating hardware that is just as easily reconfigurable as the software components in the pipeline. Currently, FPGAs have been integrated into software defined radio platforms, but it has been limited in terms of which radio frequency (RF) front-end is used, and which API controls the hardware. While tested only with DD [21] a program intended for copying and pasting data, which we used for debugging) and GNU Radio, our design can be controlled by any existing SDR API that supports UNIX file I/O, and can interact with any RF front-end the current API supports, since it runs independent of the front end and the API draws the connections between the two. We have established a framework with which future researchers could implement further functions, such as dynamic reconfiguration.

# 2. Literature Survey

There has been prior research and development put behind the concept of reconfigurable radio. This extends back as far as the mid-'90s with military investment in modular radio components [1] [2]. It was revolutionized with the concept of software-defined radio, which minimized proprietary hardware and implemented most signal processing within a computer. This was brought into the mainstream with the Spectrumware project, later to become GNU Radio [5] [6]. Since then, some have investigated the possibility of a combination of the two methods, implementing an FPGA in collaboration with a PC for digital signal processing. It maintains the reconfigurable nature of software while still having more resources at its disposal than a non-dedicated personal computer. There are even dynamic reconfiguration possibilities which surpass those of software-only pipelines.

#### 2.1 Origins of Reconfigurable Radio

Prior to the advent of today's FPGAs and software-defined radio, the concept of radio that one can configure to be compatible with multiple mediums was still considered. However, it was more intricate. With the lack of ability to alter the data pipeline with some lines of code, data processing modules for different tasks were just that – physical "modules" that had to be stored, installed, and swapped out as the application saw fit. Such was the concept behind the Joint Tactical Radio System (JTRS) and the Speakeasy project [1][2]. They are multiprocessor systems (JTRS using Pentium cores, and Speakeasy using four TMS320C40 processors) that require extensive custom hardware to perform many of the signal processing tasks presented by the varying military communication conventions available [1] [2].

#### 2.2 The Introduction of Software Defined Radio

Software defined radio is the replacement of analog components in a radio pipeline, at the very least starting at the IF stage and continuing from that point onward [3]. However, ideally all hardware should be replaced with software from the antenna onward [3]. RF still cannot yet practically be processed with general-purpose processors. Furthermore, software radio is overall slower than implementing it in hardware for certain applications (such as modulation), so implementing configurable hardware such as an FPGA at certain points would improve performance without limiting the configurability and multimode operation that are the most significant benefit of software-defined radio [3]. Application-specific integrated circuit (ASIC) designs would be able to accomplish similar tasks, but reconfigurability is at a minimum since ASICs are not readily reconfigurable after manufacture. There is one area where ASIC outshines an FPGA – power consumption. As a general rule, state-of-the-art ASIC designs are more power-efficient than equivalents implemented on an FPGA. An illustration of this is the measurement of power consumption during the implementation of numerous counters, in one case on an Altera FPGA, and in another with an ASIC. See Table 1 for the results.

| Number of active counter blocks | 1    | 16    |

|---------------------------------|------|-------|

| ASIC power (mW)                 | 0.9  | 9.9   |

| FPGA power (mW)                 | 53.6 | 112.4 |

Table 1: Power consumption on different numbers of both ASIC and FPGA counter blocks. The FPGA exceeds the ASIC in power consumption by orders of magnitude [4].

This primarily limits FPGA use to stationary tasks rather than mobile ones. ASIC is still superior in mobile applications. However, the benefits of applying an FPGA when increased power consumption is tolerable are not to be ignored: Ease of design and manufacture, fewer discrete components – these are attained with the implementation of FPGAs [5]. With significant

streamlining and development, cost can be reduced and standardized APIs for SDR components can be developed.

## 2.3 Spectrumware and GNU Radio [6] [7]

The Spectrumware project is the predecessor of modern software defined radio. Spectrumware later proceeded to branch off into two directions: Vanu Radio – the commercialized version of the Spectrumware architecture – and GNU Radio – the open-source standard for any research application involving the Universal Software Radio Peripheral (USRP). Spectrumware and its descendants are actually far more economical than hardware module-based designs. Using GNU Radio as an example, the software is open-source and can be used with most modern personal computers (if they are running Linux). The only additional hardware required is a front-end, usually satisfied by the USRP. This hardware costs \$700 [8]. This is an insignificant amount when compared to hardware that required a budget from the United States military to produce. With the advent of more powerful microprocessors, more and more of the system could be simulated by software. Thus, the pipeline is reduced to minimum transmitter/receiver hardware (a small FPGA is used for initial signal processing in the USRP in the case of GNU Radio, and similar proprietary hardware with Vanu radio) and an extensive API for simulating signal processing modules that once required dedicated hardware. The system still has its drawbacks. It is very CPU-intensive, while an FPGA-assisted platform would take much of the burden off of the microprocessor. Additionally, under normal circumstances, a GNU Radio pipeline must be stopped for some time, however short, in order to be modified. An FPGA implementing dynamic reconfiguration would provide the ability to modify the pipeline mid-operation. This will prove useful in tandem with existing GNU Radio applications.

#### 2.4 FPGAs and Dynamic Reconfiguration

FPGAs have been implemented in a software-radio environment to some extent for a significant amount of time – the FPGA integrated into the USRP is a good example of this. The USRP includes an Altera Cyclone, which is significantly smaller and less powerful than the Virtex-5 we intend to implement [9]. Furthermore, it is incapable of dynamic reconfiguration. However, this is acceptable since it is only meant to handle high sample-rate processing involved in transmission and reception [9]. Additional hardware is included in the form of daughterboards, which contain dedicated transmitter/receiver/transceiver hardware [9]. They are small and easily transferable depending on the desired application, ranging from DC-30Hz transmitters/ receivers to 2.4 GHz/5 GHz dual band transceivers [9].

There are even instances where dynamic reconfiguration of the pipeline with an FPGA is proposed. FPGAs have generally been applied to the SDR pipeline in different ways, or applied to a different task entirely. For instance, the 7142 Virtex-4 software radio PMC/XMC Mezzanine takes the place of both the radio frequency (RF) front-end and the modulation segment of the pipeline [10]. This makes it more limited, since its RF front-end cannot be as easily replaced if a certain task calls for it. Our design uses the USRP as an RF front-end, but this can be later swapped with minor modification, without rendering a portion of the FPGA peripheral outdated.

#### 2.5 FPGAs and Software Defined Radio

In 2005, a plan was proposed (but not implemented) to use an FPGA in a similar manner to our platform, using partial reconfiguration to modify the pipeline as needed. Research into the subject was extensive, assigning different levels of reconfiguration desirable within an active

pipeline: standard (GSM, 802.11g, etc.), mode (DSSS, FHSS, etc.), and service (bandwidth, etc.) switching. The pipeline's actions were also broken down into categories based on hardware requirements - Modulation (FPGA, Digital Signal Processor), Data Handling (microprocessor, RAM), and Coding (DSP) [11]. These tasks should be divided into three hierarchical layers – the overall communication class, functions within this class (which could be modified for specific applications of a certain communication class), and the most internal layer, including the contents of a particular function [12]. Depending on the changes that need to be made from one pipeline to another, modifying a certain hierarchical layer would make the reconfiguration more efficient than modifying the pipeline on the most intricate level [12]. Modular design simplifies the implementation and modification of a pipeline. A collection of pre-designed modules capable of being swapped out is easier than having to rewrite a segment of one large piece of code, both in terms of the user's understanding and the complexity of reconfiguration. Reconfiguring on this scale is a known as reconfiguring on the functional level, and is in general what we have chosen to implement [13].

There are a few concerns that must be taken into account when implementing a design on a dynamically reconfigurable FPGA. First, one must take into account the reconfiguration time. Reconfiguring the FPGA directly, it would be split into slices of the same pipeline, and any modification to slices would interrupt the flow of data until the new slices were written [14]. This can be alleviated by making a copy of the entire pipeline and modifying that [14]. Copying the pipeline allows the reconfiguration to take whatever time is necessary to overwrite specified portions, and the data stream is only interrupted while switching from the original pipeline to the modified pipeline [14]. This form of reconfiguration is something referred to as "merge

configuration" [15]. This also allows for slices that do not span the entire length of the FPGA, given a properly configured communication link between them [15]. However, it requires more resources than direct reconfiguration, since at any reconfiguration time there must be two instances of the pipeline on the FPGA [15].

The communication link, or the means by which the blocks will communicate with each other, is another issue which must be addressed. On the surface, the solution appears simple: we must implement a bus macro – a set of inputs and outputs that are held constant between all slices regardless of configuration, and an arbiter directing IO to/from each slice. However, we must be cautious, because the implementation of a bus macro is platform dependent. Work must be done somewhat from scratch, which is a significant effort. One idea for an adaptive bus macro design is as follows: HIBI (Heterogeneous IP Block interconnection) links together blocks with a variety of different interfaces (open core protocol (OCP), first-in-first-out (FIFO), direct memory access (DMA)) [16]. This is a very adaptive design, even though it is not developed for the Virtex-5 [17]. It would be useful in that there are likely many modulation task blocks already created, and this allows for a variety of IO interfaces to be interconnected [16]. A platformspecific bus macro would not be nearly as versatile, and rely on blocks created specifically to function with that macro [16]. This is worth looking into, should we find our initial bus macro inadequate [16]. What makes our design significantly different is that the "arbiter" will likely be the host PC's microprocessor itself (along with any other data management, etc.), rather than an FPGA block. In all of Delahaye's work, there is no mention of using device-nodes as a means of hardware interface with preexisting SDR APIs such as GNU Radio. This work comes closest to

matching our own (at times), and evidence to the contrary has not yet been unveiled, device-node IO implemented in this manner is new to the concept of linear SDR pipelines.

The final significant decision that needs to be made is whether to use internal or external configuration [17]. "External" configuration involves a CPLD or microprocessor directly overwriting the FPGA's contents, with no internal intervention [17]. However, the Virtex-5's ICAP interface allows for what is called "internal" configuration, or auto-configuration [17]. Issuing commands and data to the ICAP allows for the FPGA to largely rewrite itself, with less equipment involved (only the host PC to issue commands/information) [17]. For our application, it is far more effective to implement internal reconfiguration, since the resources are already there. The ICAP does limit us to partial reconfiguration, but that is acceptable. We're not changing the structure of the entire FPGA (size/number of slices) with reconfiguration, only the contents of the slices. FPGA structure remains constant unless a different chip is used. Furthermore, partial reconfiguration requires less overhead than a complete re-flash of the FPGA [17].

## 2.6 Platform Applications

There are numerous applications for SDR in a mobile environment – cellular phones, mobile wireless, and so on. The distinction should be made here that our design is *not* meant for such tasks. The design method taken is simply not well-suited. It is critical to keep power consumption to a bare minimum in a mobile environment, and FPGAs are renowned for their power consumption, the Virtex-5 being no exception. This is in addition to the USRP requiring its own power supply, and, of course, the host PC's power. A. Dejonghe defines the acceptable rate of power consumption for a digital baseband platform to be 100 million operations per

second (MOPS)/mW [18]. This is nowhere near the current level of power efficiency for modern FPGA technology at all, let alone an FPGA implementation. Referring back to Table 1, even implementing 16 counters, each of which only use a few components, exceeds desired power consumption. Given the components, effective mobile use of SDR as a reconfigurable platform would be infeasible at this time. It is worth mentioning, however, that "mobile" in this case does not include being inside vehicles, or connected to some other power source which gives our platform access to surplus power while still technically being capable of changing location. In such an environment is where our platform would thrive, particularly in military applications. Of course, it would also work in a stationary, desktop environment, for research or other purposes.

#### **Chapter Summary**

Some of the branches of software defined radio mentioned here, namely FPGA integration and dynamic reconfiguration, are within the realm of this project or in the near future work of the project. However, some such as cognitive radio are a bit far off in terms of development with respect to our project. Still, having knowledge of the possibilities does lend itself to accelerating progress on the path toward said possibilities, and was thus worth investigating. This project does not comprise the entirety of software-defined radio development. Due to limited time and resources, this project is mainly focused on integrating an FPGA into an SDR environment.

## 3. Initial Design Concept

Our design is an attempt at integrating an FPGA peripheral of our choosing into a software-defined radio pipeline. Time permitting, we also intended to implement some means of dynamic reconfiguration, and have plotted out strategies for such an endeavor. These remain unimplemented, and are a recommended continuation for anyone who sees fit to pursue similar goals. At the very beginning of our project, some key decisions had to be made. Most significant among these were the choice of the FPGA we were to use, and the choice of interface between PC and FPGA peripheral.

#### 3.1 Choice of FPGA

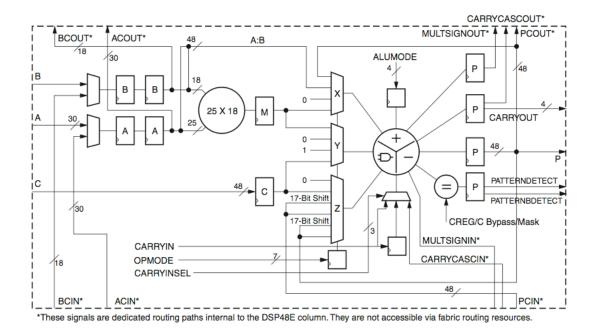

The Virtex 5 series of FPGAs can be broken into 4 different classes of device each targeting a specific type of design challenge. The 4 families are the LX, LXT, SXT, FXT. The T means that the FPGA has hardware for high speed transceivers which are required to implement protocols such as SATA and PCIe. The family is additionally broken up into the LX, SX, and FX, groups. The LX and LXT FPGAs contain a large amount of generic CLBs and little dedicated hardware. The FXT family contains embedded hard-cores for SOC type designs. The DSP variant of the family is the SXT with 6 colums of 49 DSP48e slices. We believe that these DSP blocks which consist of a 25x18 bit multiplier and 48 bit accumulate register would be extremely beneficial for our application, because they wouls allow us to make high-speed implementations of common signal processing blocks.

#### 3.2 Possible Choice of board

Figure 1: ML506 FPGA development board featuring a VIRTEX 5 SXT FPGA and a 1x PCIe connector.

The ML506 development board from Xilinx would be well suited to our project for several reasons. The FPGA on this board is a XC5VSX50TFFG1136 which is a Virtex 5 SXT series FPGA. This FPGA provides us with 288 DSP blocks which would simplify the design of pipeline modules by replacing commonly synthesized hardware with real hardware blocks. In addition to the DSP slices the FPGA supports multi gigabit transceivers giving it the capability to use PCIe. The development board includes interfaces for all of the feasible methods of interfacing the device with the host computer. These interfaces include PCIe, USB, and gigE. As well as having the proper interfaces and resources, this board's price point is low when compared to other development boards we have found.

#### 3.3 Bus Interfaces

Ultimately, the exact interface does not matter if we structure the code correctly and view the interface as a pipe on a higher level.

#### 3.3.1 Option 1: USB

Universal Serial Bus (USB) is one option we could have pursued for interfacing our FPGA with a PC and RF frontend. While more ideal for external hardware than a peripheral card that is meant to be integrated into the PC, it is sufficient. USB bandwidth peaks at 60 Mbps, of which only 10% depending on transmission method would be used. The ideal way to go about the interface with USB is to make use of bulk transfers. The performance is heavily dependent on other traffic present on the bus.

If there is no other traffic, the bulk transfers can make use of up to 90% of the bandwidth. With traffic, however, bulk transfers receive the lowest priority and thus suffer from severe latency problems. There are alternative methods of data transfer with USB (i.e. isochronous transfer) which have higher priority, but always have a lower maximum bandwidth percentage. What a USB interface would require is an entire bus dedicated to the SDR platform, using bulk transfers to handle data. Additionally, the USRP only supports a gigE interface, not USB. So using a USB interface for our peripheral card for the sake of uniformity becomes a moot point if the user decides to use the USRP2 rather than the USRP.

## 3.3.2 Option 2: PCIe

The PCIe interface option provides several advantages. Latency becomes less pronounced, with PCIe generally closer to the system memory and CPU on the PC. With a PCIe interface, we can also take advantage of the conventions of PCIe, which allow for DMA and bus mastering to communicate between peripherals independent of the PC. Another significant benefit is the greater bandwidth which, for PCIe, is 2.5 Gbps or higher minus overhead. On the other hand, USB provides 60 Mbps minus overhead. While the USB bandwidth is acceptable, PCIe proves to be more promising. Additionally, PCIe leaves us with a platform that is more expandable. The device can be compatible with a wider array of RF front-ends than the USRP due to increased theoretical bandwith. Front-ends are already easily interchangeable, since the ultimate purpose of our peripheral card is to be reconfigurable, and information accepted and given by front-ends is already similar from front-end to front-end. With the USRP's USB interface, the latency and bandwidth advantages of PCIe are only seen between peripheral card and PC. However, if an RF front-end that also uses PCIe (or a faster interface such as gigE) was introduced in place of it, the bus mastering and DMA allow for more efficient transfer of data, so front-end and peripheral would be able to communicate with each other with out the overhead of the CPU.

Admittedly, PCIe adds a certain complexity to the interface compared to USB. While USB uses periodic frames with packets for control, the PCIe interface operates with streams of packets with a layered protocol stack. However, the length of time developing the software side of the interface is greatly reduced by the presence of pre-existing code and IP modules. XILINX software tools contain the code required, and even have a wizard for setting up the Virtex-5

FPGA as PCIe block RAM, in addition to having a PCIe-processor local bus (PLB) bridge, which simplifies DMA access. This overcomes any difficulties the added complexity present.

## 3.4 Dynamic Reconfiguration

#### 3.4.1 Hardware

XILINX's Virtex series and the Spartan-6 support partial reconfiguration, where a portion of the FPGA can be reprogrammed while the other portion of the FPGA is still operational. The Virtex-2, 4, and 5 series FPGAs support dynamic reconfiguration through several interfaces, Joint test action group (JTAG), Serial Perepheral Interface (SPI), and SelectMap (accessable through the internal configuration and access port) interfaces. SPI and SelectMap are external interfaces that can be used, which means that a bitmap can be applied from iMPACT (Xilinx's programming utility) or by an external controller.

The ICAP configuration interface allows for self-reconfiguration. Synthesized hardware may interface to the ICAP interface, which appears as a bidirectional synchronous parallel bus of varying with depending on the family, and issue the sequence of commands present in a bit stream to change routing, configurable logic block (CLB) configuration, and block RAM (BRAM) contents. The more recent series of FPGAs such as the Virtex-4 and Virtex-5 series support wider bus widths allowing for faster reconfiguration.

#### 3.4.2 Software

The way dynamic reconfiguration is accomplished is through partial bitmaps. Instead of containing configuration information for a whole design these partial bitmaps contain configuration information for only a few CLBs allowing for a large portion of the FPGA to remain unmodified while reconfiguration takes place.

Communication between the hardware included in these partial bitmaps is accomplished through a bus macro. The bus macro defines an interface between the existing static logic and the newly configured logic, much such as a connector or socket. XILINX provides tools to facilitate dynamic reconfiguration by allowing low level changes to be made to bitmaps. This tool is called Plan-Ahead.

### 3.5 Proposed Methods of Dynamic Reconfiguration

After doing some research as to how dynamic reconfiguration functions on XILINX based FPGAs, we have come up with several possible designs that would achieve dynamic reconfiguration. These designs vary in complexity and cost and are organized starting with the easiest to implement and ending with the hardest yet most interesting design. While dynamic reconfiguration was not implemented, we still devoted time to the background study, which may prove useful to future researchers. Thus, these sections remain for future reference.

#### 3.5.1 Single Module Dymanic Reconfiguration

In this design we use a single module with a parallel bus macro for incoming and outgoing samples connected to some mechanisim designed facilitate the transfer of data to and from the host over our chosen interface. In addition to this mechanisim the bitmap would contain enough hardware to grab a configuration file from the host system via an interface such as USB, gigabit Ethernet (gigE), or PCIe and change the configuration of this one "module" shown in figure 2 via its internal ICAP interface.

Using this method of configuring the FPGA we could have a bitmap for various different pipelines and we would have the capability to change our current pipeline. The downside of this approach is the pipelines themselves would be fairly static. We would not be able to alter the structure of individual blocks dynamically.

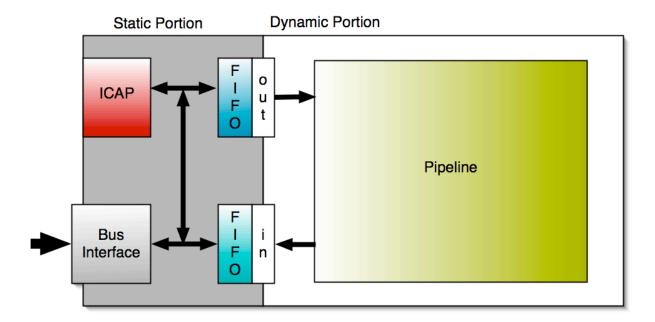

Figure 2: Dymanic reconfiguration where a module is an entire pipline.

Since this design does not vary very far from XILINX's documentation and the beaten path and it should be fairly easy to implement. The complex part would be generating a few sample bitmaps and writing a loader that would apply these bitmaps. The benefit of this is that the computer can change the pipeline directly from within their signal processing environment.

## 3.5.2 Multiple Difference Bitmaps

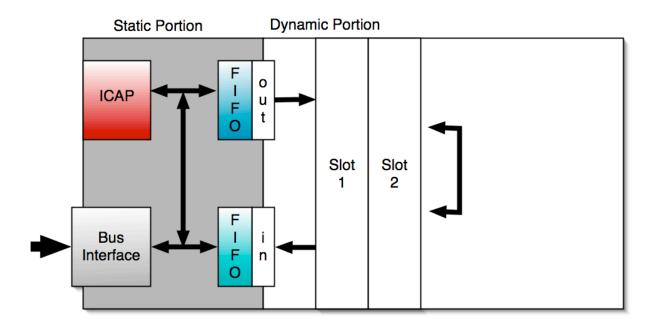

Another approach that would give us more control over the actual structure of the SDR pipeline while still remaining low in complexity would be to set aside a certain amount of slices for blocks and generate difference bitmaps for a given module in these different slots as seen in figure 3.

Figure 3: A diagram outlining the process of dynamic reconfiguration using bitmaps.

Communication between modules would be handled by bus macros on the boundaries between slices. The benefits of this approach are increased control over the structure of the SDR pipeline. We could switch between BPSK and QPSK depending on the quality of the channel for example. The downside of this approach would be that if our pipeline had 10 "slots" we would need 10

bitstreams for each module where each bitstream would be that module in that portion of the FPGA. A QPSK module would have a "in slot 1" bitmap and an "in slot 2" bitmap. This is due to limitations in XILINX's synthesis and PAR (place and route) tools and in the hardware of the virtex 5 itself. An Analogy in terms of software would be machine code with absolute jumps (as opposed to relative jumps). Such code could only be located at an initiall address in system specified at compile time and different compiled versions would be needed if different starting vectors where desired.

## 3.5.3 Independent Application

The final approach would be to gain a better understanding of the structure of the configuration bitmap such that we could have an application keep and modify this bitmap representation of the FPGA's structure and generate a dynamic bitmap that would be used to reconfigure the device on a very fine level. For example, a program could take a generic template of a module and make a modification on the routing and configuration of the internal structure of the FPGA to incorporate it into the SDR pipeline. This approach could potentially be dangerous and lead to damaged hardware because it would involve reverse-engeneering XILINX's proprietary bitmap format.

## Chapter Summary

In this section, we have outlined the various possible ways that we could have approached the hardware design and software interface problems. A desired bus interface to develop around, method to implement dynamic reconfiguration, and a way of integrating our FPGA peripheral into GNU Radio are all required at first. Through the evaluation of hardware, we have settled on

PCIe for the bus interface, single module dynamic reconfiguration, and the device node interface to tie the FPGA and GNU Radio together.

# 4. Project Development: GNU Radio

GNU Radio is a multifaceted, complex tool which we have used throughout the majority of this project. We performed initial test runs of tasks such as FM transmission with GNU Radio on its own, and later integrated our FPGA into the pipeline. We also investigated the lower-level functionality of GNU Radio, and made an attempt at creating a signal processing block. Toward the end of the three-term project, we attempted more complex tasks such as differential binary phase-shift keying (DBPSK) modulated digital transfer of data via TCP/IP tunnel and direct transfer. We integrated the FPGA into the latter with a loopback configuration to show our progress on hardware integration within GNU Radio up to that point.

## 4.1 Integrating the FPGA and a Host Application (GNU Radio)

GNU Radio is a Python- and C-based API that is used for a wide variety of software-defined radio applications, such as amplitude modulation (AM) transmission, frequency modulation (FM) transmission, packet handling, filtering, et cetera. In particular, portions of the API are dedicated to the operation of the USRP. Since we are using the USRP as our analog front-end, this provides an important glimpse into how software-defined radio tasks are carried out in terms of the host PC. On a general level, the API functions by having component classes (filters, etc.) and functions coded in C, with Python code segments connecting the blocks. Most Python segments literally contain only configuration for the blocks required, then several instances of calling a 'connect' function on itself to construct the order of the pipeline. The FPGA peripheral will ultimately do the intensive work for our platform; much of the pipeline will not be implemented in GNU Radio. However, the basic structure that it provides for its pipelines can give us a framework for our own.

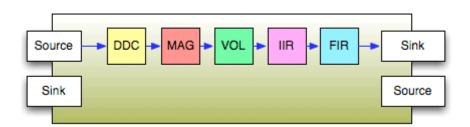

An example is the file am\_rcv.py included with the GNU Radio API. This file, as its title suggests, sends and receives amplitude modulation (AM) frequencies. The first block is a digital down converter (DDC), used to select a narrower band of frequencies to receive from the wide array of AM frequencies available. Then the magnitude of the DDC output is taken (MAG) to have a strictly real input, and the volume is scaled down (VOL). This is followed by deemphasis (IIR) and an audio filter (FIR) to reduce noise, and the data finally gets output to the audio sink (in other words, it is played on the computer's speakers). The same process could, theoretically, be followed in reverse to transmit on AM frequencies. A visual representation of the AM pipeline can be found in figure 4.

Figure 4: An AM radio pipeline from GNU Radio. This highlights the top-level structure of a typical GNU Radio pipeline.

In addition to introducing template ideas, GNU Radio also provides infrastructure for the management of data source and sink in our design. GNU Radio already contains functions for creating a file as a data sink and for using a file as a source. With this format, the FPGA can send/receive data with general UNIX file IO. Even though it appears to be the case on the software level, the data is not actually stored in a file. The "files" in question are actually calls to

functions that work in kernel space, directing anything written to them to addresses representing the desired peripheral IO and pulling anything read from them from the same addresses. File IO is notorious for being slow under normal circumstances, but this is due to the medium used. If located on the PC's hard disk (as per usual), file IO is slow. However, the file IO API itself is not.

GNU Radio's top-level applications are implemented in Python, while our FPGA is configured using a bitmap synthesized from Very High Speed Integrated Circuits Hardware Development Language (VHDL) or Verilog. Both are expected to perform within the same pipeline. This distinction in languages begs the question: how do the two languages interact with one another? Within GNU Radio exists wrappers which convert the C objects in the library into Pythonfriendly code. While we have no such wrapper to integrate the FPGA into code manageable by Python, there is an elegant option. The concept of device-nodes exists in UNIX, and transcends both programming languages. The FPGA will be configured using an API that is set up apart from GNU Radio. This will consist of blocks created within the XILINX ISE that are combined by the API and applied to the card. Our drivers will establish device-nodes for the FPGA card's IO and configuration, requiring a request to the kernel for information regarding where the FPGA expects to receive configuration data, receive input, and deliver output. Input, output, and configuration streams will be functions that are expressed in UNIX as files that actually store information in a buffer before moving it to its specified location. With this established, the FPGA (and therefore all of the pipeline elements within) will be treated as a file by the rest of the computer.

The end result (once drivers have been written) is that configuration of the pipeline occurs in two phases. First is the configuration of the FPGA. As long as components loaded to the FPGA are contained within the API, no use of XILINX ISE would be necessary. It would only be a matter of appending preexisting files to the configuration "file", with specification of which portion of the FPGA it should be written to. The driver will then load the file to the expected location on the FPGA. This will be where all blocks expected to be implemented by the FPGA will be configured, primarily modulation tasks (encoding, filtering, mapping, etc. - this will vary from standard to standard). This will be followed by configuration of the data management portion of the pipeline (multiplexing, etc.), which is best dealt with by the microprocessor [21]. Any tasks the microprocessor is expected to accomplish will be managed by manipulating GNU Radio conventionally.

The USRP is connected via the PCs USB and not through the FPGA, so the microprocessor can still access the USRP and manage configuration, card selection, and initialization. The FPGA's and microprocessor's tasks in the pipeline are distinctive enough that they can be kept separate in most situations. In the overall pipeline arrangement, the FPGA is generally "closest" to the RF front-end, being the first to affect receptions. It reads in and writes out to the USRP and PC as needed, using the device nodes that the drivers have established. The GNU Radio portion takes in the data stream from the output device-node of the FPGA, and interprets it as a file source.

From here GNU Radio can instruct the microprocessor to do any data management required, and then output the received data in whatever medium is desirable (sound, video, another file, etc.). For transmissions, the reverse of this process is true. GNU Radio will manage data from the

source device (microphone, camera, etc.) in preparation for transmission, and deliver it to the FPGA as though the FPGA were a sink. The FPGA will do its modulation tasks, and stream the modulated signal to the USRP (using GNU Radio, MATLAB, etc.) for transmission.

The FPGA really shines at implementing specific tasks in hardware. The computer is ideal at moving data around and manipulating it. Our scheme uses each component for its ideal task. In addition to providing an interface, device nodes allow for GNU Radio to be replaced by any software that can stream to/from a file, such as MATLAB. The reason GNU Radio is mentioned by default is that it is beneficial for the RF front-end we are working with (the USRP). Since the RF front-end itself is variable with respect to our FPGA, this platform is not limited to GNU Radio's standard API.

#### 4.2 An Exercise – FM Transmission with GNU Radio

In initial attempts at FM radio manipulation, there were some technical difficulties. Investigation into the problems entailed rereading the GNU Radio tutorials by Dawei Shen, as well as consulting with grad students in the lab [19] [20]. The tutorials helped to narrow the problem down to being one regarding the configuration of the daughterboards on the two USRPs. With the provided programs usrp\_siggen.py and usrp\_oscope.py, a signal could be generated and transmitted from one of the USRPs, and a graphical oscilloscope could be used to verify that the signal was being received. After a couple of earlier failed attempts at simply running the transmission and reception with file storage (resulting in static as before), using this graphical diagnostic swiftly and conveniently verified which motherboard configuration functioned properly. This entailed connecting RX A of one USRP's Basic RX daughterboard and TX A of

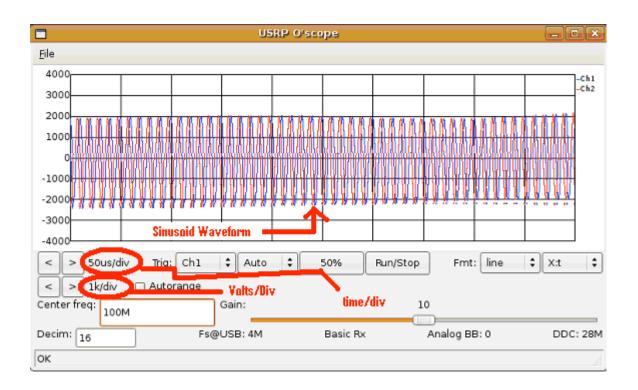

another's Basic\_TX daughterboard with a copper wire. As is visible in figure 5, the configuration described functions properly, delivering the signal to the receiving computer.

Figure 5: Daughterboard Testing Signal. As can be seen, the signal output is a sinusoid, with amplitude at approximately 2000. The center frequency upon which the signal is received is 100 MHz.

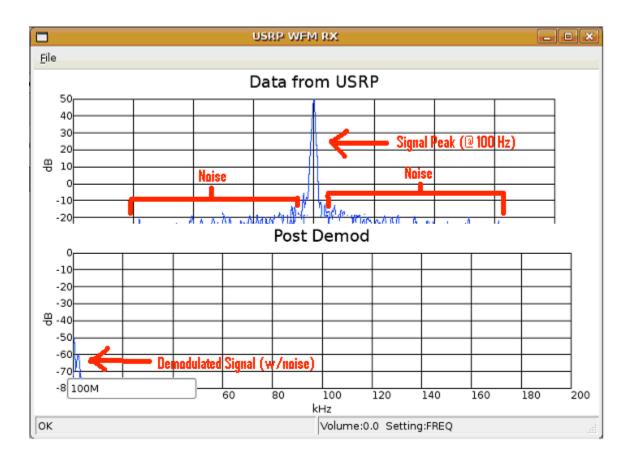

With that obstacle set aside, the efforts that were taking significant time now moved swiftly. However, there were still some slight modifications made, which made the receiving end easier to configure, as well as confirm to be functioning. Namely, this involved modifying <code>usrp\_wfm\_rcv.py</code> instead of <code>usrp\_wfm\_rcv\_no\_gui.py</code> for receiving the transmission and writing it to a file. Initially the non-GUI version was used as a base since the code was less complex, but the GUI version bore a greater resemblance to the code in the tutorial. It also displayed the current frequency and volume settings, as well as pre- and post-modulation signals (see figure 6). With this information, it was possible to adjust the gain and volume settings, and

observe the effect. Ultimately, a gain of 50 dB, a volume setting of 100, and a center frequency of 100 MHz were used to provide a file with a suitable tone. Some of the volume was still lost from the receiving end, but this could have been resolved by increasing the gain further, or simply using a tone with greater amplitude such that the loss was less noticeable. However, it was sufficient to conclude that the tone file was indeed being transmitted from PC to PC. The tone was noticeable when played using audio\_play.py.

Figure 6: Frequency response of FM Signal Reception. Prior to demodulation, there is a distinct peak at 100 MHz, with smaller peaks and noise trailing off. Post-demodulation, the frequency response is what figure 3 indicates: a sinusoid at rather low frequency (approx. 500 Hz).

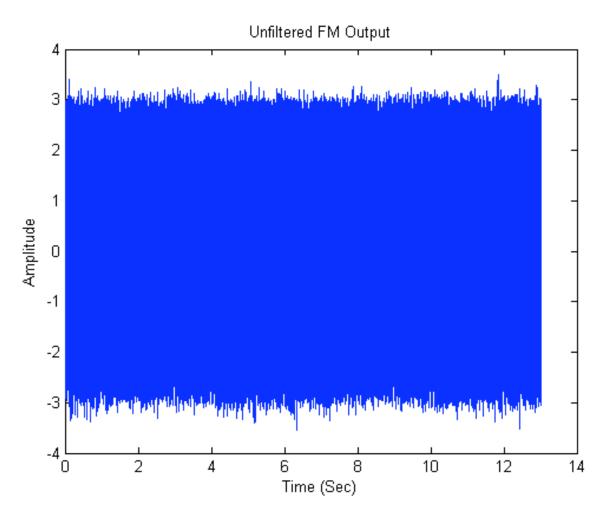

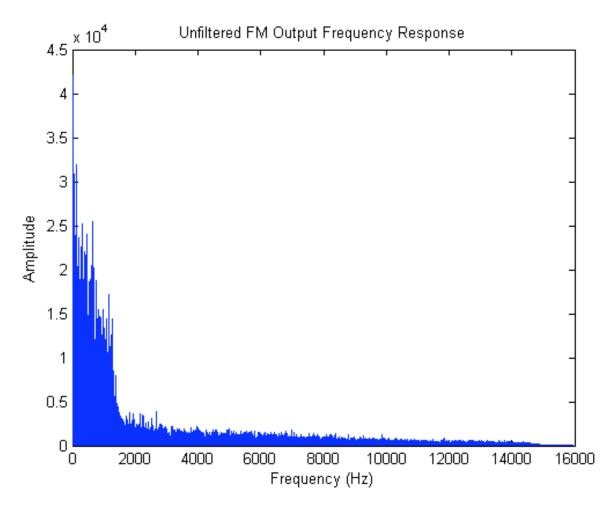

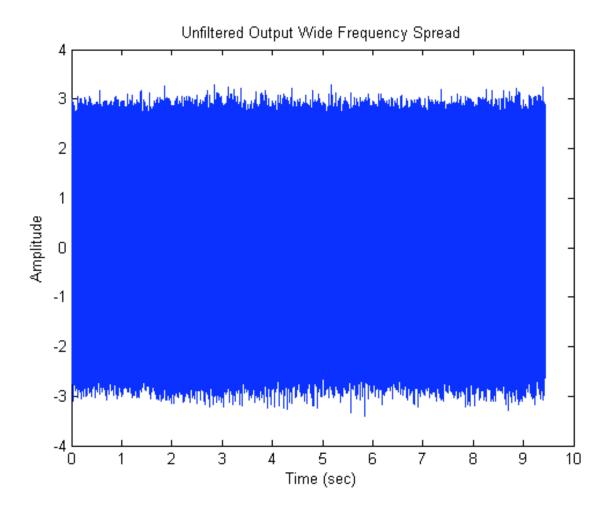

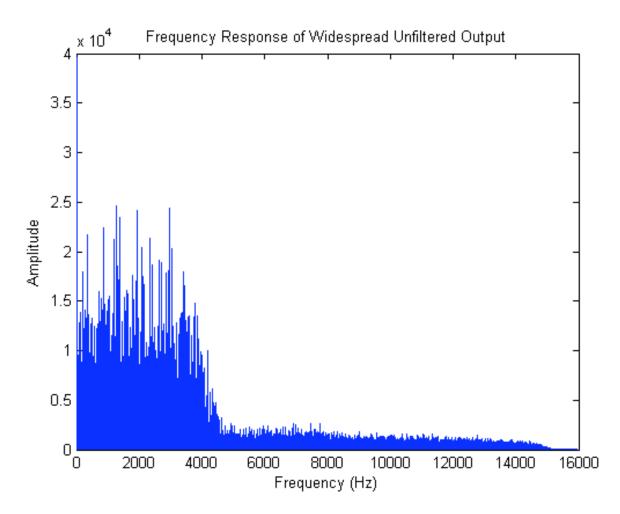

#### 4.3 Preparing FM Transmission applications for FPGA Integration

The integration of the FPGA into the receiving computer, with GNU Radio in a pipeline took priority. Whether the FPGA was integrated into transmission or reception was an arbitrary decision, though it does determine which direction program implementation initially progresses in.

To this end, most of the PC-side resources were already available or almost available at that point. The components required were as follows:

- An FM transmission program that takes data as audio from any specified file

- An FM receiving program that receives from a file (ultimately the device-node for FPGA output), demodulates, and plays back or stores as another file

- Programs to generate/play back audio files (audio\_to\_file and audio\_play, already provided in gnuradio-examples).

The FM transmission program was hard-coded to accept files with specific names (audio-N.dat, where N is a number from 0-7) in the same directory as the program. With some modification to this, the program was made such that the name and location of the file to be transmitted could be specified in the command line. To confirm functionality, the same test that was implemented with the hard-coded file source was run again, but giving the program a file with a different name and location. The results were the same as before – the tone was received on the other computer, with volume slightly reduced. This program will prove useful in a wider

array of situations, going beyond testing – ultimately the user would want to transmit files that were not necessarily in the same directory as the program.

The FM reception program receives data from a specified file (i.e. the device-node), demodulates it as though it was FM signal from a USRP, and stores it away in another file. Given prior experience modifying sources and sinks, and testing the reception code with a USRP source, the program is somewhat reliable. However, the program needed FPGA loopback implemented before we could be certain it was functional. When the FPGA was ready and set up on a computer with a USRP and GNU Radio, all that needed to be done to the program in addition was specifying the device-node directory when executing the reception program in the command line.

To prepare for the successful integration of the FPGA, one question still remained to be answered at that point – does GNU Radio treat device-nodes as ordinary files? To ensure that the device-node concept functioned properly with GNU Radio, a quick test of the functionality of a preexisting device node, /dev/urandom, was executed using audio\_play. As expected for being supplied random integers, the program output consisted of distinct, loud white noise. So, it can be said with that in cases requiring a file to be specified, a device-node can be specified in its place.

Either way, the pipeline can be implemented in its simplest form on the software end at this stage. With FPGA drivers that are up to speed, all that needs to be known in addition is the

directory and name of the FPGA output device-node. The primary GNU Radio milestone for the first term was achieved with the completion of this pipeline.

#### 4.4 The GNU Radio Signal Processing Block

At the beginning of B term, the development of the signal processing block has hit a couple of obstacles. First, there were many errors that needed to be worked out in the automake configuration of the block. These were largely due to the abstract nature of the automake system, and the fact that the tutorial was outdated and vague in that section. The only really way to ensure the automake functioned properly was to attempt compiling and see all the errors that came up. There were many such errors, most of which lay in the files configure.ac (Error 1) and randsig.i (Error 2, Error 4). These were relatively minor syntax errors in retrospect, but were difficult to spot because they were either small or did not appear as issues in the tutorial (which was written using an older version of configure.ac. The two most time-consuming errors to deal with were errors 1 and 2.

```

/usr/bin/m4 failed with exit status: 1

'is already registered with AC_CONFIG_FILES.

../../lib/autoconf/status.m4:300: AC_CONFIG_FILES is expanded from...

configure.ac:126: the top level

autom4te-2.61: /usr/bin/m4 failed with exit status: 1

autoheader-2.61: '/usr/bin/autom4te-2.61' failed with exit status: 1

'is already registered with AC_CONFIG_FILES.

../../lib/autoconf/status.m4:300: AC_CONFIG_FILES is expanded from...

configure.ac:126: the top level

autom4te-2.61: /usr/bin/m4 failed with exit status: 1

automake-1.10: autoconf failed with exit status: 1

```

Error 1: This was an issue with the configure.ac file. It was difficult to identify, since the latest version of the file differs from the one showcased in the tutorial on how to write a signal processing block. It was addressed by swapping out the more recent version for the older version, and then pulling a fresh copy of configure.ac from howto-write-a-block and modifying it again.

```

randsig_source_ff.h: In function 'PyObject* _wrap_source_ff(PyObject*,

PyObject*)':

randsig_source_ff.h:74: error: too few arguments to function

'randsig_source_ff_sptr randsig_make_source_ff(double)'

randsig.cc:4335: error: at this point in file

```

Error 2: This error appeared at first to be an issue with the header file. However, it was actually a matter involving the file randsig.i, in which there was a parameter mismatch with respect to the rest of the code.

Ultimately, the processing block compiled and tested successfully.

Another technical problem had presented itself with the implementation of the processing block, and this is one that has yet to resolve itself. While the module can be imported in the test \*.py file by using the line import randsig, using this line did not work properly in a \*.py file placed in the GNU Radio example directory. Instead, error 3 was displayed.

```

Traceback (most recent call last):

File "./usrp_randsiggen.py", line 4, in <module>

import randsig

ImportError: No module named randsig

```

Error 3: "Missing" randsig module. The program could not find our new library, and did not function as a result.

This implies that the module cannot be found. Probable causes for this were investigated – changing the \*.py file's directory such that it is the same as the one where the working \*.py is located, changing the import line to from gnuradio import randsig, checking the directory where all modules should be stored (/usr/local/lib/python2.5/site-packages) to ensure that it is in fact located there – all of these possibilities checked out fine. The issue was resolved within a few days. It was a matter of the pythonpath being unspecified. This still seemed unusual, since other GNU Radio applications functioned properly, but specifying the path got rid of the error. However, this only revealed another error (Error 4)

```

Traceback (most recent call last):

File "./usrp_randsiggen.py", line 122, in <module>

main ()

File "./usrp_randsiggen.py", line 96, in main

fg.set_interpolator (options.interp)

File "./usrp_randsiggen.py", line 29, in set_interpolator

self.siggen.set_sampling_freq (self.usb_freq ())

File "/usr/lib/python2.5/site-packages/gnuradio/randsig.py", line 100, in

set_sampling_freq

return _randsig.randsig_source_ff_sptr_set_sampling_freq(*args)

AttributeError: 'module' object has no attribute

'randsig source_ff sptr set_sampling_freq'

```

Error 4: Missing randsig\_source\_ff\_sptr\_set\_sampling\_freq attribute. It is a variable not defined in randsig.i that is used in the \*.py implementing the processing block, which causes the program to terminate.

This immediately raised red flags about either the header file or the \*.i file not containing information about set\_sampling\_freq(). Sure enough, the \*.i file had no accessors or manipulators declared, and this was changed to attempt to remedy the error. randsig was rebuilt, though, and the error remained. Even with deleting all files generated by the last make and running make again, it still remained. This error message was dealt with by changing the \*.i file as mentioned above, and deleting the copy of the randsig module installed in /usr/lib/python2.5/site-packages/gnuradio as opposed to /usr/loca/lib/python2.5/site-packages/gnuradio. At this point, after editing out a couple of syntax errors that did not get detected in usrp\_randsiggen.py, the python file executed without errors. The waveform would either change erratically, or always remain the same. However, it was producing improper waveforms on the receiving oscilloscope. Modifying the code to integrate srand() and ensure that the waveform object was only initialized once, proved ineffective. At this point, it was thought best to turn to establishing a working secure shell (SSH) tunnel now that one of our lab computers does not seem to be functioning properly.

# 4.5 Digital Communications – Implementing DBPSK

#### 4.5.1 A Demo – DBPSK Modulation over TCP/IP

The differential binary phase-shift keying (DBPSK) tunnel is a fairly straightforward process, implemented on two computers: our workbench computer (containing the FPGA), and our primary lab computer out of two lab computers that were accessable. The primary lab computer worked as expected on the first try. However, our secondary lab computer and the workbench computer both had technical difficulties. The former seemed to have something malfunctioning within the boost C++ library that was installed, and the latter was missing the Universal tunnel/network tap (TUN/TAP) Driver. With brief collaboration to properly configure our workbench computer, we had two computers which supported tunnel.py (included in the GNU Radio trunk for implementing TCP/IP tunnels). DBPSK modulation can now be set up on both terminals (workbench computer's example shown below), but lack of privileges on the primary lab computer made scheduling a test for simultaneous operation take longer than expected. It was a trivial matter from there, once the proper privileges were available.

There were some minor technical difficulties while implementing tunnel. The RFX daughterboards were transmitting, but not receiving packets. This was at first resolved by switching to basic TX/RX, but that operated on lower frequencies (in the MHz range rather than GHz), and as such gave less ideal performance in terms of speed, but more importantly range. Ultimately, we realized that the fact that all other wireless on campus was operating at 2.4 GHz resulted in interference with our tunnel. With that, we attempted to operate the tunnel on RFX boards at slightly a slightly different frequency, and it functioned properly. Another way of improving the speed of throughput was to reduce the maximum transmission unit. This way, if

errors occurred in packets, smaller amounts of data would be lost and require transmitting again. The ideal number found for this application was around 300 bytes. This was determined through trial and error. 300 bytes was the highest packet size that did not result in packet loss, and anything less than this would increase transfer times unnecessarily. This may vary from situation to situation, but it can be trivially changed with ifconfig.

We have investigated the inner workings of tunnel.py, and realized that poor documentation of where certain signal processing blocks are and how they work is a tremendous drawback. This resulted in consulting the mailing list, and attempting a temporary solution while waiting for a response. That is, to write code to manipulate the simulated Ethernet connection between the two USRPs on the OS level. Initial attempts at this were highly cumbersome – first generating a signal and storing it to a file (similar to what has been done before), then using system calls to execute SCP in the shell, requiring python executables to be manually run on both ends. Working with Alex, another solution was designed. This involved compressing a file and moving it through an SSH pipe. The SSH pipe called an executable file on the receiving computer, which established a pipe in the opposite direction and sent the file back to a different directory on the transmitting computer. This could be done with manual execution of only one file (file transmitter.py), and was far more effective than calling SCP.

This is still not the ideal case. It works on the OS level, exploiting SSH to accomplish the required goals, and as such is somewhat slow. It is at least a good exercise in implementing GNU Radio applications for other tasks. It would be much more efficient to redirect transmitted data with GNU Radio directly. The most significant question is how to supply the digital

transmission/reception applications (benchmark\_tx.py, benchmark\_rx.py, or processing blocks that are subsets are these) packets or streams of data directly.

### 4.5.2 Initial Attempts at a Lower-Level Approach

A data streaming design works in theory, but not in practice. This is due to a hardware limitation preventing daughterboards from transmitting and receiving simultaneously, which is a requirement for data streaming. The tone transmitted was not received, and the approach had to be discarded in favor of packet-based data transfer. However, this took a significant enough portion of time to warrant mentioning here, as a path not to go down for future researchers or as a starting point to work off of if the hardware flaw prohibiting simultaneous transmission and reception of streams is no longer an issue in the future.

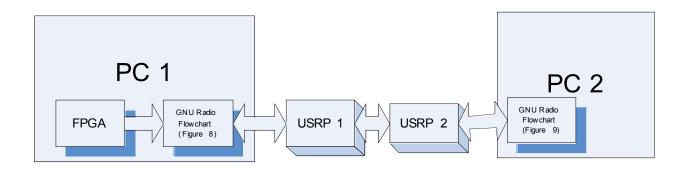

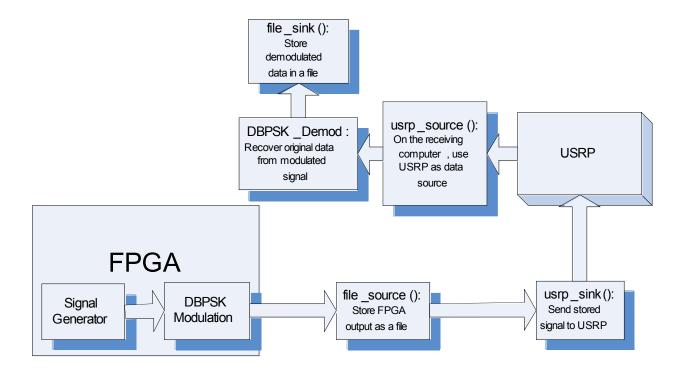

Much of the time investment for this design was directed toward seeking a reference for what signal processing blocks were available to us, as well as how the benchmark\_tx and benchmark\_rx applications work. Ultimately, we boiled it down to the use of lower-level blocks than benchmark\_\*, and avoided using them in this case entirely. This is because they inherently include modulation blocks, and we will want to insert already modulated data into the pipeline from the FPGA at some point. As a result, we replace the benchmark transmission/ reception with a series of less complicated blocks, including file\_source(), file\_sink(), dbpsk\_demod(), usrp\_source\_c(), and usrp\_sink\_c(). The arrangement of these blocks is expressed graphically in figure 7, with figures 8 and 9 showing lower-level contents of the GNU Radio flowcharts.

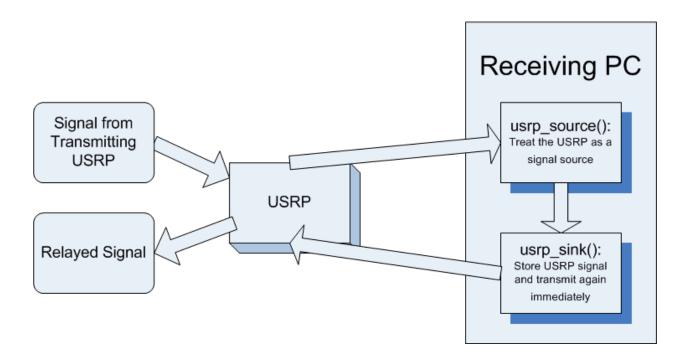

Figure 7: A top-level diagram of the pipeline. The FPGA on PC 1 supplies data to the flow graph, which relays across the USRPs to the PC 2. The flow graph of PC 2 redirects anything received back to USRP 2. The The two GNU Radio flow graphs are quite different and vary in complexity, as is show in figures 2 and 3.

Figure 8: The planned GNU Radio flow graph for PC 1, along with the tasks allotted to the FPGA. This includes all signal processing blocks that should be needed, presuming DBPSK modulation was implemented on the FPGA. The FPGA is represented by a character device node, and treated as a file source. Anything received by the USRP from PC 2 is interpreted as a USRP source, demodulated as DBPSK, and stored as a file. In the initial development process, prior to writing a DBPSK modulation block for the FPGA, the signal processing blocks sig\_source\_c() and dbpsk\_mod() can be used as a replacement. For this to function properly with only the blocks in the diagram, the FPGA must output the generated signal as complex numbers. This design was not completed, as streaming data transfer only works unidirectionally with GNU Radio.

Figure 9: The GNU Radio flow graph for PC 2. Quite simply, it interprets the USRP as a source, and immediately directs any input back to the USRP as a sink. This is a loopback, so the receiver is a "dummy", for the moment only determining the functionality of the transmitter.

# 4.6 The Current Concept – A Packet-Based Approach

#### 4.6.1 Unidirectional Communication

To resolve the problems present in stream-based data transfer, we further examined the benchmark\_tx.py and benchmark\_rx.py applications. They could be adjusted to transmit to/from files by implementing file I/O, having payload be read from a file using read() and the received payload (with the exception of the two least significant bits) using write(). It was a matter of knowing how to implement file I/O in python, and knowing where to place the read/write functions. We had come to this realization after stumbling upon similar modifications

for benchmark\_tx, and developed the benchmark\_rx modifications completely independently, using the newfound knowledge that we could use file I/O to modify and read the payload string.

With these modifications, we now have unidirectional file transfer done properly – in a way that can later be altered for new modulation options (the module where the benchmark files select their modulation type, mod\_pkts, has been identified), and is far more favorable to integrating the FPGA. For instance, the function generator we used at the end of A term for FM transmission could be implemented as a file source again. And if a DBPSK block is written for the FPGA, that can be used and GNU Radio modulation can be removed.

#### 4.6.2 Bidirectional Communication

The initial attempt at a relay for bidirectional communication (stream-based) also had to be abandoned for a packet-based application, as the RFX2400 boards inherently cannot transmit and receive at the same time. The initial relay consisted of a USRP source and sink receiving and transmitting constantly (in theory). This does not work, because transmitting takes priority and the application never receives.

To remedy this, we shifted away from creating a stream and tried instead to implement packet exchange, as we had done in the alterations of his plan for unidirectional file transfer the prior. This requires taking timing constraints into consideration, since one computer must be receiving when the other is transmitting. The transmitter has a discontinuous mode, which sends a certain number of packets before waiting for some period of time. This proved ideal for synchronization, since the relay side could be made to know to receive a certain number of packets and then

transmit, and the originating side could wait long enough after packet bursts to receive a series of packets the same as it had just transmitted.

This application runs, but is unreliable. The RX callback function in the relay application (used for both transmitting and receiving) is called whenever packets are received. Therefore, for the last packet in a burst the relay USRP is attempting to transmit and receive at the same time, so the packet is never sent back. If the number of packets in a burst is significantly large and the file is a sine wave stored as a series of floats, this causes only minimal distortion to the final file, and it is still usable. The greater problem is that many packets transmitted by the relay are not properly received, and are dropped. Effectively implementing bidirectional communication had to begin on a smaller scale, transmitting individual packets of known contents rather than large files.

Implementing transmission of single packets with known packet contents in two directions proved to be a far more straightforward and less error-prone task. Over the first weekend of C term, we wrote programs for transmitting a user-specified string in a packet, relaying the packet back to the transmitting computer, and displaying the original string contents/storing them in a file. All of these tasks are now performed reliably. This was bought together with the FPGA in loopback once the driver (see Chapter 5) was functional. For more on the loopback integration results in this example, see Section 6.1.

### **Chapter Summary**

Over the course of this project we applied GNU Radio to a variety of tasks, and checked FPGA functionality (at least ostensibly, in the form of a loopback) at every stage. Ultimately, the FPGA

integration was intended to be used to replace certain tasks within the GNU Radio pipeline. In the following chapter, we will establish the architecture within the FPGA, and the means by which it interacts with the pipeline.

# 5. FPGA Architecture and GNU Radio Integration

# 5.1 Driver Development

The goal of the driver in this project was to integrate GNU radio and other applications such as MATLAB with the hardware running on the FPGA. Even though many environments can be extended to add new functionality using mechanisms such as MATLAB's MEX modules and GNU radio signal blocks we decided against using a specific solution similar to the solutions mentioned above due to accessibility reasons. We did not want to create a solution that tailored specifically to one data manipulation suite. Instead, we chose to implement the interface to our hardware as a UNIX device-node.

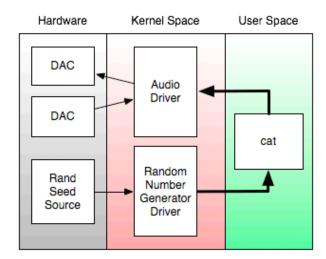

If we look at the way file-IO is implemented in a modern operating system we find a buffered bidirectional stream of data. This is why in UNIX derivitive operating systems the file metaphor is used to access a wide variety of hardware. A device driver would create and associate itself with a special virtual file called a device-node using device file system (devFS) or UNIX File System (UFS) and then read and write from the other end of the buffer. On a modern Linux system the following command:

cat /dev/urandom >> /dev/dsp

will result in static being played out of a user's speakers. The command reads the file "/dev/urandom" which is a device node created by the random number generator. This file provides random data every time it is read from. Then the output is redirected to the file

/dev/dsp which is the device node for the computer's sound card. Any writes to this file will cause the written value to be fed into the DAC in the computer's sound card. This forms a very rudimentary data pipline as depicted in figure 10. This example shows how the "device as a file" metaphor can be used to access hardware. A more controlled form of the above example could be implemented using the 'dd' command:

dd if=/dev/urandom of=/dev/dsp bs=4 count=10

This command would copy 10 units of four bytes of data from the random number generator to the sound card.

Figure 10: Visual Representation of cat /dev/urandom >> /dev/dsp forming a pipline.

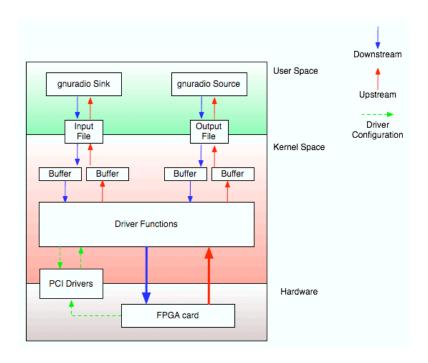

For our platform, we will represent the configuration interface and both ends of each synthesized pipeline as device-nodes. Figure 11 shows how our driver would interact with the hardware on one end and the host application on the other end.

Figure 11: A flowchart of the driver we use to push data to and from the FPGA

This method of design in addition to providing a easy to use interface abstracts the hardware specific details and leaves them in the domain of the driver. As long as the same interface is provided to the software portion of this problem the hardware and driver can be modified without adversely affecting the software and breaking compatibility.

## 5.1.1 PCI Initialization

PCI express is an extension of the original PCI bus that replaces the physical parallel bus with a much faster multi-serial packet based PHY. From a software level, however, it was designed to look and behave similar to a PCI bus so much so that a system that is unaware of PCI express can treat it as a plain old PCI bus and function properly.

PCI was designed to replace industry standard arhitecture (ISA) which was an extension of the 80286's processor bus. In addition to increasing performance, PCI included features such as architecture independence, plug & play, auto configuration, and hot plug support. Both buses allow the host system to communicate with hardware using memory mapped IO. This means that once our card is configured we can access it as if it was memory. However, some of these advanced features make setting up the card complicated.

When a PCI card powers up initially, it only responds to configuration requests. On a PCI bus there are three memory spaces: Memory, IO, and configuration. Memory and IO address spaces behave as they do on ISA, cards get mapped to specific address ranges and can be accessed by using IO and memory transactions. However, the configuration address space exploits geographic addressing. This means that no two cards will have conflicting configuration addresses. Using this configuration space the host can then configure specifically what addresses the card can respond to and achieve plug and play support without having the IO and memory be geographically addressed.

When the system boots, the BIOS (or the OS) crawls through the bus and makes sure that no two cards are conflicting with each other and have their memory regions (specified in the configuration registers) mapped into system memory. Our driver has to associate itself with the card and perform some configuration. The card type can be identified by the vendor and device pair. XILINX has a vendor ID of 0x10EE and we assigned the device ID of 5050 to our card. We then register two callback functions with the kernel telling it what it should do if our card

(specified by the tuple) is added or removed from the system using the pci\_register\_driver() function.

Using the callback "probe" mechanism, we now have a way of finding and working with our card. The "Add" function has to do three things. Initialize the card, Find out what base address has been assigned to the desired BAR (memory block) and configure the system's memory management hardware to set up a mapping between our virtual memory and the system's physical memory for that specific range. The equivalent "virtual base address" is stored in a struct for later use.

```

// enable card

ret = pci_enable_device(dev);

if (ret < 0) return ret;

printk("Device enabled sucsesfully\n");

// configure translation for BAR0

mem_start = pci_resource_start(dev,0); // reigon zero. BAR0

mem_len = pci_resource_len(dev,0);

map=request_mem_region(mem_start,mem_len,"driver");

m1506.vmemadd=ioremap(mem_start,mem_len); // save the virtual address

m1506.memadd=pci_resource_start(dev,0);

m1506.memlen=pci_resource_len(dev,0); // We now know where our card is in memory and can access it using memory transactions.</pre>

```

The "remove" function removes this mapping and disables the card, cleaning up after the "add" function. Once the "add" callback function is called by the kernel our card can now be accessed by simply writing into the memory range specified by the "virtual" base address and the length of the memory block.

#### 5.1.2 Character Device Initialization

A character device from the user's point of view is a file. One can read and write to this file as well as seek to an arbitrary position in the file much as you do with any other file. In this case, however, all file operations are handled by our own functions that read and write to registers on the peripheral card.

There are two numbers that represent our character device when combined. These are the major number assigned to the driver and a minor number that the driver assigns to the character device. In our driver since we only have one device we chose a minor number of zero. To register a character device we first need to create a structure with pointers to our handler functions. We then pass this pointer to the kernel along with a minor number using the register\_chrdev() function. This function returns our major number. To create the device node we use the command mknod this way:

mknod /dev/device 253 0

This makes a character device and connects it to driver 253 char device 0. Any interactions with this file will cause our callbacks to be called.

#### 5.1.3 Character Device Data Functions

The four required character device functions are device\_read, device\_write, device\_open, and device\_release. These functions get called when our device node is read from, written to, opened, or closed. These are the function prototypes for the four character device functions:

```

static int device_open(struct inode *, struct file *);

static int device_release(struct inode *, struct file *);

static ssize_t device_read(struct file *, char *, size_t, loff_t *);

static ssize t device_write(struct file *, const char *, size t, loff t *);

```

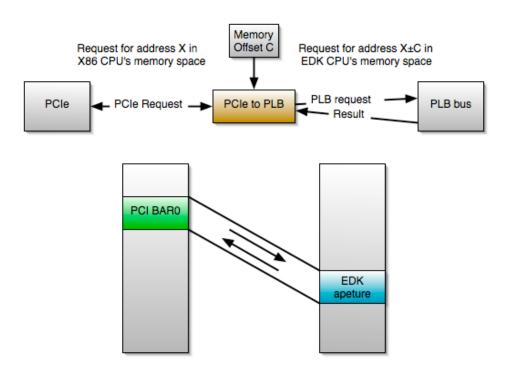

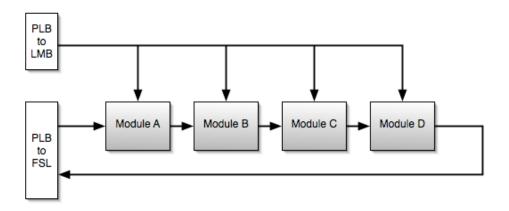

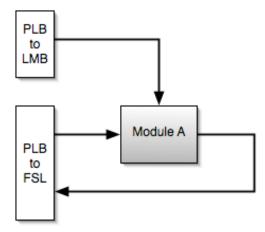

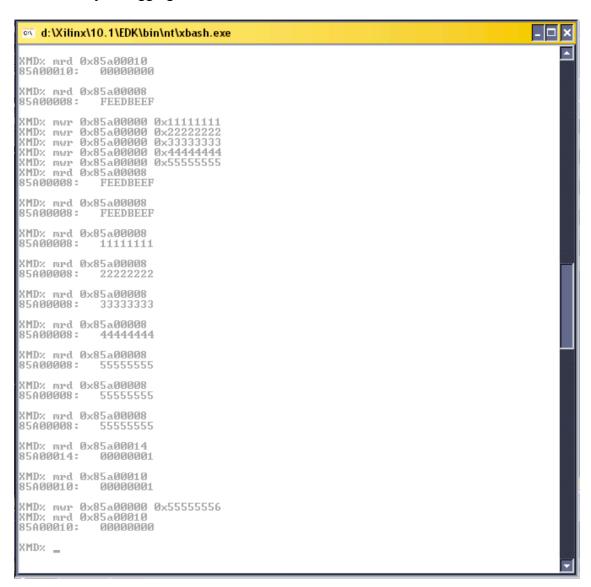

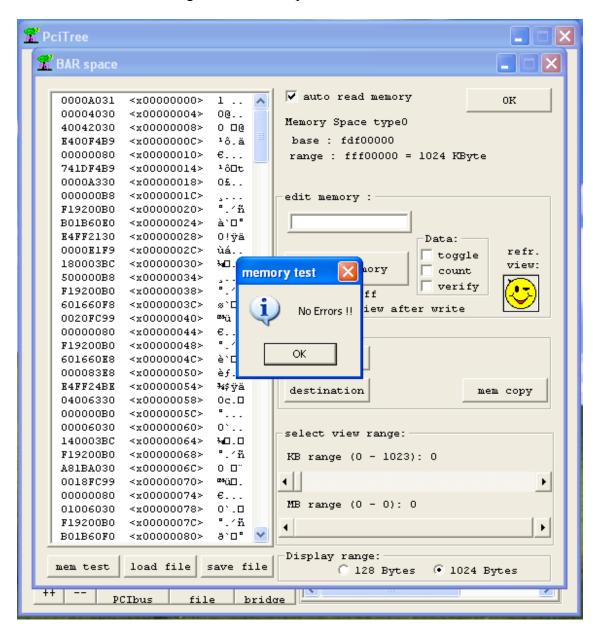

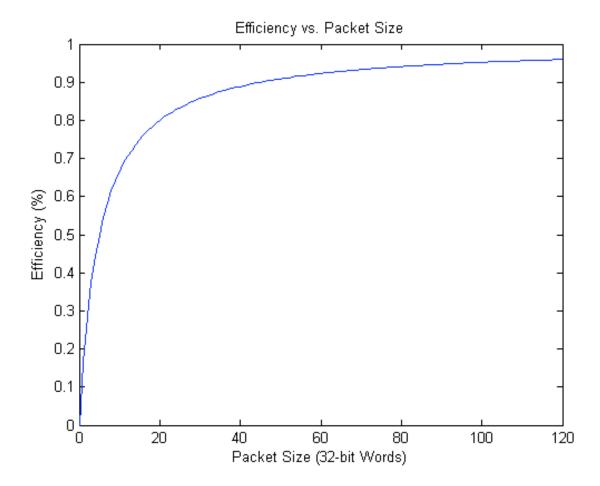

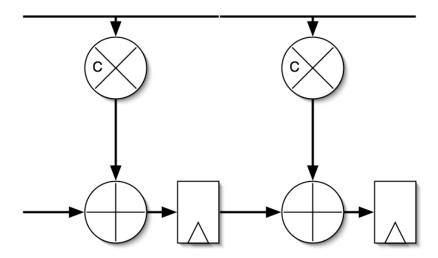

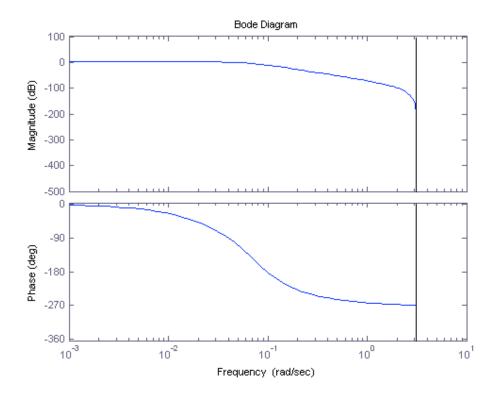

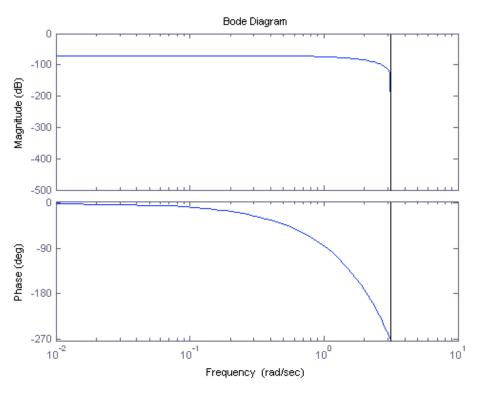

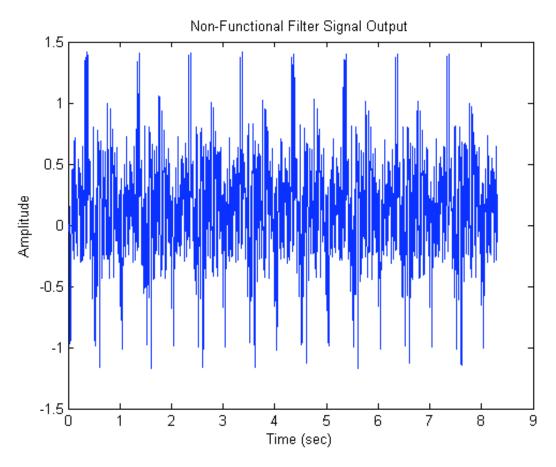

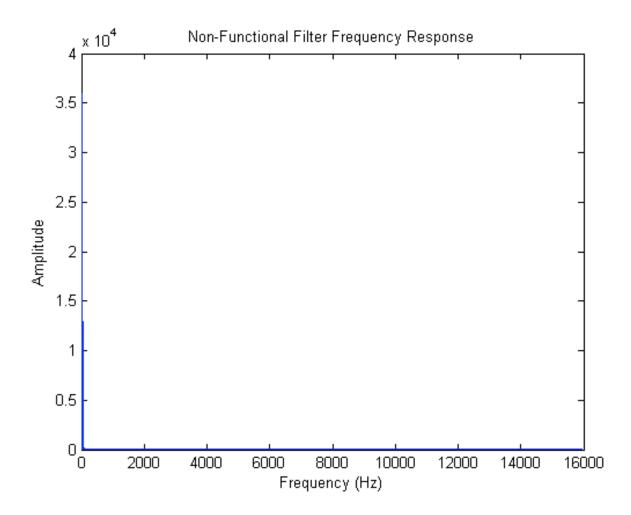

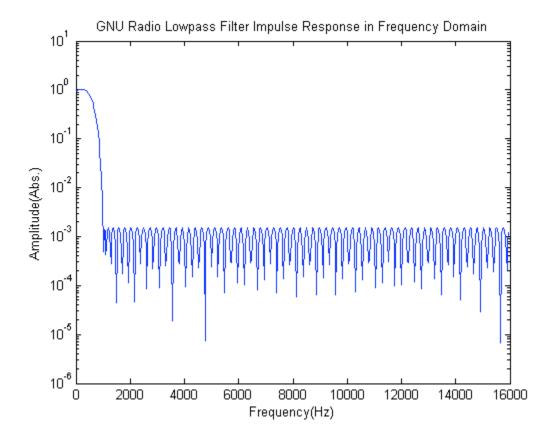

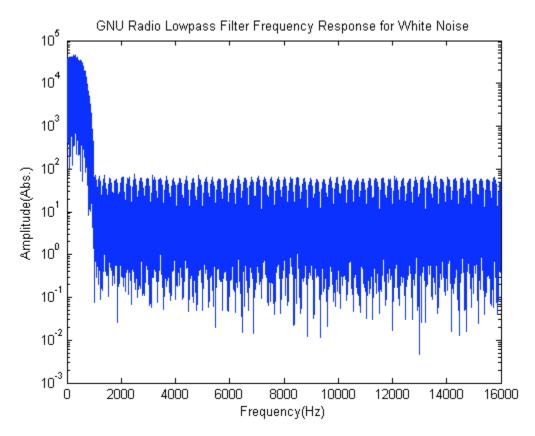

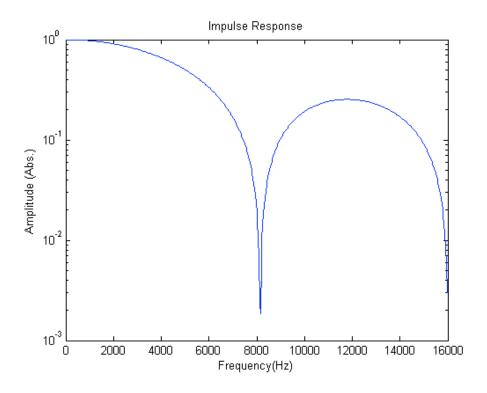

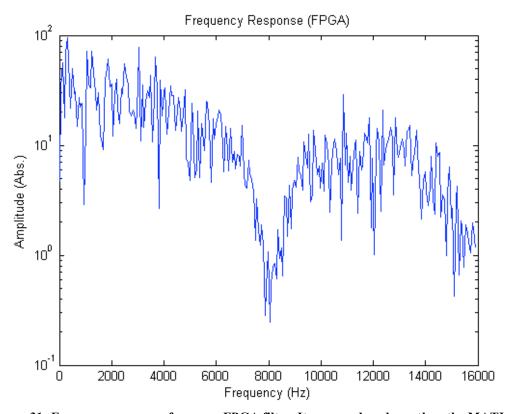

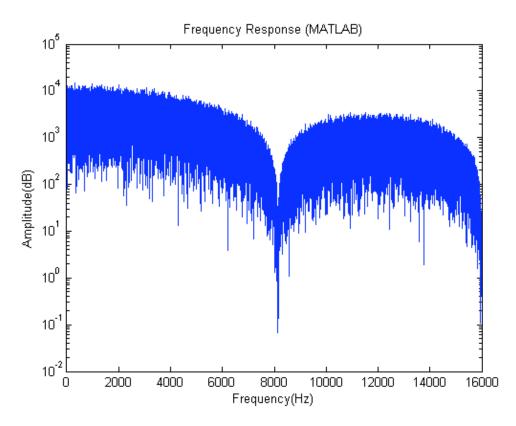

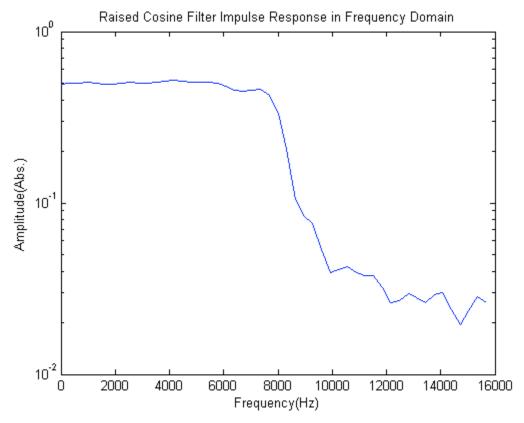

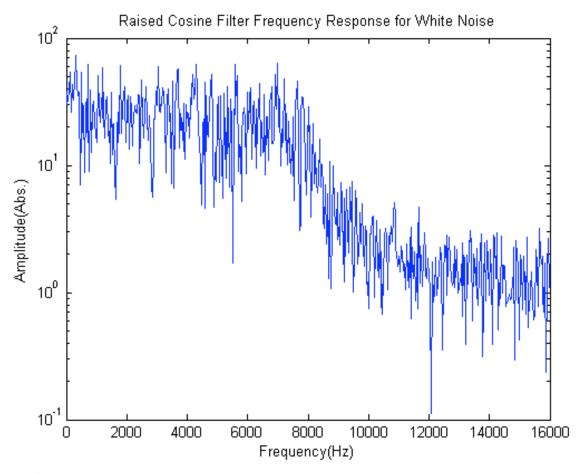

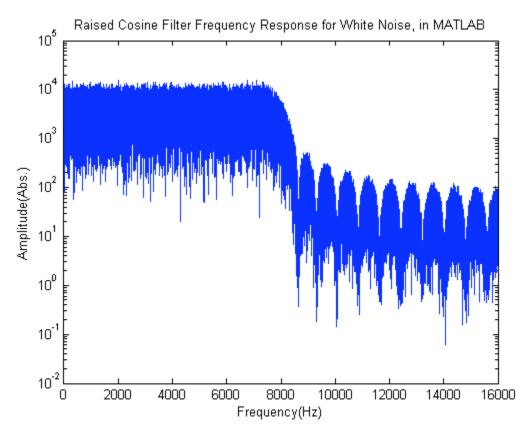

In our situation the two important functions that contain the bulk of our code are the "device\_read" and "device\_write" functions. These functions contain a pointer to a user space buffer, the length of bytes to be written, and the offset into the file. For our application we ignore the offset because our file has infinite length and seeking is irrelevant in that context. The function's return argument is how many bytes where written.