Project Number: MQP-BYK-GD07

# Self-Healing Partial Reconfiguration of an FPGA

| A Major Qualifying Project Report:                 |                      |

|----------------------------------------------------|----------------------|

| Submitted to the Faculty                           |                      |

| of the                                             |                      |

| WORCESTER POLYTECHNIC INSTITUTE                    |                      |

| in partial fulfillment of the requirements for the |                      |

| Degree of Bachelor of Science                      |                      |

| by                                                 |                      |

|                                                    |                      |

| Evan Custodio                                      |                      |

|                                                    |                      |

| Brian Marsland                                     |                      |

| Date: April 26, 2007                               |                      |

| Sponsored by:                                      |                      |

| General Dynamic C4 Systems                         |                      |

| Approved:                                          |                      |

|                                                    | Professor Brian King |

# **Abstract**

The goal of this project, sponsored by General Dynamics, is to create an FPGA-based system capable of detecting and gracefully recovering from errors without compromising system functionality. Previous research developed a prototype for partial reconfiguration, but a major limitation was the need for a PC to partially reprogram the FPGA. By implementing a method of self-reconfiguration and developing a system using triple module redundancy, the FPGA can locate errors and partially self-reconfigure the corrupted areas while maintaining valid system outputs.

# **Acknowledgements**

We are extremely grateful to both General Dynamics C4 Systems and Worcester Polytechnic Institute for the opportunity to complete this project. Without the cooperation of everyone involved, this project would not have been possible.

We would like to thank Professor Brian King for advising this project in the absence of Professor Berk Sunar. Even though it is not in his usual field of study, Professor King was a tremendous help throughout the term. We are especially appreciative of his efforts to help us complete this project within the constraints of the shortened D-term schedule.

We would also like to thank Professor Berk Sunar for making this opportunity available to us. Although he was unfortunately unable to take part in the specific details of this project, this project and its sponsorship by General Dynamics C4 Systems would not have possible without him.

We are also grateful for the constant support provided by Brendon Chetwynd and Gerardo Orlando, our on-site advisors at General Dynamics. Brendon provided us with constant support throughout the term, both in technical and administrative aspects of the project. We appreciate Brendon's efforts in allowing us to take the FPGA development board to the WPI Project Presentation Day. We would also like to thank Gerardo for his high-level technical support in this project. He was often a few steps ahead of us in finding potential issues and points of consideration in our design.

Lastly, we would like to thank all of the previous MQP research teams that provided us with crucial background information for the completion of this project. Specifically, we would like to thank Mike Kristan, Brian Loveland, and Rob Sazanowicz, who completed the project "Dynamic Partial Reconfiguration of a Field Programmable Gate Array" in the previous term at General Dynamics. Their project provided a clear, step-by-step flow for achieving their results, which was a crucial starting point for the research and design necessary in our project. We would also like to thank Mike Lundy, who completed the project "A Self-Healing Circuit Implementing TMR" at General Dynamics in the previous year. Although we did not use the specific design implemented in his project, the research that went into his project was greatly beneficial to us.

# **Table of Contents**

| Abstract    |                                                      | ii  |

|-------------|------------------------------------------------------|-----|

| Acknowled   | gements                                              | iii |

| Table of Co | ontents                                              | iv  |

| Table of Fi | gures                                                | vii |

| 1 Introd    | uction                                               | 1   |

| 2 Backg     | round Review                                         | 3   |

| 2.1 F       | ield Programmable Gate Array                         | 3   |

| 2.1.1       | The Xilinx Virtex-II Pro XC2VP30                     |     |

| 2.1.2       | Single Event Upsets and Single Event Transients      | 6   |

| 2.2 P       | artial Reconfiguration                               |     |

|             | riple Module Redundancy                              |     |

|             | ractical Uses of Self-Healing Systems                |     |

|             | revious Work                                         |     |

|             | ools                                                 |     |

| 2.6.1       | Virtex-II Pro Memec Development Board                |     |

| 2.6.2       | Xilinx EDK 8.2.02                                    |     |

| 2.6.3       | Xilinx ISE 8.2i                                      |     |

| 2.6.4       | Xilinx PlanAhead 8.2.7                               |     |

|             | t Goals                                              |     |

| •           | 'op-level Goals                                      |     |

|             | echnical Goals                                       |     |

|             | echinear Goalsdology                                 |     |

|             | ool Flow                                             |     |

|             | Analysis Strategies                                  |     |

|             |                                                      |     |

|             | Design Strategies                                    |     |

|             | Contingency Plans                                    |     |

| -           | mentation of a Self-Reconfiguring System             |     |

|             | analysis                                             |     |

| 5.1.1       | PowerPC or Custom Logic                              |     |

| 5.1.2       | Memory Storage for the PowerPC Data and Instructions |     |

| 5.1.3       | Memory Storage for the Partial Bit Files             |     |

| 5.1.4       | Tool Integration Issues                              |     |

| 5.1.5       | Internal Reconfiguration Access Port                 |     |

|             | Design                                               |     |

| 5.2.1       | Design Intent                                        |     |

| 5.2.2       | EDK Hardware Considerations                          |     |

| 5.2.3       | EDK Software Considerations                          |     |

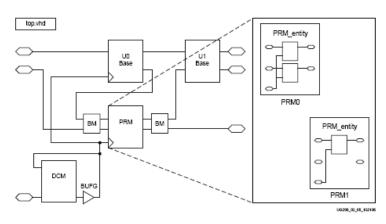

| 5.2.4       | Top-Level                                            |     |

| 5.2.5       | Bus Macros                                           |     |

| 5.2.6       | Module Level                                         |     |

| 5.2.7       | PlanAhead Implementation                             |     |

|             | roduction Flow                                       |     |

| 5.3.1       | Considerations for Further Development in EDK        | 43  |

|   | 5.3.2        | Onboard Partial File Storage               | 43  |

|---|--------------|--------------------------------------------|-----|

|   | 5.4 Tes      | ting and Results                           | 45  |

| 6 | Impleme      | ntation of a TMR-Based Self-Healing System | 50  |

|   |              | ılysis                                     |     |

|   | 6.1.1        | Custom VHDL TMR Implementation vs. TMRTool |     |

|   | 6.1.2        | Partial Regions and Safe Regions           |     |

|   | 6.1.3        | Error Decoding.                            |     |

|   | 6.1.4        | Error Sampling                             |     |

|   | 6.1.5        | Output Enables                             |     |

|   | 6.1.6        | PowerPC Partial Module Reset               |     |

|   | 6.1.7        | DCM Module Placement                       |     |

|   | 6.1.8        | Considerations for Sequential Systems      |     |

|   | 6.1.9        | Expandability of the TMR Design            |     |

|   |              | ign                                        |     |

|   | 6.2.1        | Design Intent                              |     |

|   | 6.2.2        | EDK Software Design.                       |     |

|   | 6.2.3        | EDK Software Design                        |     |

|   | 6.2.4        | Logic Module                               |     |

|   | 6.2.5        | Partial Module                             |     |

|   |              |                                            |     |

|   | 6.2.6        | Safe Module                                |     |

|   | 6.2.7        | Generic Top-Level TMR                      |     |

|   | 6.2.8        | PlanAhead Implementation                   |     |

|   |              | duction Flow                               |     |

| 7 |              | ting and Results                           |     |

| 7 |              | onsiderations                              |     |

|   |              | Macros and Internal Routing                |     |

|   |              | verPC Wrappers                             |     |

|   |              | .P                                         |     |

|   |              | tware Storage                              |     |

|   |              | R Considerations                           |     |

|   |              | e Machine Considerations                   |     |

| 8 |              | on                                         |     |

|   |              |                                            |     |

| A |              | Self-Reconfiguring System                  |     |

|   |              | PC Software                                |     |

|   | A.2: Top-L   | evel – VHDL                                | 103 |

|   |              | figurable Module – LED Switch – VHDL       |     |

|   | A.4: Static  | Module – LED Display – VHDL                | 107 |

|   |              | Module – Clock Converter – VHDL            |     |

|   |              | Constraints File                           |     |

| A | ppendix B: ' | TMR-Based Self-Healing System              | 114 |

|   |              | PC Software                                |     |

|   | B.2: Power   | PC Wrapper – Top-Level Wrapper – VHDL      | 116 |

|   | B.3: Power   | PC Wrapper – User Logic – VHDL             | 123 |

|   | B.4: Power   | PC Wrapper – Clock Converter – VHDL        | 128 |

|   | B.5: Power   | PC System – VHDL                           | 129 |

| B.6: PowerPC System Synthesis Parameters             |     |

|------------------------------------------------------|-----|

| B.7: Top-Level – VHDL                                |     |

| B.8: Reconfigurable Module – Logic and Voters – VHDL |     |

| B.9: Reconfigurable Module – LED Blink – VHDL        |     |

| B.10: Reconfigurable Module – Majority Voter – VHDL  |     |

| B.11: Reconfigurable Module – Minority Voter – VHDL  |     |

| B.12: Static Module – Safe Module – VHDL             |     |

| B.13: User Constraints File                          |     |

| Appendix C: Project Goals                            | 147 |

# Table of Figures

| Figure 2-1 – Typical FPGA                                                                 | 4  |

|-------------------------------------------------------------------------------------------|----|

| Figure 2-2 – Virtex-II Pro / Virtex-II Pro X FPGA Family Members                          | 5  |

| Figure 2-3 – Floor Architecture of Virtex-II Pro                                          | 5  |

| Figure 2-4 – Memec FF1152 Development Kit                                                 | 6  |

| Figure 2-5 – Truth Table and Schematic of 1-Bit Majority Voter                            | 9  |

| Figure 2-6 – Truth Table and Schematic of Minority Voter                                  | 10 |

| Figure 2-7 – Minority Voters with Tri-state Buffers and Wired-OR gate                     | 11 |

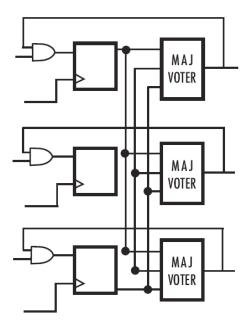

| Figure 2-8 – From Outside to Combinational Logic and Majority Voters                      |    |

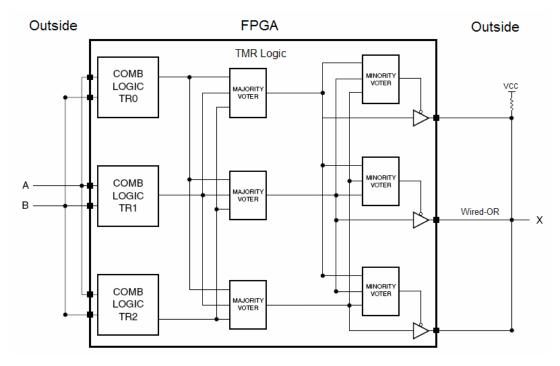

| Figure 2-9 – Full TMR Logic Implementation                                                |    |

| Figure 2-10 – Full Self-Healing System Implementation                                     | 13 |

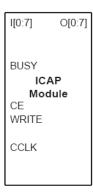

| Figure 5-1– Interface for the ICAP module                                                 |    |

| Figure 5-2 – ICAP Initialization Code                                                     | 32 |

| Figure 5-3 – Main ICAP Programming Function                                               | 34 |

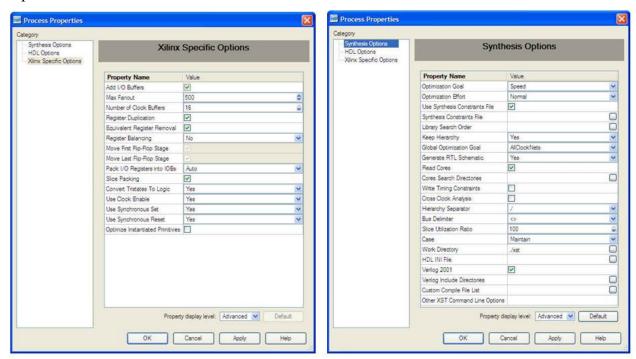

| Figure 5-4 – XST Process Properties                                                       |    |

| Figure 5-5 – Nested Wide Bus Macros                                                       | 37 |

| Figure 5-6 – Matching Port Definitions and Entity Names for a Partial Module              | 38 |

| Figure 5-7 – Bus Macro Placement                                                          |    |

| Figure 5-8 – Partial Bit Files Memory Mapping for the ICAP                                | 45 |

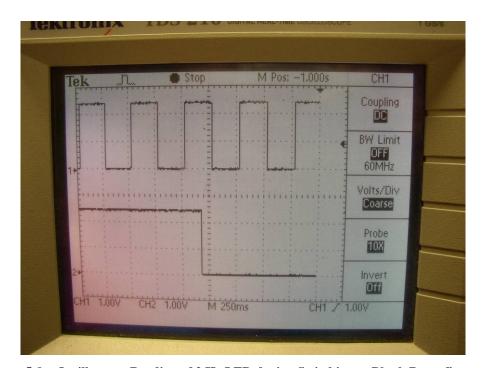

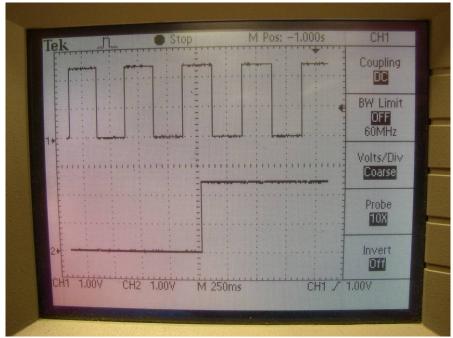

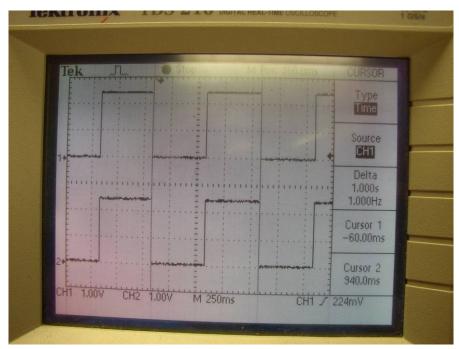

| Figure 5-9 – Oscilloscope Reading of 2 Hz LED during Switching to Blank Reconfiguration   |    |

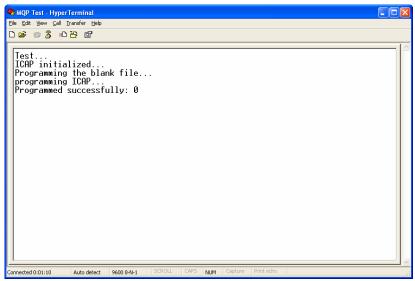

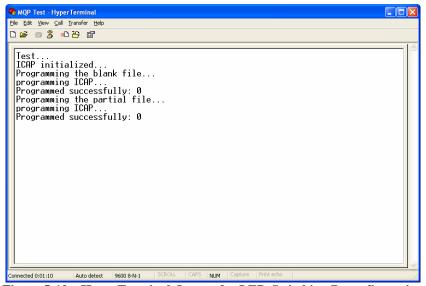

| Figure 5-10 – HyperTerminal Output for Blank Reconfiguration                              | 47 |

| Figure 5-11 – Oscilloscope Reading of 2 Hz LED during Blank to Switching Reconfiguration. | 48 |

| Figure 5-12 – HyperTerminal Output for LED-Switching Reconfiguration                      | 48 |

| Figure 6-1 – Full TMR Logic Implementation                                                | 53 |

| Figure 6-2 – Partial Region Boundaries                                                    |    |

| Figure 6-3 – Voting on Feedback for Redundant State Machines                              | 58 |

| Figure 6-4 – Beginning of main                                                            | 62 |

| Figure 6-5 – The banner procedure                                                         | 63 |

| Figure 6-6 – Infinite loop error checking code                                            | 65 |

| Figure 6-7 – User-Defined Ports for the Custom PowerPC Wrapper                            | 67 |

| Figure 6-8 – Error Decoding Process for the Custom PowerPC Wrapper                        | 68 |

| Figure 6-9 – Reset and Enable Mapping for the Custom PowerPC Wrapper                      | 69 |

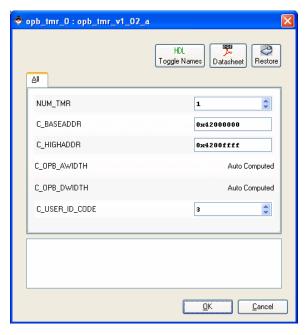

| Figure 6-10 - Configuration Window for the opb_tmr Custom PowerPC Wrapper in EDK          | 70 |

| Figure 6-11 – Feedback Logic for the Blinking LED Module                                  | 71 |

| Figure 6-12 – Final Voter Output for the Partial Module                                   | 72 |

| Figure 6-13 – Generic Majority and Minority Voter Instantiation in the Partial Module     | 73 |

| Figure 6-14 – Input Enables for the Partial Module                                        | 73 |

| Figure 6-15 – Safe Region VHDL Code                                                       |    |

| Figure 6-16 – Instantiation of the Input Bus Macros                                       | 76 |

| Figure 6-17 – Instantiation of the Voter Input Bus Macros for Partial Module 0            | 76 |

| Figure 6-18 – Instantiation of the Logic and Voter Output Bus Macros for Partial Module 0 | 77 |

| Figure 6-19 – Instantiation of the Enable Bus Macro for Partial Module 0                  | 78 |

| Figure 6-20 – Concatenation of the Logic and Minority Voter Signals for the PowerPC       | 78 |

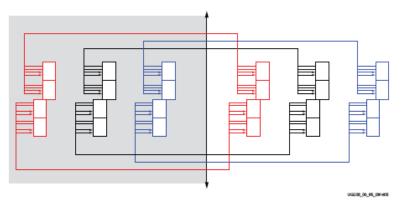

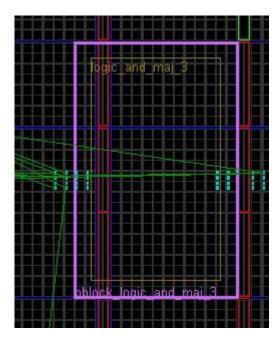

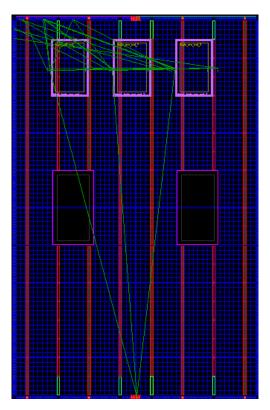

| Figure 6-21 – PlanAhead Floorplan for a Self-Healing System                               |    |

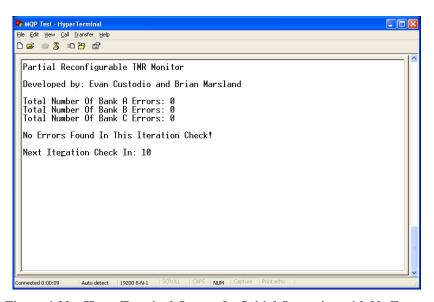

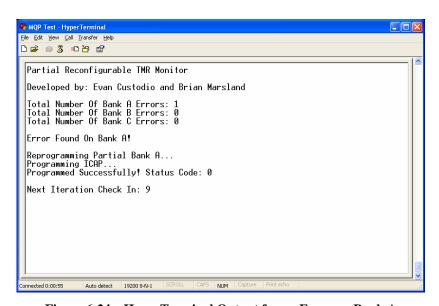

| Figure 6-22 – HyperTerminal Output for Initial Operation with No Errors               | . 85 |

|---------------------------------------------------------------------------------------|------|

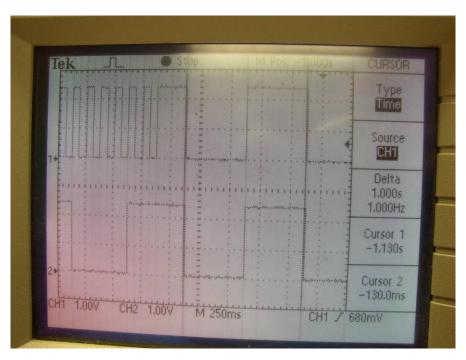

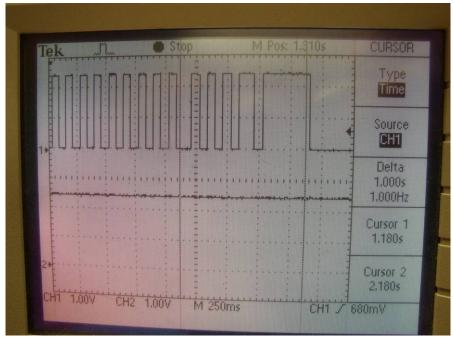

| Figure 6-23 – Oscilloscope Reading of Synchronized 1 Hz Logic and Final Voter Signals | . 86 |

| Figure 6-24 – HyperTerminal Output for an Error on Bank A                             | . 87 |

| Figure 6-25 – Oscilloscope Reading of One Module in Error with Valid Final Output     | . 88 |

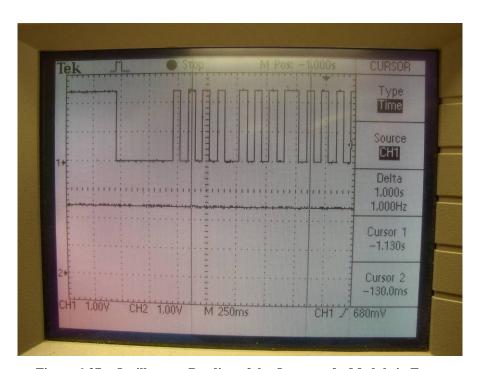

| Figure 6-26 – Oscilloscope Reading of a Reconfigured Module being Resynchronized      | . 88 |

| Figure 6-27 – Oscilloscope Reading of the Outputs of a Module in Error                | . 89 |

| Figure 6-28 – Oscilloscope Reading of the Outputs of a Module during Reconfiguration  | . 90 |

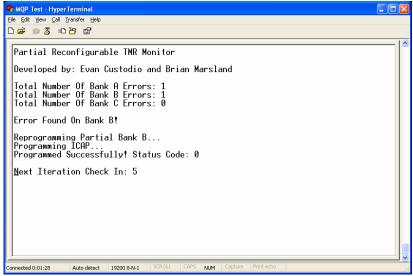

| Figure 6-29 – HyperTerminal Output for an Error on Bank B                             | . 90 |

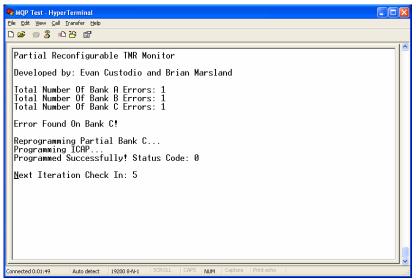

| Figure 6-30 – HyperTerminal Output for an Error on Bank C                             | . 91 |

### 1 Introduction

Mission-critical digital systems are often implemented on Field Programmable Gate Arrays (FPGAs), which allow for easy reprogramming of the hardware. FPGAs are especially desirable in these applications due to their cost-effectiveness for relatively small quantity productions and the ease in which they can be updated. The reprogrammable nature of FPGAs presents one of its strongest advantages as well as one of its most significant limitations as compared to an Application Specific Integrated Circuit (ASIC), which is a non-reprogrammable integrated circuit that is customized for a particular use. The upgradeability of an FPGA is especially useful for systems implementing cryptographic algorithms since modifications can be made to the hardware in order to strengthen the module without the need for re-fabricating the entire chip. However, this non-permanent characteristic of FPGAs also causes problems with errors in the system, especially in environment subject to high radiation. Particles may cause portions of the reprogrammable circuitry to change states. FPGAs are therefore more prone to errors in its logic values and in its actual circuitry than a more permanent custom hardware solution such as an ASIC. Thus, in cooperation with General Dynamics C4 Systems, this project implements a proof-of-concept system that is capable of detecting such errors and partially selfreconfiguring these corrupted areas. This "self-healing" system is capable of gracefully recovering from errors while maintaining valid system outputs.

A previous research group at General Dynamics C4 Systems developed a proof-of-concept system implementing partial reconfiguration, which is the capability of reprogramming a portion of an FPGA while the rest of the system remains in operation. A major drawback to their system was that it required an external PC to partially reprogram portions of the FPGA. In order to successfully implement a self-healing system, the first goal of this project is to create a self-reconfigurable system. Such a system would extend the previous term's research with the capability of an FPGA to reprogram itself without the need for any external PC. Once the implementation of a self-reconfiguring system has been realized, the ultimate goal of this project is to expand the design to include support for detecting and reconfiguring modules in error without affecting the output of the system.

A self-healing system as implemented in this project provides the capability of providing extra security for designated modules on an FPGA. These modules are typically mission-critical

modules that must maintain valid outputs for the successful operation of the system as a whole. For instance, modules implementing encryption or decryption algorithms may utilize these additional security features to deter parties from gaining access to confidential information. Because areas of high radiation increase the likeliness of an error occurring on an FPGA, space systems are another potentially useful application of a self-healing design. While no system can perfectly eliminate the possibility of any errors in an FPGA, the additional levels of security implemented by the self-healing system in this project provide a much lower probability of such an error.

# 2 Background Review

Throughout the research and development of a system that is capable of detecting and gracefully recovering from errors in its circuitry, many new technologies and concepts have been encountered. Many of these technologies are not yet common practices in digital logic and FPGA (Field Programmable Gate Array) design, and therefore they require significant background research and consideration.

FPGAs are typically used in designs due to their ease of reprogramming; however, this reprogrammable nature causes FPGAs to be prone to errors. As a result of the non-permanent nature of FPGAs, it is possible that portions of the reprogrammable circuit can erroneously change states during operation. This is especially problematic in environments subject to high levels of radiation. Therefore, to achieve a reliable FPGA design, the system must be capable of detecting errors and reprogramming modules as necessary.

Partial reconfiguration is the capability of reprogramming a portion of an FPGA while the rest of the system remains in operation. The concept of partial reconfiguration is a relatively new and uncommon technology used in FPGA design. In order to create a system that has no down-time while repairing modules in error, partial reconfiguration must be used to reprogram these modules without affecting the rest of the system. Triple Module Redundancy (TMR) is used to replicate modules and compare the outputs, which significantly mitigates the probability of that error appearing at the output. TMR can then be used in conjunction with partial reconfiguration to detect errors in a module and reprogram that module as necessary without affecting the final output of the system. The following sections provide a brief overview of these topics and applications of such a system before detailing the design and implementation specifics in later chapters of this report.

## 2.1 Field Programmable Gate Array

A Field Programmable Gate Array (FPGA) is a user-programmable logic device which can be programmed to interconnect arrays of switches to arrays of logic elements. FPGAs are very useful to developers because of their reprogrammable nature. With an FPGA, companies

have the freedom of modifying hardware designs since the device is reprogrammable. Devices such as Application Specific Integrated Circuits (ASICs) are chips that are built for a certain use and cannot modified after fabrication. Given the FPGA's reprogrammable nature, it is also easier for companies to issue out firmware updates when the need arises. FPGAs were first created in 1985 by a company called Xilinx. Ever since then FPGAs have grown in popularity and many different companies have been using FPGA technology in all type of products [3]. The main drawbacks of FPGAs compared to ASICs are their high per-unit cost, slower performance and high power consumption [20]. However, as better transistor technology is implemented some of these drawbacks are slowly disappearing.

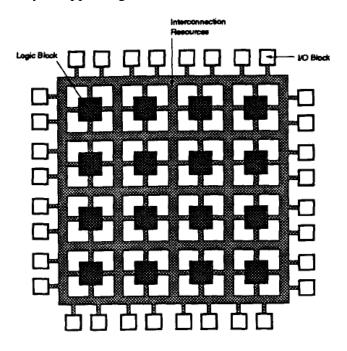

Figure 2-1 – Typical FPGA

Field Programmable Gate Arrays typically work by developing and synthesizing a design on a computer. That design then has all the details on how to route logic gates on the FPGA to allow the creation of the circuit defined in the design. Figure 2-1 illustrates the high-level make up of a typical FPGA.

From Figure 2-1 you can observe that an FPGA contains an entire array of logic blocks. These logic blocks can be as simple as transistors, NAND or XOR gates, or as complex as multiplexers or small microprocessors. The logic blocks are surrounded by programmable interconnections and switches which connect these logic blocks to I/O blocks [14].

### 2.1.1 The Xilinx Virtex-II Pro XC2VP30

The FPGA which is used in this project is the Xilinx Virtex-II Pro XCVP30. The XC2VP30 has some interesting features to note. Firstly, in comparison to its entire family, the XC2VP30 is a medium-grade FPGA. It has two PowerPC cores, 30,816 logic cells, and 13,696 slices. Figure 2-2 below shows how the XC2VP30 compares to the rest of the members in the Virtex-II Pro family line [16].

|                       | RocketIO                    | PowerPC             |                               | CLB (1 = 4 slices =<br>max 128 bits) |                       | 18 X 18 Bit          | Block SelectRAM+ |                       |      | Maximum          |

|-----------------------|-----------------------------|---------------------|-------------------------------|--------------------------------------|-----------------------|----------------------|------------------|-----------------------|------|------------------|

| Device <sup>(1)</sup> | Transceiver<br>Blocks       | Processor<br>Blocks | Logic<br>Cells <sup>(2)</sup> | Slices                               | Max Distr<br>RAM (Kb) | Multiplier<br>Blocks | 18 Kb<br>Blocks  | Max Block<br>RAM (Kb) | DCMs | User<br>I/O Pads |

| XC2VP2                | 4                           | 0                   | 3,168                         | 1,408                                | 44                    | 12                   | 12               | 216                   | 4    | 204              |

| XC2VP4                | 4                           | 1                   | 6,768                         | 3,008                                | 94                    | 28                   | 28               | 504                   | 4    | 348              |

| XC2VP7                | 8                           | 1                   | 11,088                        | 4,928                                | 154                   | 44                   | 44               | 792                   | 4    | 396              |

| XC2VP20               | 8                           | 2                   | 20,880                        | 9,280                                | 290                   | 88                   | 88               | 1,584                 | 8    | 564              |

| XC2VPX20              | 8(4)                        | 1                   | 22,032                        | 9,792                                | 306                   | 88                   | 88               | 1,584                 | 8    | 552              |

| XC2VP30               | 8                           | 2                   | 30,816                        | 13,696                               | 428                   | 136                  | 136              | 2,448                 | 8    | 644              |

| XC2VP40               | 0 <sup>(3)</sup> , 8, or 12 | 2                   | 43,632                        | 19,392                               | 606                   | 192                  | 192              | 3,456                 | 8    | 804              |

| XC2VP50               | 0 <sup>(3)</sup> or 16      | 2                   | 53,136                        | 23,616                               | 738                   | 232                  | 232              | 4,176                 | 8    | 852              |

| XC2VP70               | 16 or 20                    | 2                   | 74,448                        | 33,088                               | 1,034                 | 328                  | 328              | 5,904                 | 8    | 996              |

| XC2VPX70              | 20(4)                       | 2                   | 74,448                        | 33,088                               | 1,034                 | 308                  | 308              | 5,544                 | 8    | 992              |

| XC2VP100              | 0 <sup>(3)</sup> or 20      | 2                   | 99,216                        | 44,096                               | 1,378                 | 444                  | 444              | 7,992                 | 12   | 1,164            |

Figure 2-2 – Virtex-II Pro / Virtex-II Pro X FPGA Family Members

Figure 2-3 - Floor Architecture of Virtex-II Pro

Figure 2-3 above shows an image of the floor architecture for the Virtex-II Pro FPGA. In the figure the two PowerPC cores are visible in the middle of the floor area. There are SelectIO-Ultra and DCM (Digital Clock Manager) interfaces on the side and there is BlockRAM placed vertically along the floor area [21].

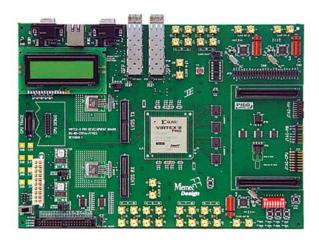

Along with the powerful Virtex-II Pro FPGA this project will use the FPGA on a Memec development board. This development board has plenty of I/O to use. Aside from simple LEDs and buttons, this development board contains 32MB of SDRAM, 2 x 16 character LCD, 10/100 Ethernet PHY, JTAG, CPU debug, CPU JTAG ports, RS-232 and more. Figure 2-4 below is an image of the development board used in this project [1].

Figure 2-4 – Memec FF1152 Development Kit

### 2.1.2 Single Event Upsets and Single Event Transients

One of the major motivations of this project is to combat system critical errors to FPGA designs. There are two main types of errors that are being considered, the Single Event Upset and the Single Event Transient. The Single Event Upset occurs when radiation affects the transistors that are part of the look up table logic of the FPGA. If the lookup table becomes affected by radiation it can change bit values associated with the hardware makeup of the current FPGA design. If radiation does modify a lookup table, this could cause a NOR to be switched to a NAND therefore compromising the entire system [5].

The Single Event Transient is less damaging than the Single Event Upset mainly because it does not affect the hardware makeup of the current FPGA design. The Single Event Transient instead affects current processing of data in the circuit. Radiation can hit areas on the FPGA and cause an incorrect bit value to the input or output of critical modules. Although this does not affect the hardware makeup of the FPGA design, many mission critical designs require high reliability of data processing and in turn these types of errors could just be as dangerous [4].

### 2.2 Partial Reconfiguration

Partial reconfiguration (PR) is the ability for a portion of an FPGA to be reprogrammed while the remainder of the system remains unchanged. A partial bitstream loads only a portion of the design onto the FPGA rather than rewriting the entire design. Partial reconfiguration is especially useful for reprogramming a portion an FPGA during operation without affecting the rest of the system. This practice is called dynamic partial reconfiguration. Static partial reconfiguration refers to reprogramming a portion of the FPGA while the rest of the board is in a reset state [21]. Dynamic reconfiguration is much more useful since it allows device reconfiguration during runtime. Therefore, any future use of the term "partial reconfiguration" in this paper will refer to dynamic partial reconfiguration.

Xilinx supports partial reconfiguration for all of its FPGAs, ranging from the Virtex-4 devices to the low-cost Spartan-3 boards. The two main methods of partial reconfiguration supported by Xilinx are module-based and difference-based. Module-based partial reconfiguration is used to specify portions of the device that can be reconfigured, which are known as reconfigurable modules. This module-based design typically requires floorplanning to specify where all of the reconfigurable modules will be placed on the physical layout of the FPGA. When the device is to be reprogrammed, the entire reconfigurable module is overwritten with the new partial bitstream. Difference-based partial reconfiguration is used to only make small changes in the FPGA design. The generated bitstream only includes differences between designs. Difference-based partial reconfiguration allows for faster reprogramming of the device since only the changes must be rewritten, but it has limited applications as compared to the module-based solution. In this project, only module-based partial reconfiguration will be used [9].

In a system implementing module-based partial reconfiguration, modules that are to be kept in continuous operation without the capability of being partially reprogrammed are referred to as static modules. One or more modules can be designated as the partially reconfigurable module(s), which require additional considerations in the design, synthesis, and implementation stages. Specifically, a modular design flow must be used which will synthesize and create separate bitstreams for each of the reconfigurable modules as well as a total system bitstream including all of the static logic and one implementation of each of the reconfigurable modules.

Partial reconfiguration can be implemented through a JTAG connection to a PC or internally though custom logic or an on-board processor, such as the embedded PowerPC in the Virtex II Pro FPGA. Partially reprogramming the FPGA through internal circuitry, referred to as self-reconfiguration, is a much more useful method of partial reconfiguration since it eliminates the need for an external PC. The partial bitstreams are stored in memory and are written to the Internal Configuration Access Port (ICAP) of the FPGA in order to reconfigure the specified region of the board with the new logic. Self-reconfigurable modules allow for the implementation of a self-healing device, which is a system capable of detecting errors in its own circuitry and reconfiguring the modules as necessary. A self-healing device can detect and gracefully recover from errors while maintaining valid output from the system. This is especially valuable for devices that are operating in the field and contain crucial applications such as circuitry implementing cryptographic algorithms, where errors in such modules could cause access to information that is supposed to be kept confidential.

# 2.3 Triple Module Redundancy

FPGAs allow a hardware engineer tremendous flexibility to implement and revise hardware designs in a very short amount of time. The FPGA's soft-core nature makes it possible to route arrays of logic elements in a certain fashion according to a bit map software description. Unfortunately, as is the problem with many large memory arrays, the FPGA can be affected by external radiation. This radiation can cause corruption with the interconnections between logic elements. This issue has always been a major concern in unknown high-radiation applications (such as space). Comparatively, this radiation is a lesser concern in ASIC designs because most of the connections between logic elements are physically hardwired together, and not connected

by using programmable switches. The radiation is dangerous to the FPGA because the state of these programmable switches in charge of routing can flip as any outside radiation hits it [4]. For instance, if an FPGA was programmed to route two inputs into an OR gate, radiation could hit the programmable switch in charge of this routing and the inputs routed into the OR gate may then be routed into an AND gate. These types of events can be classified as an SEU. Triple Module Redundancy with a majority vote is an ideal method to prevent these SEUs from affecting the FPGA's programming.

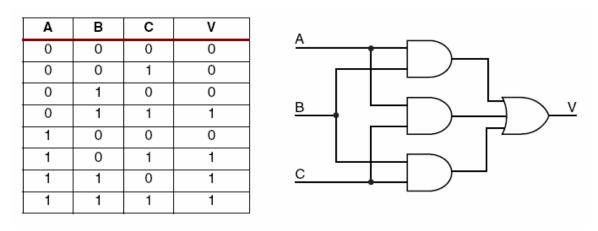

The concept of Triple Module Redundancy (TMR) is based on the idea of implementing the same logic task three times. The three outputs from these redundant modules are then compared in order to locate any possible area corruptions. Ideally the three outputs should be all identical, however if this is not the case then these three outputs are compared using the majority voter. The majority voter takes an input from three individual but redundant modules in parallel. If two or more of these inputs are equal, then the output of the majority voter is input majority. Figure 2-5 below is a schematic and truth table of a 1-bit majority voting circuit. This majority output is decided by the majority voter to be the true output of this redundant logic. The major benefit from this is that if one out of the three modules is not in working condition, the overall functionality of the logic is not compromised.

Figure 2-5 – Truth Table and Schematic of 1-Bit Majority Voter

This method of using TMR with only one majority voter circuit is still flawed, this is because the SEU not only could affect the redundant modules but can also affect the voting circuit itself. To alleviate this issue the majority voting circuit must also be redundant. These redundant majority

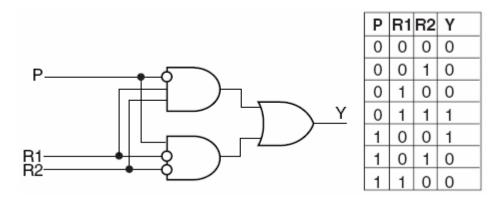

voters must be compared using minority voter circuits. The minority voters also take in three inputs, the primary path and two other redundant paths in question. If the primary path is in the majority with one other redundant path then the output is low. If the primary path is in the minority in comparison with the two other redundant paths then the output is high. Figure 2-6 below is a schematic and truth table of the minority voting circuit.

Figure 2-6 – Truth Table and Schematic of Minority Voter

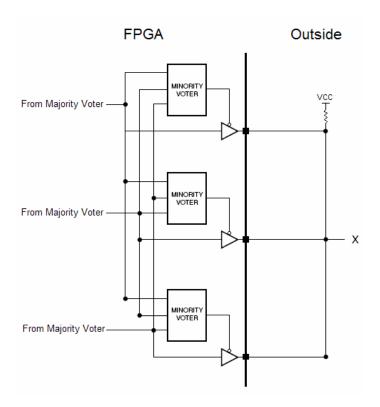

This minority voter output is fed into the control signal of a tri-state buffer with an inverted control input. If the path in question is the minority then the tri-state buffer will be placed into high-impedance. If the path in question is in the majority then its corresponding tri-state buffer will allow the path to follow through to output. These three outputs will connect together outside of the FPGA into a wired-OR fashion. Figure 2-7 shows the minority voters controlling the tri-state buffers which feed outside to the wired-OR gate.

Figure 2-7 – Minority Voters with Tri-state Buffers and Wired-OR gate

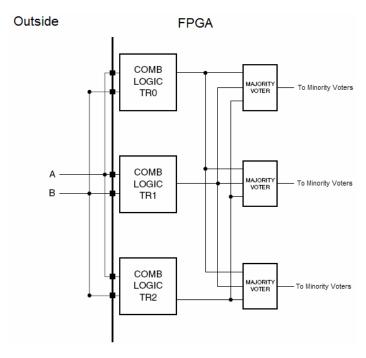

The main reason of implementing the Wired-OR on the outside of the FPGA is because it is the main circuit which combines all TMR outputs. It is the one section which must be hardwired so that it cannot be affected by the SEUs. If the three outputs were connected inside the FPGA, this would still be considered a soft-core wire connection and can be compromised by SEUs. Similarly, the inputs must be duplicated outside of the FPGA in order to guarantee true signal independence. Figure 2-8 below shows the hardwired inputs into the FPGA TMR logic.

Figure 2-8 – From Outside to Combinational Logic and Majority Voters

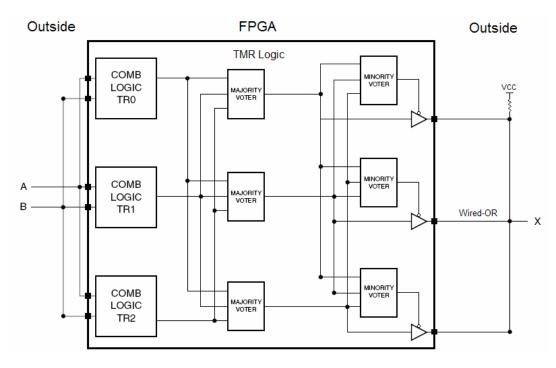

Figure 2-9 – Full TMR Logic Implementation

This full TMR implementation can be shown in Figure 2-9. The full TMR design example illustrates how to implement TMR with only combinational logic. Special

considerations must be taken into account when implementing TMR with simple and complex state machines [4].

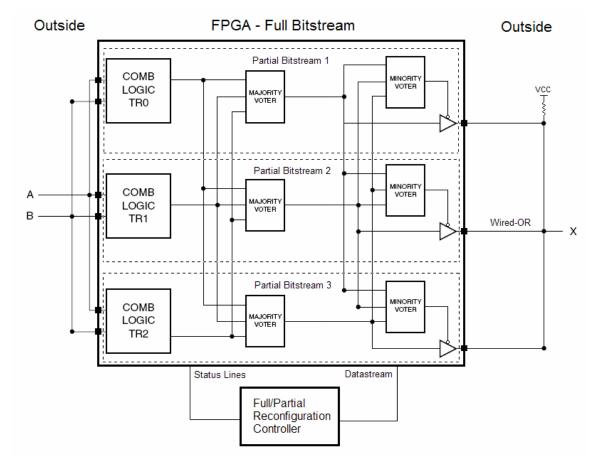

### 2.4 Practical Uses of Self-Healing Systems

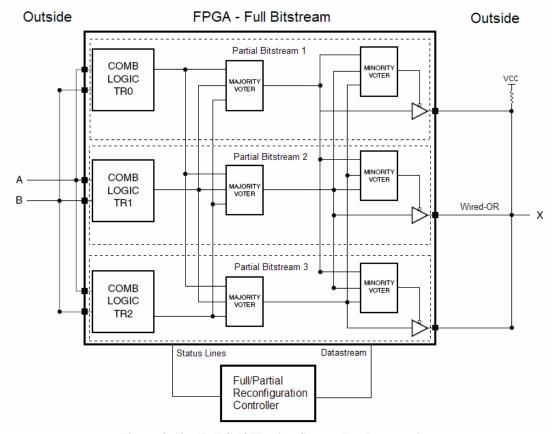

Partial Reconfiguration and Triple Module Redundancy can be used together to create a true Self-Healing system design. In order to do this, the full TMR implementation must be extended to provide additional status outputs to the partial reconfiguration controller. During FPGA operation as data is being processed through the redundant modules, if any of the three modules gets corrupted the overall output is not compromised, also the status signal will be set to communicate to the partial reconfiguration controller in order to configure the module in question. During this time there is no downtime or effect on the overall system while a module is being reconfigured. Figure 2-10 below illustrates the full system diagram of a Self-Healing system.

Figure 2-10 – Full Self-Healing System Implementation

A practical use of this system design would be in cryptography. Implementing a cryptographic algorithm on an FPGA provides exposure to a couple of known attacks in order to break the integrity of the algorithm. Such attacks are referred to as side-channel attacks. One may be capable of corrupting portions of the FPGA in order to analyze its behavior. Analyzing such behavior can give an attacker insight on how to compromise the security. Implementation a Self-Healing system to the cryptographic algorithm can prevent corruption to the FPGA and alleviate the possibilities for this type of attack [12].

Another practical use of this system design would be in any type of high-radiation setting such as space. There are many radiation particles traveling through space, if no protection is applied, these particles can strike your device and possibly cause it to malfunction. A Self-Healing system using Partial Reconfiguration and Triple Module Redundancy will drastically reduce the probability of radiation causing complete system failure and will ensure full system uptime during the healing process.

#### 2.5 Previous Work

Previously completed Major Qualifying Projects at General Dynamics C4 Systems have provided a framework for the research and design to be completed in this project. The project, "Dynamic Partial Reconfiguration of a Field Programmable Gate Array" completed in March 2007, detailed the design flow for a system implementing partial reconfiguration as well as an initial study of potential implementations of self-reconfiguration. "A Self-Healing Circuit Implementing TMR," completed in April of 2006, provided a background on the use of TMR for error detection and correction in FPGAs. This project ultimately combines these two background areas of research into a complete self-healing cryptographic system.

#### 2.6 Tools

Several hardware and software tools are necessary for the completion of this project. These tools include the physical FPGA and its associated development board that allowed for continual reprogramming of test systems as well as many features for data storage and output display. Xilinx has also supplied a suite of tools that are necessary for this project. These Xilinx software tools are used for developing the hardware and software aspects of the system. Although many of these tools have included documentation from Xilinx, their support of partially reconfigurable systems is currently somewhat lacking. Therefore, the integration of these tools into a working tool flow to achieve the goal of a self-healing system required research from numerous sources and some experimentation with the tools.

### 2.6.1 Virtex-II Pro Memec Development Board

The Virtex-II Pro Memec Development board provides a variety of features in order to implement our partial reconfiguration designs. This board contains a Virtex-II Pro FPGA chip from Xilinx which has two PowerPC cores. Out of the many features which this board provides, this project just utilizes the FPGA, a PowerPC core, onboard memory storage and the inputs/outputs provided by RS-232, LEDs, and dip-switches.

#### 2.6.2 Xilinx EDK 8.2.02

Xilinx EDK is a software development kit used to utilize the functionality of the onboard PowerPC cores of the Virtex-II Pro FPGA chip. The EDK provides us with IP Cores to bridge functionality of hardware designs on the FPGA with software designs on the PowerPC. This is an attractive feature as this project will implement VHDL designs on the FPGA while being able to partially reprogram those designs using the PowerPC. Most of the software developed for this project will be created using the Xilinx EDK interface. After a successful software build, the EDK can synthesize the correct VHDL wrappers to instantiate the PowerPC core and can inject the PowerPC instructions into a blockram on the FPGA for the PowerPC to read and process.

#### 2.6.3 Xilinx ISE 8.2i

Xilinx ISE is a popular FPGA development tool used widely in industry and in educational institutions. This tool allows for complete FPGA development. ISE can read in VHDL/Verilog/Schematic modules created for a project design and synthesize them into logic elements to be placed on an FPGA. ISE can automatically interpret your HDL syntax, synthesize your description, place and route the logic elements and then provide a software BIT file description to connect these logic elements together to create the circuit described in the HDL. All these tool flow steps require their own respective application program to perform the function. ISE calls these programs automatically in a pleasant GUI so that the user can create FPGA designs in seconds.

#### 2.6.4 Xilinx PlanAhead 8.2.7

Xilinx PlanAhead is a floorplanning tool provided by Xilinx to allow developers flexibility on how there synthesis designs should be placed on the FPGA floorplan. This tool is useful in ASIC designs where locations of logic elements are an important factor to the performance of the application. For the scope of this project, PlanAhead has partial reconfiguration options which make it a required tool in the partial reconfiguration tool flow.

# 3 Project Goals

Before the start of the project certain top-level and technical goals were laid out. The top-level goals must satisfy both General Dynamics C4 Systems and WPI. The work done must provide General Dynamics with enough research and documentation so that the project could be re-created if the need arises. Also, the work must provide the project group enough educational benefit to merit a grade as a Major Qualifying Project for WPI. Once the top-level goals were set, the technical goals were decided. These goals are very specific to the type of research that needed to be done.

### 3.1 Top-level Goals

The project group wanted to give General Dynamics C4 Systems a fully implementable self-healing design using partial reconfiguration and triple module redundancy. It was also decided that this design should have the ability to be re-created with helpful step-by-step documentation. The project group expected that General Dynamics would use this design for future self-healing crypto applications in high radiation environments. In order to satisfy WPI's goals the project group would need to gain lots of experience with VHDL, Xilinx's tool environment and development on the PowerPC core in order to research and write a comprehensive academic report.

#### 3.2 Technical Goals

Our main overall technical goal was to implement a cryptographic circuit which includes triple module redundancy for error checking and has the capability of healing itself if an error were to be detected. This main top-level technical goal is split into three important milestones. First goal is to design a self-reconfiguring system, the second goal after is to design a self-healing system and the last goal is to design a more complex VHDL module for the self-healing system. Each of these goals and their sub-goals will be discussed in more detail.

Designing a self-reconfiguring system required specific technical goals to be met. First was to re-implement the previous project group's design of partial reconfiguration. Next was to become more familiar with the PowerPC and Xilinx Platform Studio. After that, achieving communication with the ICAP port must be obtained. This can either be done using the ICAP IP core of the PowerPC or designing a custom VHDL solution which can interface with the port. After communication with the ICAP port is a success, the project group must implement a simple ICAP design into a partially reconfigurable environment. Once these components are integrated, the next goal would be to load a partial bitstream from flash memory through the ICAP port to the partial area of the FPGA on a button push.

Once the self-reconfiguring system has been design, the next goal would be to design a self-healing system. To do this the project group must implement TMR functionality to detect errors in the redundant modules. This can be done one of two ways, either by using custom VHDL to replicate modules and create voting circuitry or use the Xilinx XTMR tool to create the TMR system. In either case, once this goal is completed the next goal is to modify the ICAP design to load a partial bitstream to a redundant module when an error in the module is detected.

Once the self-healing system has been designed and tested, the next goal is to design a more complex VHDL module to be used in this self-healing system. This goal can be achieved by either using a supplied AES implementation that can fit within the size constraints or by creating an alternate custom algorithm. After all these goals have been met, the project is completed and ready for testing and documentation. For a list of all the technical goals and their estimated difficulty, please refer to Appendix C.

# 4 Methodology

In this section the methodology that the project group used in completing this project will be discussed. It is important to note that before starting a project, members of the group must have an overall plan on how to engage problems at hand. Not having a pre-defined plan would have cost the group many wasted hours of uncompleted work. This project group could not afford losing any time because of the nature a seven-week Major Qualifying Project. In the following sections the importance of tool flow, analysis strategies, design strategies and contingency plans will be discussed.

#### 4.1 Tool Flow

Tool flow is a very important process to be documented. One of the first goals which this project team had to accomplish was to re-create the partial reconfiguration implementation which the previous project group had achieved. This goal was a complete success because of the tool flow which the previous project group had supplied. It is important to note that this project is not solely research; it is also a step-by-step guide on how to re-create the proof-of-concept of the research. Such a step-by-step guide could not have been possible without a well-documented tool flow.

For each of the goals accomplished, the project group made sure that at the end of the day each step of the successful tool flow was well-documented. This was done for a couple of reasons, since the project group is dealing with complex designs, these tool flows become very lengthy. If the project group did not document the tool flow as goals were accomplished, it would have been difficult to recall all the small mundane steps taken to achieve the goal. The second reason is that if the project group did not document tool flow, and could not recall certain steps in the tool flow, then it would have cost the group valuable time and effort in re-creating designs.

Two tool flows have been created for this project, one for a self-reconfiguring system and one for a self-healing system. The project group hopes that this tool flow will be used by General Dynamics and any other MQP group continuing research in this area.

# 4.2 Analysis Strategies

When analyzing problems to achieve a goal, the project team must extensively research these problems. To do this, the project team took use of parallel research. Since the project group had only two members, the resources of both members had to be utilized to their full extent. In a given day, if the group had three different things to analyze, one group member would research one of the topics while the other group member would research a different topic. In the end a group meeting would take place to discuss the findings and consider them for implementation of the design. Some topics of analysis would require much more extensive research. For these topics, both group members would research the topic in parallel in order to not follow the same train of thought and to arrive at the solution faster than usual.

### 4.3 Design Strategies

After analysis was completed on a certain project goal, the project group would start designing. Given that most of the design work was done in either VHDL or C, the group took use of the software engineering concept of pair programming. Different from parallel research, pair programming utilizes the resources of both project members at the same time on one design topic. In pair programming, one of the project members is the main programmer and the second project member reviews all the code written by the first member while it is being written. This strategy was a very efficient use of resources. It combined the intelligence of both project members during the design stage in order to quickly build the designs needed. If the main programmer was stuck on a problem at hand, both members would suggest and build upon each others' ideas to come to a solution. Also, pair programming reduced time on debugging, while the main programmer was writing code, the other project member could review the code as its being written and point out any possible errors that were made.

# 4.4 Contingency Plans

In order to prevent complete dead-lock of the project, the project group made sure that contingency plans were set in place. Since this project required a significant amount of research in order to discover tool flow, there was no guarantee that at any point that a certain plan of action would work. If the project group were to explore a path of research that did not lead to a solution in a reasonable amount of time, then the project would be placed in complete dead-lock. Pre-defined contingency plans solved the problem of project failure. It is important that the project is not placed on a completely sequential goal-path. The project group made sure that for certain goals which may lead to problems, that there are two different paths to come to the same solution. This way if one path is not leading to the solution, the project group can switch paths seamlessly with very little time wasted. Fortunately, this project group did not face any critical research dead-lock with any of the technical goals placed. Good analysis and design strategies used by the project team ensured that all goals were met in order to complete the project.

# 5 Implementation of a Self-Reconfiguring System

A system implementing dynamic partial reconfiguration over the JTAG connection to a PC was developed by the previous project group. However, the use of partial reconfiguration is not truly valuable unless the FPGA is capable of reprogramming itself independently of an external PC and ultimately without any necessary human interaction. A design that implements self-reconfiguration is a significant milestone for achieving a self-healing system that can detect errors in its circuitry and reprogram the modules as necessary to fix these errors.

### 5.1 Analysis

The implementation of a self-reconfiguring system requires careful consideration of several significant design choices. The study of self-reconfiguring systems is still in its infancy, so much of the documentation is fragmented, incomplete, or incorrect. Systems implementing partial self-reconfiguration are still uncommon in most FPGA applications due to the relatively large overhead required for the initial analysis phase to find a working tool flow. Xilinx has recently been attempting to make partially reconfigurable systems easier to implement. Xilinx has added more documentation to their website and has produced a more user-friendly floorplanning tool used for partial reconfiguration, but much of this information is currently limited to an "Early Access" area that requires approval for access. Although a more standardized and user-friendly tool flow for partial self-reconfiguration may be available soon, a large amount of research and trial-and-error had to be used in order to attain a self-reconfigurable system using the currently available tools and documentation.

## 5.1.1 PowerPC or Custom Logic

A self-reconfiguring system on a Xilinx Virtex FPGA is implemented by making use of the Internal Configuration Access Port (ICAP). A partial bitstream is written to the ICAP, which then reconfigures the specified portions of the FPGA with the new logic. Communication with the ICAP can be implemented through either the embedded PowerPC or through a custom VHDL logic design.

The Virtex-II Pro FPGAs used in this project include two embedded PowerPCs. One significant advantage to using the PowerPC is that Xilinx has provided an IP core that interfaces to the ICAP. Using this interface, the PowerPC can communicate with the ICAP through simple C method calls, with most of the low-level interface design being hidden to the user. In fact, once the bitstream is loaded into memory, only one single method must be called to successfully reprogram a reconfigurable module on the device. Conversely, a custom logic design would require a manual implementation of the low-level interface to the ICAP, including any necessary timing considerations. Also, the PowerPC provides additional IP cores that enable easy interfacing with the different types of memory in the system as well as the I/O modules of the test board. The use of any of these interfaces would require VHDL code if the PowerPC were not being used. The RS232 port can act as the standard input and output of the C programs, which allows for status messages to be sent over the RS232 cable and displayed on HyperTerminal running on the Windows XP PC. The ability to print status messages during the debugging stage of the design was very useful to quickly determine exactly where an error occurred.

Although the IP cores provided by Xilinx are very useful to hide the low-level implementation of the peripherals, they do make use of more board resources than may be necessary for this application. The PowerPC itself is a hardware module that cannot be reconfigured on the FPGA, but the wrapper files associated with the IP cores utilize many additional board resources. A custom logic interface would be less resource intensive since only the required logic would be included in the design. The IP cores include functionality for some peripherals that are never used in this project. Also, once the system is implemented with TMR in the next portion of the project, the PowerPC introduces some additional issues. The PowerPC itself does not have to be replicated since it is actually part of the hardware and not part of the reconfigurable logic; however, the surrounding VHDL wrapper files are susceptible to errors caused by SEUs. It is difficult to include these wrapper files in the replicated portion of the design, so they are not protected from SEUs.

The PowerPC was chosen as the method for interfacing with the ICAP in this design. Although it does use more resources than necessary, the custom VHDL modules implemented in this system are relatively small and are not limited by board resources. Additionally, the time it saved by hiding the low-level details of the ICAP and other peripherals allowed for other areas of the project to be reached that may not have been otherwise possible.

### 5.1.2 Memory Storage for the PowerPC Data and Instructions

When using the Xilinx EDK tool to implement PowerPC functionality on the Virtex-II Pro FPGA, the Block RAMs internal to the FPGA are automatically initialized with the proper program data and instruction memory when the bitstream is generated and written to the board. The block memory contents are specified in a Block Memory Map (BMM) file, which contains a syntactic description of how individual Block RAMs (BRAMs) create a contiguous logical data space. During the Place and Route (PAR) and bitstream generation portions of the design implementation, the BMM template file is updated to specify the configuration of the BRAMs. However, when utilizing the self-reconfiguration design flow, specifically in the PlanAhead software, this process does not initialize the BMM files correctly. The solution to this problem requires updating the BMM template file automatically generated by EDK with the updated design hierarchy as well as modifying the scripts generated by PlanAhead to include the BMM file. The exact changes will be specified in the Production Flow of the project report. Once the updated BMM file has been generated, it must be imported back into the EDK project directory along with the new full bitstream. EDK will properly read the updated bitstream and BMM files, and it will automatically initialize the Block RAM modules when the bitstream is uploaded to the FPGA. This allows for easy software reprogramming since the data and memory initialization will be automatically loaded

An alternative method for storing program data and instruction memory is to use the Static RAM (SRAM) modules on the Memec test board external to the FPGA. These SRAM modules are much larger than the Block RAM internal to the FPGA. Although this design does not use a significant portion of data or instruction memory, future designs may be limited by the size of the Block RAM. Also, since the Block RAM modules are part of the FPGA, they are susceptible to SEUs, which may be problem in a TMR design. Since the SRAM modules are external to the FPGA, they are not as vulnerable to these problems. However, because they are not part of the FPGA, they cannot be programmed directly through the JTAG interface. Instead,

data must be written to the FPGA through the JTAG interface and then transferred to the external SRAM modules. This can be done through the "Program Flash Memory" menu option in EDK. Unfortunately, several errors were encountered when attempting to use this method, and the results are inconsistent between different EDK projects. Each time a program is loaded to the board, the SRAM must be configured separately, unlike the Block RAM modules which are configured automatically in the bitstream.

The self-reconfiguring system makes use of the Block RAM modules internal to the FPGA in this design. Although the Block RAM modules are smaller and more error-prone than the SRAM modules, they are easier to use in EDK once the design has been implemented and the final bitstream and BMM files have been created.

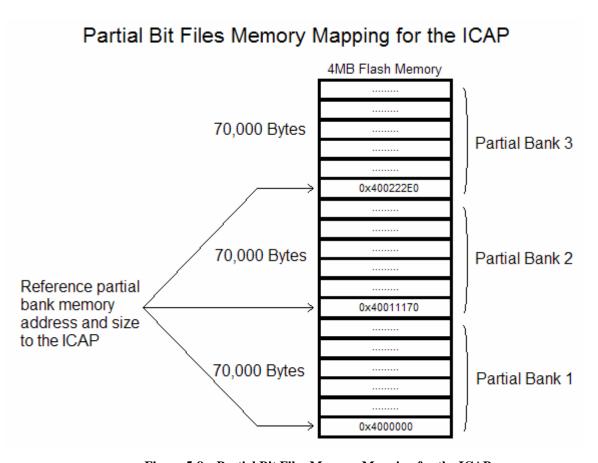

### 5.1.3 Memory Storage for the Partial Bit Files

Similar to the previous design consideration concerning where program code should be stored in memory, a separate decision must be made concerning the storage of the partial bit files in the self-reconfigurable system. Partial bit files are typically equal in size or larger than program code in the simple applications implemented in this project. The bit files for relatively simple modules have generally ranged from 50KB to 75KB in size, and larger, more complicated modules will have larger partial bit file sizes. The program code is typically around 60KB in size, but will likely not significantly increase in size as much as the partial bit files. The code for reprogramming the ICAP should remain relatively consistent regardless of the size of the bit files. Also, when configuring the system using the start-up wizard in EDK, 128KB of Block RAM can be reserved for program code while only 64KB can be reserved for program data. Since multiple partial bit files will be stored in memory consecutively, a larger memory space is necessary for storing the bitstreams than was necessary for storing the application code.

The 4MB Flash Memory module was chosen to store the partial bit files. This memory module is external to the FPGA and is part of the Memory test board. Unfortunately, the use of the external Flash Memory did complicate the tool flow. Some projects created in EDK were unable to properly write data to the Flash Memory while other projects did not cause any problems. Another issue that was encountered was that partial bit files are binary files, which would often cause the flash memory programming tool to freeze without any indication of an

error. In these cases, though, an ASCII file could be programmed to the Flash Memory; however, when reading the file back, only the first 16KB of the file was programmed due to the 16KB sector size of the Flash Memory module. An ASCII file would have to be reverted to binary data in the Flash Memory, so this solution was not desirable even if the sector size problem could be alleviated.

The initial solution to this problem involved using the WinHex software hex editor to convert the binary files into a C array [17]. This array was copied into the program code as a global variable so it would be stored in a Block RAM module. The PowerPC would then use a simple loop to program each byte in the array to consecutive memory locations. Since the Flash Memory is non-volatile, this process of creating C-style arrays and programming them to memory only had to occur once for each partial bit file until a new design was to be loaded to the board. This method of writing the partial bit files to memory allowed for continued development of the self-reconfigurable system, specifically for communication with the ICAP. An initial complete self-reconfigurable system was implemented using this bit file storage method. Since the array must be temporarily stored in Block RAM, though, it is subject to the same size constraints as previously discussed. This method does not scale well to larger bit files, since those may have to be divided into smaller file, and is therefore not an ideal method of programming partial bit files to Flash Memory.

A complete sample EDK project was provided online for the specific Memec FF1152-6 Virtex-II Pro Rev. 3 Development Board with the additional P160 Communications Module 2 [1]. This project is supplied by the vendor for the exact revision of the board in use for this project. Once this project was loaded into EDK, the "Program Flash Memory" tool in EDK allowed for successful programming of binary partial bit files to the memory. This also alleviated the problem of the 16KB sector size that was previously encountered. It has not yet been determined what features of this supplied project allow for the successful programming of Flash Memory that cannot be completed in other EDK projects. It is possible that the address space set in previous projects was incorrect, or an additional module or configuration file is provided in this project. Determining the exact cause of this error is not a forefront issue in the scope of the MQP, so this EDK project has been used to program the non-volatile Flash Memory with the partial bit files while other EDK projects have been used to include custom hardware and software necessary for self-reconfiguration.

One final issue faced while writing the partial bit files to the Flash Memory is that when writing a file to memory at a specified offset, the entire memory module is cleared before writing the new file. Therefore, multiple bit files cannot simply be programmed separately at different offsets. Instead, the three files must be concatenated into a single file using a hex editor prior to programming. Then, this complete file can be programmed to the Flash Memory.

### 5.1.4 Tool Integration Issues

The previous term's Major Qualifying Project, "Dynamic Partial Reconfiguration of a Field Programmable Gate Array," detailed a tool flow to achieve partial reconfiguration using the JTAG interface. The partial reconfiguration tool flow primarily makes use of Xilinx ISE for designing and synthesizing VHDL modules as well as the PlanAhead software for placing and routing the partially reconfigurable design. The implementation of a self-reconfigurable system using a PowerPC requires the additional Xilinx Platform Studio (XPS) and Embedded Development Kit (EDK) tool to be included in the tool flow. The prior term's team also performed some initial research and testing to include EDK into the tool flow to create a selfreconfigurable system, but they were unable to communicate with the PowerPC in their design. A Xilinx document on the "Early Access" partial reconfiguration website details the integration of EDK into the tool flow [7], which is the document that the previous term's group followed. This method involves modifying VHDL files created by EDK to create the necessary top-level module, which includes the static PowerPC module and any other static or reconfigurable modules. Last term's group encountered several problems when attempting to implement this tool flow. One major problem was that EDK would often overwrite files that they modified, specifically the top-level VHDL file and the synthesis parameters file [10]. They also were unable to make the processor boot or gain access to any of the peripherals. They hypothesized that the PlanAhead software broke the I/O connections to the microprocessor hardware [10]. Due to these issues, an alternative tool flow approach was explored in this project.

Several possible tool flows were explored before finding one that was successful. In order to simplify the process, an incremental design approach was used where each step only added a limited amount of additional functionality to the design. First, a simple design using only EDK was used. Next, this design was then incorporated into a design with other static

VHDL modules. A system was then designed that included both the PowerPC along with reconfigurable modules, but the PowerPC did not control the reconfiguration. Finally, the self-reconfigurable circuit would be implemented where the PowerPC controls the reconfiguration of the modules. This incremental design approach allowed for easier debugging since it was easier to isolate exactly what caused an error rather than attempting to create the complete self-reconfigurable system in one step.

Once a project was built using only EDK, the next step was to incorporate this project with other static VHDL modules, without any communication between these modules and the PowerPC. Initially, netlist files generated by EDK were imported into PlanAhead along with several ISE netlists. However, since there was no top-level file incorporating both modules, this design did not work. Next, the research tem attempted to export the project from EDK to Xilinx ISE. This would create a folder of the necessary VHDL, synthesis, BMM, and other related files necessary for ISE to synthesize the design. Although this method may have worked, Xilinx has deprecated this method and prefers that the .xmp EDK project file be added to the ISE project instead. This is a much better method since changes in the EDK project will automatically be changed in the ISE project rather than having to export and import a new folder of files. Once the XPS project file has been added to the ISE project, a top-level VHDL file must be created that incorporates any static logic modules with the XPS system component. The ports for the XPS system component are found in the "system\_stub.vhd" file located in the "hdl" folder of the xps project. Component instantiation and port-mapping are performed as with any other VHDL component, and the necessary top-level I/O and user constraints file are likewise modified. Once this has been completed, the complete system is synthesized in ISE as normal, and the resulting netlists are imported into PlanAhead for placing and routing. The remainder of the flow is unchanged, and the system works as expected.

The next step of the incremental design process was to incorporate the reconfigurable modules, although they would not be reprogrammed by the PowerPC. Although the synthesis and implementation of this design did not cause any problems, when programming this system to the board, the PowerPC did not produce its expected outputs. This was because the BMM file was not included in the synthesis, and thus the Block RAM modules for the program instruction and data were not initialized correctly. Eventually, a script file created by PlanAhead was modified to include the BMM file generated by XPS. Unfortunately, this created an error in

synthesis. The BMM file had to be updated to include the additional top-level hierarchy caused by importing the design into ISE. Once this was updated, the synthesis ran without any errors. The system was programmed to the board and ran as expected. In order to further modify the software, the full bit file and the updated BMM file generated by PlanAhead had to be imported back into the EDK project directory. When downloading the bitstream to the board in EDK, the full bit file generated by PlanAhead will be programmed, and the instruction and data will be properly initialized in the Block RAM modules.

The final step of the incremental design process was to use the PowerPC module to reprogram the partial bitstreams through the ICAP. The EDK project had to be re-synthesized with the opb\_hwicap IP core included in the design. Once this synthesis finished, the remainder of the tool flow was unchanged from the previously described incremental version of the design. Thus, the self-reconfigurable system was properly implemented. The exact tool flow to achieve this result will be detailed in the "Production Flow" Section of this report.

### 5.1.5 Internal Reconfiguration Access Port

The Internal Reconfiguration Access Port (ICAP) module is used to perform partial self-reconfiguration on Virtex-II and Virtex-II Pro FPGAs [8]. The ICAP module is not intended for full device configuration, but only for partial self-reconfiguration. Configuration data can be read from or written to the ICAP. The interface for the ICAP module is show in Figure 5-1 below. The ICAP uses byte-width input and output ports, which allows for faster reconfiguration than a serial interface. The maximum frequency at which the ICAP module can be clocked without using the BUSY signal is 66MHz [2].

Figure 5-1- Interface for the ICAP module

The low-level details of the interface to the ICAP module are hidden by the EDK OPB\_HwIcap module provided by Xilinx. This module includes the necessary VHDL wrapper files for interfacing the PowerPC to the ICAP as well as the C software libraries that provide the methods for the ICAP functionality. The software library includes functions that allow for initializing the ICAP, reading configuration data from the ICAP, writing a frame to the ICAP, and writing a partial bitstream to the ICAP. Since the partial bitstreams will be stored in memory for this application, the most useful function is for writing a complete partial bitstream to the ICAP in which a pointer to the start address in memory and the size of the bitstream must be passed as parameters. The software libraries and VHDL wrapper files will convert this data into an appropriate format and write it to the ICAP module.

## 5.2 Design

The design of a working self-reconfiguring system is a crucial stage in the development of a complete self-healing system. A true self-healing system must be able to fix errors in its circuitry without any external interaction. This reprogramming will be handled by one of the PowerPC cores on the Virtex-II FPGA. Therefore, this design will make use of both hardware and software elements. All of the code and other necessary files for the implementation of this system can be found in Appendix A. A step-by-step production flow to create a self-reconfiguring system is given in section 5.3 of this report.

## 5.2.1 Design Intent

The purpose of this initial self-reconfiguring design is to determine and validate the functionality of the ICAP module for partially reprogramming portions of an FPGA. The prior General Dynamics C4 Systems MQP project team was able to perform partial reconfiguration through the JTAG connection with an external PC, but they were never able to successfully reprogram portions of the FPGA using the ICAP. In order to achieve the final goal of a self-

healing system that can detect and gracefully recover from errors, it is necessary for the FPGA to be able to reprogram itself without any external PC or human interaction.

Thus, this self-reconfiguring design is a relatively simple proof-of-concept circuit that demonstrates the use of the ICAP module and the production flow necessary to achieve this system. The partial module in this system is one that uses four switches to control the corresponding 4 LEDs on the bottom row of the FPGA development board. A static module includes the PowerPC system generated through the Xilinx EDK tool and a simple module that controls the other four LEDs on the FPGA development board. During the synthesis and implementation flow, a complete bit file will be generated with the static logic and the LED-switching partial module. Also, the partial bit files for the LED-switching module and the blank module will also be generated. These two partial modules will be written to memory. When the first button on the development board is pressed, the PowerPC will detect the input and will program the blank partial module to the ICAP. When the second button is pressed, the LED-switching partial module will be programmed. Thus, once the bitstreams are stored in memory, no external PC is required for reprogramming portions of the FPGA.

#### **5.2.2 EDK Hardware Considerations**

The Xilinx EDK tool is the first place to start when considering the PowerPC design portion of this project. In EDK, it is important to start off with a new project that conforms to the settings of the project board. Interfaces like RS-232, and SDRAM should be added for proper operation of the PowerPC core. Once your workspace has been created, basic demonstration source code should have been created in order to test the interfaces which were added to the project. One extra interface which must be included for self-reconfiguration is the hardware ICAP wrapper. This peripheral can be added by going into the IP Catalog in EDK and manually added it to the design. Once the IP core has been added, connect the peripheral to the OPB bus and set a 64k address range for the device to operate on. The address range recommended in this tool flow is 0x40200000 to 0x4020FFFF.

#### 5.2.3 EDK Software Considerations