# **Sparse Matrix Multiplication on a Field-Programmable Gate Array**

A Major Qualifying Project Report submitted to the Faculty

of the

WORCESTER POLYTECHNIC INSTITUTE

in partial fulfillment of the requirements for the

Degree of Bachelor of Science

By

| Ryan Kendrick | Michael Moukarzel |

|---------------|-------------------|

| Date: Octo    | ober 11, 2007     |

|               |                   |

## **Abstract**

To extract data from highly sophisticated sensor networks, algorithms derived from graph theory are often applied to raw sensor data. Embedded digital systems are used to apply these algorithms. A common computation performed in these algorithms is finding the product of two sparsely populated matrices. When processing a sparse matrix, certain optimizations can be made by taking advantage of the large percentage of zero entries. This project proposes an optimized algorithm for performing sparse matrix multiplications in an embedded system and investigates how a parallel architecture constructed of multiple processors on a single Field-Programmable Gate Array (FPGA) can be used to speed up computations. Our final algorithm was easily parallelizable over multiple processors and, when operating on our test matrices, performed 49 times the operations per second than a normal full matrix multiplication. Once parallelized, we were able to measure a maximum parallel speedup of 5.2 over a single processor's This parallel speedup was achieved when the multiplication was performance. distributed over eight Microblaze processors, the maximum number tested, on a single FPGA. In this project, we also identified paths for the further optimization of this algorithm in embedded system design.

# **Executive Summary**

In the study of graph theory, a graph is defined as "Any mathematical object involving points and connections between them" (Gross & Yellen, 2004). Graphs are composed of sets of vertices which share connections between each other. The connections are referred to as edges. Graphs are used to model many systems that are of interest to scientists and engineers today such as communications between computers, social networks between people, and even bonds between proteins and molecules.

Through the act of graph processing, useful information from a graph can be extracted. Often times, algorithms to find the most important vertex in the graph or the shortest path between two vertices are applied. When a computer is used to apply these algorithms, each graph is represented as an adjacency matrix. Commonly, these matrices contain many more zeros than non-zeros meaning that they are considered sparse matrices; matrices with enough zeros in it that advantages can be had by exploiting them.

Graph processing algorithms often determine the most important vertex in a graph. Though the mathematics required to find a vertex's importance are outside the scope of this project, it is important to note that the majority of computational operations involved in performing this algorithm are due to the multiplications of sparse matrices.

The Embedded Digital Systems group at MIT Lincoln Laboratory focuses heavily on the study of knowledge processing. Knowledge processing is the act of transforming basic sensor data, bits and bytes, into actual useable knowledge. The data can often be modeled as a graph. Graph processing algorithms, such as vertex importance, are extremely time consuming and inefficient. This inefficiency means that in order to find results quickly, more powerful computers are needed to apply the algorithms. Often times, raw data are communicated from the sensor back to a more powerful computer to be processed. Because it would be faster, and require less communication bandwidth, a heavy focus exists on developing embedded digital systems that can perform graph processing algorithms quickly and efficiently at the front end of the sensor application.

Because embedded digital systems are often limited in both their memory size and their computational power, the key to making them perform graph processing algorithms faster is to reduce the requirements of the algorithm. Since these requirements are based

on graph theory, and thus process with sparsely populated matrices, exploiting their sparsity is the best way to reduce the requirements on the system. By storing and processing only non-zero values, the computational and memory requirements of a graph processing algorithm are minimized, allowing it to be performed on an embedded system.

This project sought to achieve two goals. The first goal was to develop an efficient, parallelizable algorithm for both the storage and multiplication of two sparse matrices. Current methods for performing the multiplication of these matrices on a microprocessor perform at operational efficiencies of between 0.05 and 0.1%. In this context, efficiency is defined as:

$$\% Efficiency = \frac{NonzeroOperations}{/TotalTime} x100\%$$

$$OperatingFrequency \times \# processors$$

Sparse matrix algorithms are made more operationally efficient if they perform more non-zero operations per clock cycle. The second goal was to investigate how the performance of this algorithm could be increased in by parallelizing operations over multiple processors in an embedded system. In this case, performance, measured in non-zero operations per second is calculated by the following equation:

$$Performance = \frac{NonzeroOperations}{TotalTime}$$

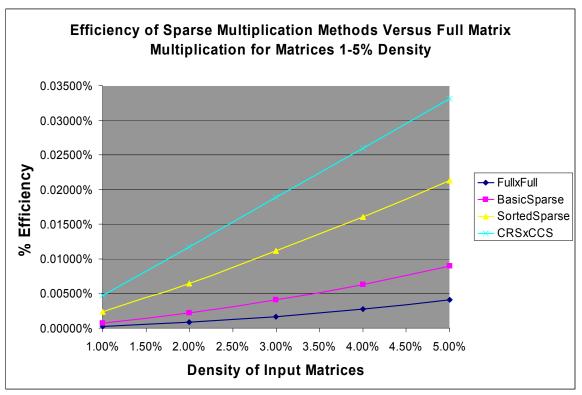

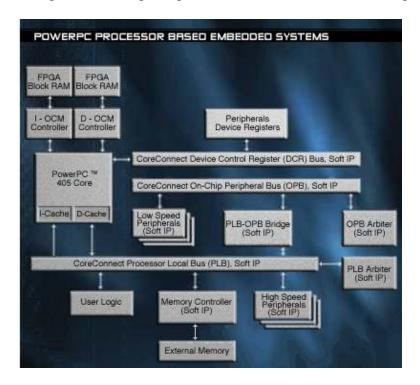

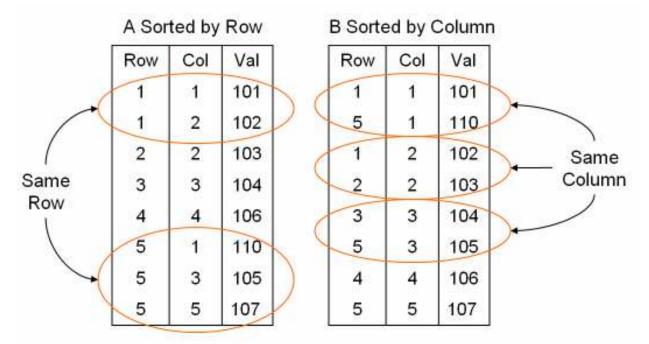

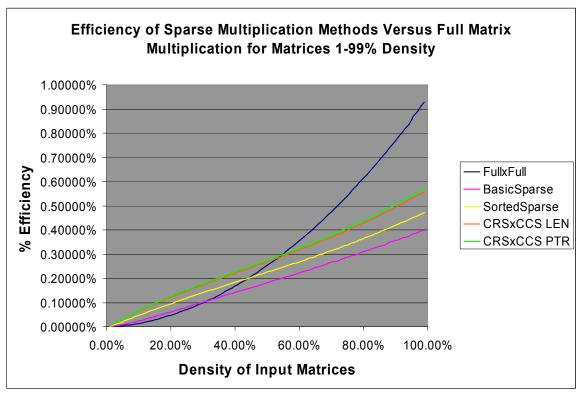

During the development of our multiply algorithm, we assumed that the input matrices could be in any storage format. Therefore we tested multiple types of formats for sparse matrices as well as their corresponding multiplication algorithms. Each of the storage formats and multiplication algorithms were developed and tested in MATLAB. Three storage types of storage formats in addition to full matrix format were tested in all. The aim of these tests was to determine the most efficient methods for storing and multiplying sparse matrices. The first was a basic sparse matrix storage format, which stored only the non-zero value. Next, because matrix multiplication is basically repeated row by column multiplication, a sorted sparse method was tried in which the first matrix was sorted by row and the second was sorted by column. Finally we tested compressed storage formats, specifically compressed row storage (CRS) by compressed column storage (CCS). Our test proved that CRSxCCS multiplication performed more efficiently

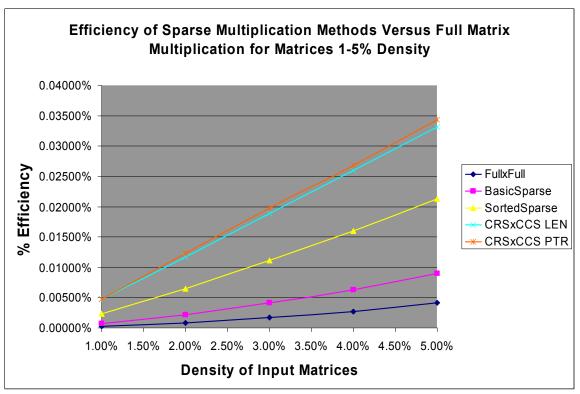

than any other format for sparse matrices with densities 1% to 5%. Results of these tests are shown in Figure 1.

Figure 1: Multiplicational Efficiency of Various Sparse Storage Formats

This figure shows the multiplication algorithm's efficiency for each of the sparse storage formats we tested compared to the efficiency of a full matrix multiplication for sparse matrices of 1-5% density.

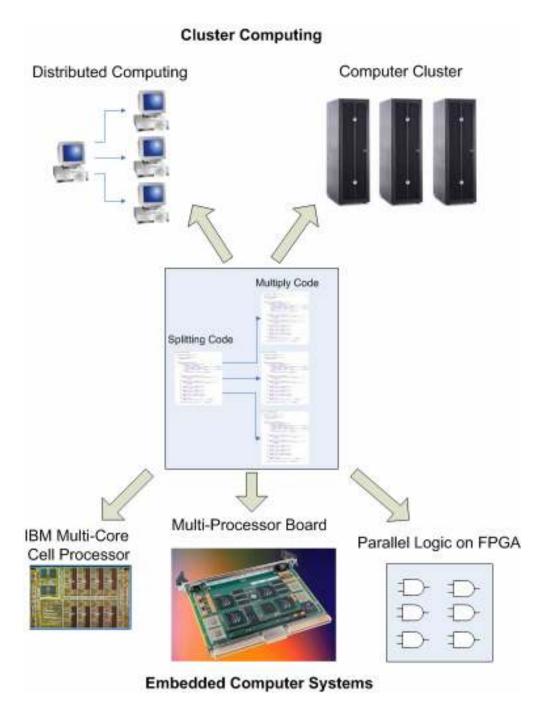

Once our multiplication algorithm had been determined, we parallelized it on a single Field-Programmable Gate Array. An FPGA is a type of programmable logic device which is well suited for embedded systems design. FPGAs consume less power and use less space than a programmable processor performing the same function. An FPGA allows an engineer to implement virtually any digital circuit imaginable through the use of a hardware definition language (HDL). HDL files to implement many commonly used functions can be found online. These files are referred to as Intellectual Property (IP) cores and can implement a wide range of functions such as USB drivers, signal processing applications, and even programmable microprocessors. A programmable microprocessor implemented in the logic of an FPGA through an HDL is referred to as a soft-core processor. Soft-core processors are often used in FPGA development because they are easy to implement and can interface easily with specialized hardware circuits on the FPGA.

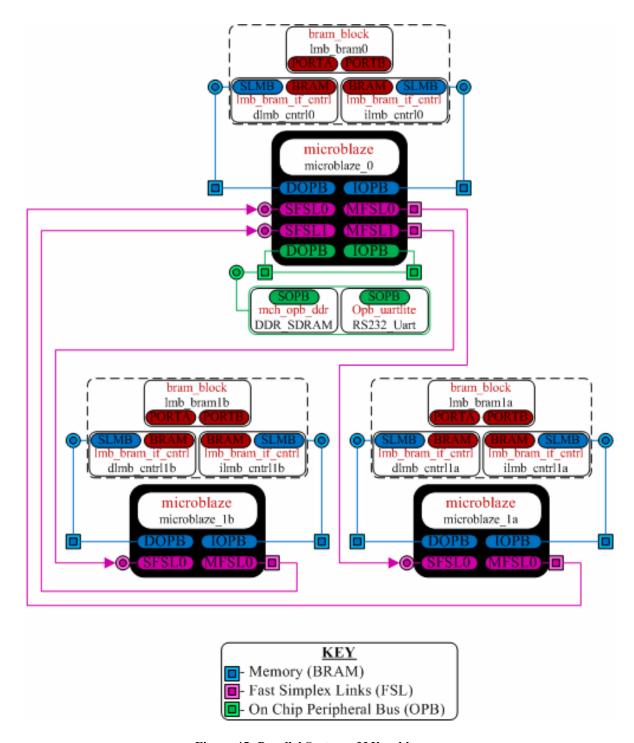

This project used multiple Microblaze soft-core processors working in parallel on one Xilinx Inc. FPGA to increase the performance of a sparse matrix multiplication algorithm. Our final design incorporated a highly optimized matrix multiplication algorithm, a parallel architecture, and an advanced matrix splitting technique to achieve a parallel speedup of the multiplication algorithm on a single FPGA.

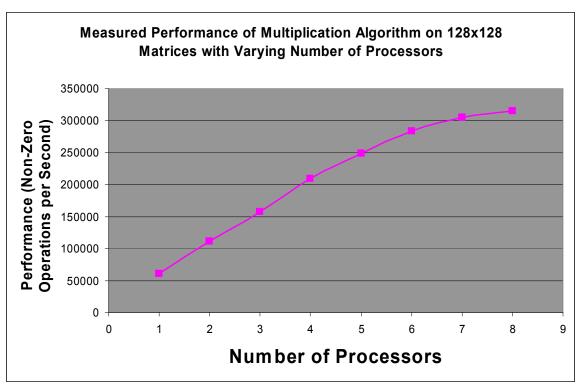

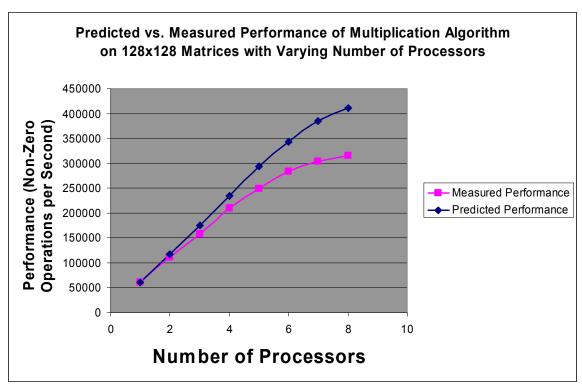

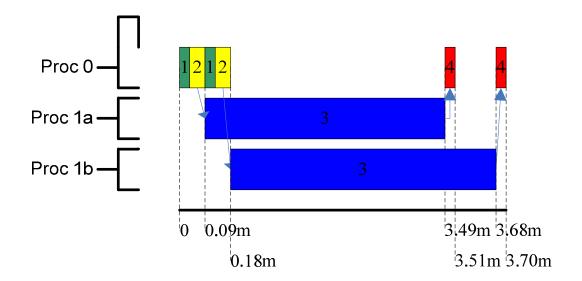

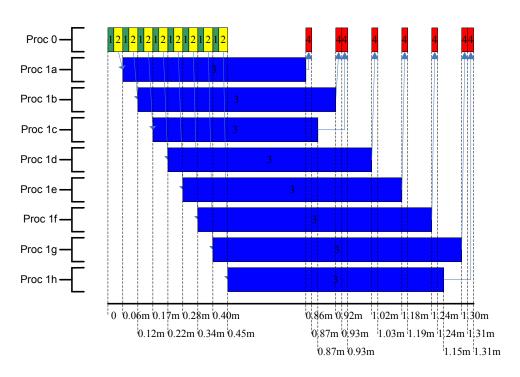

Our final matrix multiplication was able to multiply two sparse matrices, A and B, stored in CRS and CCS formats, respectively. The algorithm was highly parallelizable and was capable of computing the product of two 128x128 sparse matrices with 1% density 49 times faster than the speed at which a full matrix multiplication was capable. This type of algorithmic performance was comparable to the abilities of other optimized sparse matrix multiplication algorithms, but was highly parallelizable. A parallel implementation of this algorithm achieved a speedup of 5.20 when mapped over eight parallel processors. The algorithm consisted of a load distribution technique that split matrix B into submatrices of its columns, thereby providing intelligent distribution of the matrix multiplication workload among multiple processors. Figure 2 shows the measured speedups provided by parallelizing our algorithm over a varying number of Microblazes.

Figure 2: Matrix Multiplication Algorithm Performance over Multiple Processors

This plot shows the speedups achieved by mapping our final matrix multiplication algorithm over a varying number of parallel processors. The test matrices were 128x128 matrices with 1% density.

A major recommendation for future research into sparse matrix multiplication on FPGAs would be to implement the matrix multiplication algorithm in logic on the FPGA rather in software on a soft-core processor. Implementing a matrix multiplication in the logic circuitry on an FPGA could provide a projected efficiency increase of 11 over the current abilities of the soft-core Microblaze processor to perform this computation and would assist in developing highly optimized embedded system designs to perform sparse matrix multiplication.

# **Contributions**

This project was completed by Ryan Kendrick and Michael Moukarzel of the WPI class of 2008.

In the summer of 2007, prior to working on this MQP, Ryan and Michael worked as summer interns at MIT Lincoln Laboratory. During this period of time, background research was performed to determine optimized algorithms to be implemented on the FPGA. Michael focused mostly on the testing and development of various data structures, multiplication algorithms, and conversions between storage formats while Ryan focused his efforts on background mathematical research into the algorithms and the testing of various load distribution techniques.

Once the actual project began Michael shifted his efforts towards the actual implementation of these algorithms on the Xilinx FPGA in C-code. His work consisted of the configuring of Microblaze processors and their communication links in hardware on the FPGA. Also, Michael was responsible for loading code to these Microblazes and debugging to be sure the code worked properly in the system.

Ryan assisted in technical work for the first few weeks of this project, converting his MATLAB algorithms for matrix splitting to C-code. After writing this code for the FPGA implementation, Ryan took on the responsibility of editing the MQP paper. Though Ryan still took part in every technical decision made during the course of this project, the primary focus of his efforts was the development of the MQP paper and the presentations.

Both partners have reviewed their contributions to this project and both feel that each contributed equally to the overall efforts involved in completing this project.

# **Table of Contents**

| Abstract      |                                                        | ii |

|---------------|--------------------------------------------------------|----|

|               | Summary                                                |    |

|               | ons                                                    |    |

| List of Illus | strations                                              | xi |

| 1 Introd      | uction                                                 | 13 |

| 1.1 F         | roject Goals                                           | 17 |

| 1.1.1         | Goal Measurementt Metrics                              | 18 |

| 2 Backg       | round                                                  | 19 |

| 2.1           | Graph Processing                                       | 19 |

| 2.2           | parse Matrices                                         | 22 |

| 2.2.1         | Sparse Matrix Storage                                  | 23 |

| 2.2.2         | Compressed Column Storage (CCS)                        | 24 |

| 2.2.3         | Compressed Row Storage (CRS)                           | 26 |

| 2.2.4         | The Length Vector vs. Pointer                          |    |

| 2.2.5         | Compressed Diagonal Storage (CDS)                      | 27 |

| 2.2.6         | Storage Size Comparison                                |    |

| 2.2.7         | Matrix Multiplication                                  | 32 |

| 2.3 N         | Matrices of Interest                                   | 33 |

| 2.4 F         | Tield Programmable Gate Arrays (FPGAs)                 | 36 |

| 2.4.1         | FPGA Architecture                                      | 38 |

| 2.4.2         | Soft-Core Microprocessors                              | 41 |

| 2.4.3         | PowerPC processor                                      | 44 |

|               | ML310 Development Board                                |    |

| 2.6 Y         | Kilinx Virtex-II Pro XC2VP30                           | 48 |

| _             | ithm Performance Analysis                              |    |

| 3.1           | Optimized Matrix Multiplication Algorithm              | 49 |

| 3.1.1         | Full Matrix Multiplication                             |    |

| 3.1.2         | Sparse Matrix Multiplication                           |    |

| 3.1.3         | Sorted Sparse Matrix Multiplication                    | 53 |

| 3.1.4         | CRS x CCS Matrix Multiplication Using Pointer          |    |

| 3.1.5         | CRS x CCS Matrix Multiplication Using Length           |    |

| 3.1.6         | Counting Non-Zero Operations                           |    |

| 3.1.7         | Algorithm Efficiency Results                           |    |

| 3.2           | Optimized Parallelization and Load Balancing Technique |    |

| 3.2.1         | Pointer vs. Length Vector in Parallelization           |    |

| 3.2.2         | Block-Column Distribution                              |    |

| 3.2.3         | Block-Values Distribution                              |    |

| 3.2.4         | Block-Cyclic Distribution                              |    |

| 3.2.5         | Inverse Block-Cyclic Distribution                      |    |

| 3.2.6         | Column-Cyclic Distribution.                            |    |

| 3.2.7         | Performance Evaluation of Load Balancing Techniques    |    |

| 4 FPGA        | Implementation                                         | 75 |

|    | 4.1.1      | Microblaze Multiplication                                      | 75  |

|----|------------|----------------------------------------------------------------|-----|

|    | 4.1.2      | Parallel Microblaze Load Distribution                          | 76  |

| 5  |            | nm Performance Results                                         |     |

|    | 5.1 CR     | SxCCS Multiplication vs. Full Matrix Multiplication in C       | 79  |

|    |            | eoretical Maximum Allowable Matrix Size                        |     |

|    | 5.3 FP     | GA Parallel Speedup Predictions                                | 86  |

|    | 5.3.1      | Microblaze Execution Speed                                     | 86  |

|    | 5.3.2      | Fast Simplex Link                                              |     |

|    | 5.3.3      | Microblaze System Theoretical Performance Estimate             | 89  |

|    | 5.4 FP     | GA Parallel Speedup Measurements                               |     |

| 6  | Discuss    | ion and Conclusions                                            | 95  |

|    | 6.1 Sp     | arse Matrix Multiplication Algorithm                           | 95  |

|    | 6.2 Par    | allelization of Multiplication Algorithm on FPGA               | 96  |

|    | 6.3 Fu     | ture Recommendations                                           | 97  |

|    | 6.4 Fu     | ture Impacts                                                   | 100 |

| A  | nnotated R | eference List                                                  | 103 |

| A  | ppendix A. |                                                                | 108 |

|    | Full Matri | x Multiplication                                               | 108 |

|    |            | rse Matrix Multiplication (Unsorted)                           |     |

|    | Sorted Spa | rse Matrix Multiplication                                      | 110 |

|    | Compresso  | ed Sparse Matrix Multiplication (CRSxCCS) using Pointer Vector | 111 |

|    | Compresso  | ed Sparse Matrix Multiplication (CRSxCCS) using Length vector  | 112 |

| A  | ppendix B. |                                                                | 114 |

|    | Block-Col  | umn Distribution                                               | 114 |

|    | Block-Val  | ues Distribution                                               | 115 |

|    | Block-Cyc  | elic Distribution                                              | 117 |

|    | Inverse Bl | ock-Cyclic Distribution                                        | 120 |

|    | Column-C   | yelic Distribution                                             | 123 |

| A  | ppendix C. |                                                                | 125 |

| A  | ppendix D. |                                                                | 127 |

| A  | ppendix E. |                                                                | 128 |

|    |            | yelic Splitting                                                |     |

|    | Column-C   | yclic Reassembly                                               | 129 |

| A  | ppendix F  |                                                                | 131 |

|    | 1 1        |                                                                |     |

|    |            |                                                                |     |

|    |            |                                                                |     |

|    | 1 1        |                                                                |     |

| IF | EEE Code o | f Ethics                                                       | 153 |

# **List of Illustrations**

| Figure 1: Multiplicational Efficiency of Various Sparse Storage Formats          | V      |

|----------------------------------------------------------------------------------|--------|

| Figure 2: Matrix Multiplication Algorithm Performance over Multiple Processors   | vii    |

| Figure 3: Graph Example                                                          |        |

| Figure 4: Knowledge Processing                                                   | 15     |

| Figure 5: Small Social Network Represented by a Graph                            | 19     |

| Figure 6: Adjacency Matrix Representation of Social Network Graph                | 20     |

| Figure 7: Full Matrix Format                                                     |        |

| Figure 8: Sparse Matrix Format                                                   |        |

| Figure 9: Compressed Column Format (CCS)                                         | 25     |

| Figure 10: Compressed Row Format (CRS)                                           | 26     |

| Figure 11: Compressed Column using Length Vector                                 | 27     |

| Figure 12: Diagonal Assignments in Compressed Diagonal Storage                   | 28     |

| Figure 13: Diagonal Vector Example                                               | 28     |

| Figure 14: Diagonal Values                                                       | 29     |

| Figure 15: Banded Matrix Example                                                 | 30     |

| Figure 16: Storage Method Sizes on a Square Matrix                               | 31     |

| Figure 17: General form for Matrix Multiplication                                |        |

| Figure 18: General Form for Computing a Dot Product                              | 33     |

| Figure 19: Structured RMAT Matrix                                                | 34     |

| Figure 20: Randomized RMAT Matrix                                                | 35     |

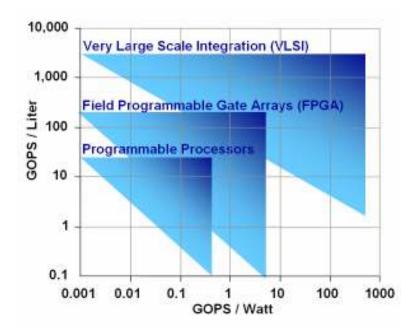

| Figure 21: Performance Density and Efficiency between device families            | 37     |

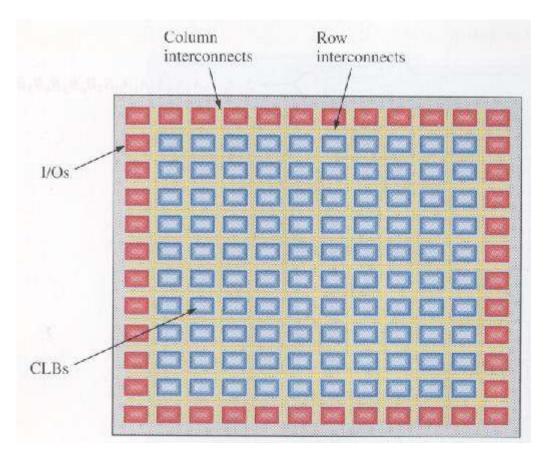

| Figure 22: FPGA Architecture                                                     | 39     |

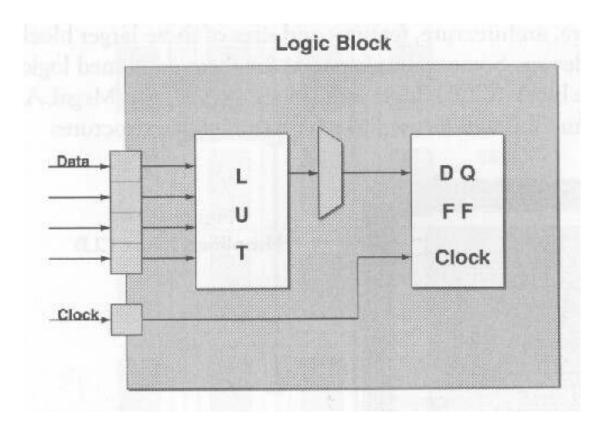

| Figure 23: FPGA Logic Block                                                      | 40     |

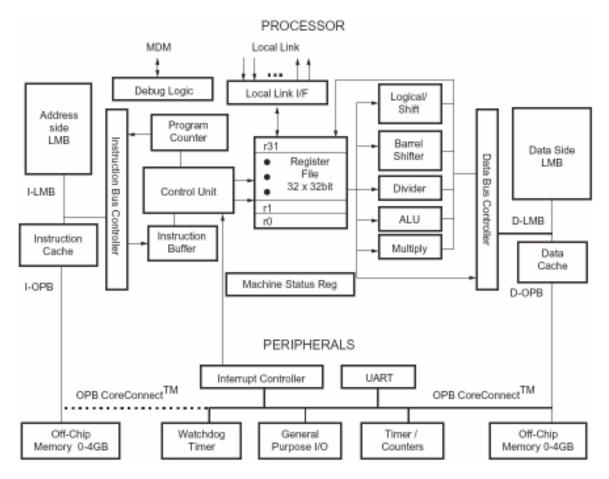

| Figure 24: Microblaze Architecture                                               | 43     |

| Figure 25: Software Algorithm vs. Hardware                                       | 44     |

| Figure 26: PowerPC Architecture                                                  | 45     |

| Figure 27: Xilinx ML310 Development Board                                        | 47     |

| Figure 28: Data Locality in Sorted Sparse Matrix Multiplication                  | 54     |

| Figure 29: Efficiency of Different Multiplication Methods 1-99% Density          | 57     |

| Figure 30: Efficiency of Different Multiplication Methods 1-5% Density           | 58     |

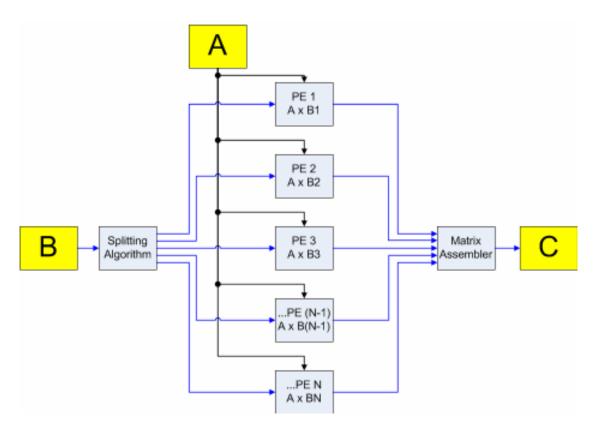

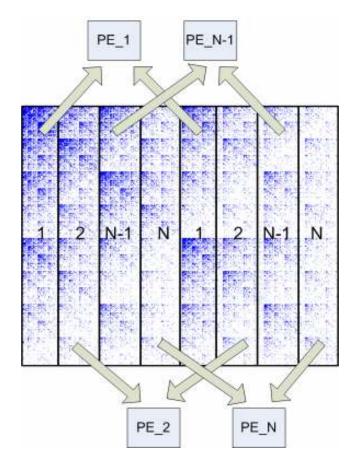

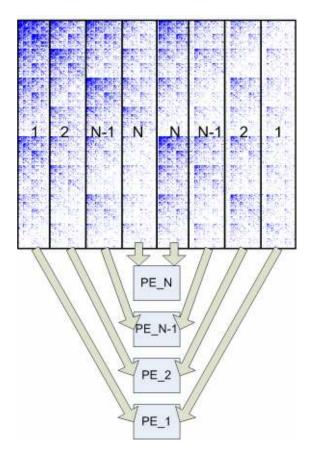

| Figure 31: Parallelization Block Diagram                                         | 60     |

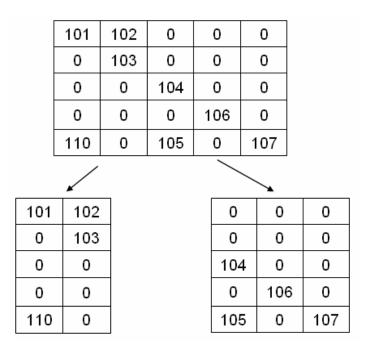

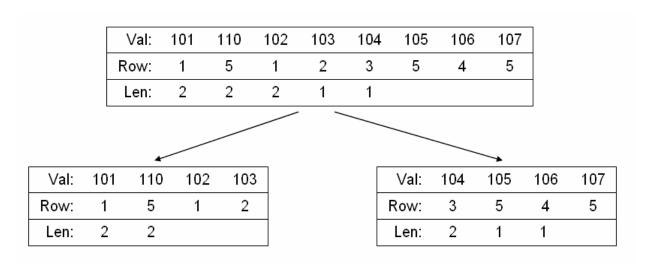

| Figure 32: Splitting a Full Matrix into Smaller Matrices                         | 62     |

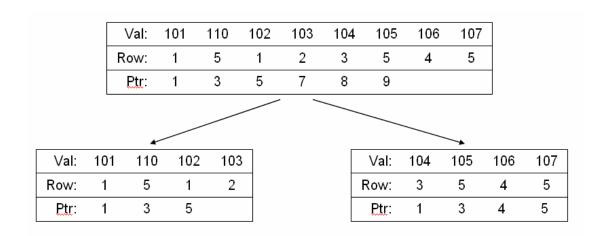

| Figure 33: Split Matrices Stored using Pointer                                   | 62     |

| Figure 34: Split Matrices Stored using Length                                    | 63     |

| Figure 35: Block-Column Load Distribution                                        | 65     |

| Figure 36: Block-Values Load Distribution                                        | 66     |

| Figure 37: Block-Cyclic Load Distribution                                        | 68     |

| Figure 38: Inverse Block-Cyclic Load Distribution                                | 69     |

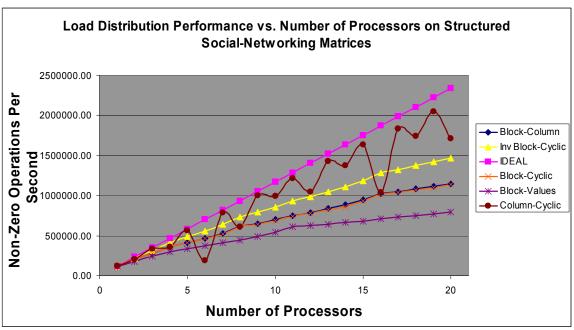

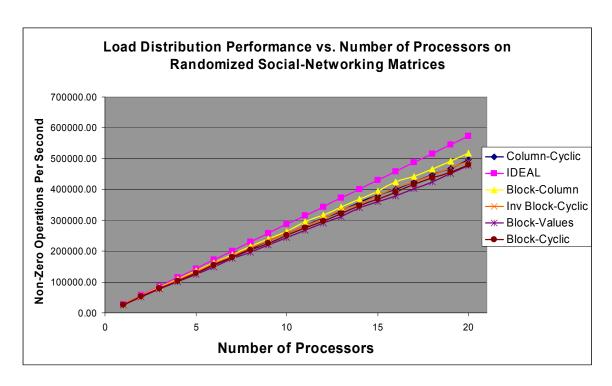

| Figure 39: Performance of Various Load Balancing Techniques on Structured Matrix |        |

| Figure 40: Performance of Various Load Balancing Techniques on Randomized Mat    | trix74 |

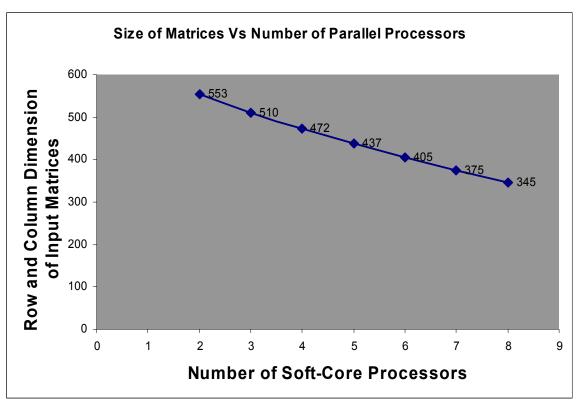

| Figure 41: Allowable Memory per Input Matrix Estimate                            |        |

| Figure 42: Required Memory Space of Compressed Matrix                            |        |

| Figure 43: Size of Input Matrices vs Number of Processors                        |        |

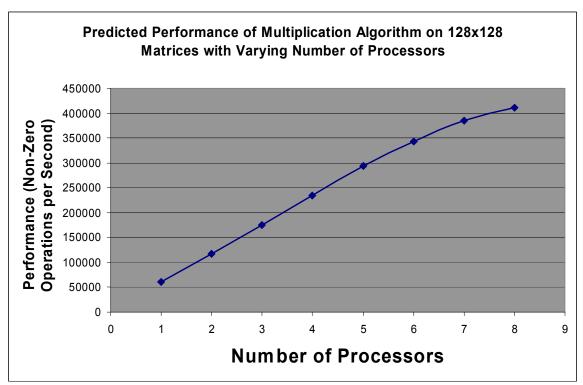

| Figure 44: Theoretical Parallel Microblaze Performance                           | 89     |

| Figure 45: Parallel System of Microblazes                                      | 91  |

|--------------------------------------------------------------------------------|-----|

| Figure 46: Measured Performance of Parallel Multiplication of 128x128 Matrices | 93  |

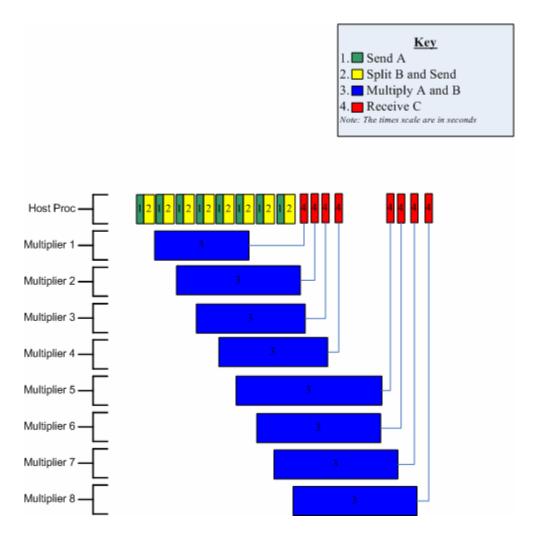

| Figure 47: Realistic Timeline of Parallel Algorithm                            | 94  |

| Figure 48: Proposed Logic Circuit States to Perform Matrix Multiplication      | 99  |

| Figure 49: Projected Speedups with Microblazes and Logic Circuits              | 100 |

| Figure 50: Parallelizable Algorithm in Multiple Computer Environments          | 102 |

# 1 Introduction

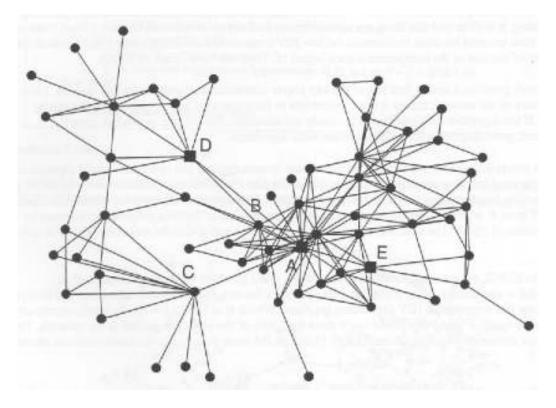

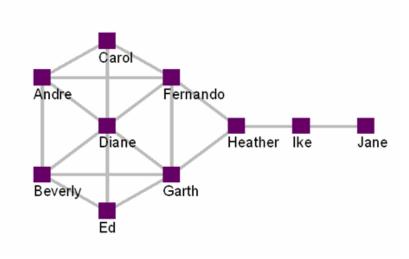

In the study of graph theory, a "graph" is defined as "Any mathematical object involving points and connections between them" (Gross & Yellen, 2004). The individual elements in a graph are referred to as "vertices" while the various interconnections between them are "edges." Figure 3 shows an example of a graph. The idea of a graph can be used to model many different types of science and engineering problems today.

Figure 3: Graph Example

This is an example of a graph. The various vertices are shown by either a black box or circle while the various interconnections. "Edges" are shown as black lines connecting the vertices. (Borgatti, 2003)

Graphs can be used to represent physical structures such as computer networks, transportation systems, pictures, or even interconnections between proteins and molecules. More abstract ideas can also be represented by graphs such as social relationships between people. Useful results such as computing the shortest path between

a pair of vertices or the most important vertex in a network can be found through the application of graph processing algorithms. These results prove to be extremely useful in many applications.

The identification of a shortest path between two vertices in a network could be a meaningful result for a telecommunications company wanting to send a message through their network with the shortest delay. Other applications for this result include "geographical information systems, operations research, plant and facility layout, robotics, transportation, and [electrical circuit] design." (Chen, 2007)

Identification of the most important vertex in a network would be helpful information for an electricity company which could identify the most important power stations to the functioning of its power grid. Perhaps the Northeast Blackout of 2003 may not have happened if the power companies had real time data about their infrastructure. The result could also help determine vulnerable points in a network, both for strengthening or disabling a network:

The meaningful purpose for attack vulnerability studies is for the sake of protection: If one wants to protect the network by guarding or by a temporary isolation of some vertices, the most important vertices, breaking of which would make the whole network malfunction, should be identified. Furthermore, one can learn how to build attack-robust networks, and also how to increase the robustness of vital biological networks. Also in a large network of criminal organization, the whole network can be made to collapse by arresting key persons, which can be identified by a similar study.(Holme et al., 2002)

These graph computations such as calculating the shortest path or the most important vertex can be useful in many types of analyses. There are multiple other characteristics one can derive from the analysis of a graph which are also extremely useful.

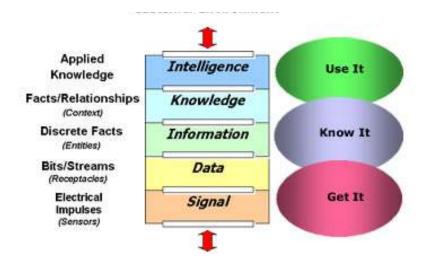

At MIT Lincoln Laboratory in Lexington, Massachusetts researchers work on the development of highly sophisticated surveillance and intelligence systems. Group 102, the Embedded Digital Systems group, focuses on what is called knowledge processing. Knowledge processing is the act by which raw data from a camera, radar, antenna, or some other sensor, is converted into useable information. In these surveillance systems, this work is carried out by small embedded computer systems which accompany the sensor itself. Figure 4 shows an example of the steps involved in knowledge processing.

Figure 4: Knowledge Processing

This figure shows, from bottom to top, the transition of raw data collected from sensors up to the intelligence level where it can actually be used. This transition is done through the process known as knowledge processing. In the case of modern sensor systems, some of this information takes the form of graphs. (http://www.nsa.gov)

A large percentage of the data processed by these systems takes the form of graphs. Since a tactical advantage is held by whoever can translate information from the bit level to actual knowledge the fastest, a strong focus is placed on performing graph processing algorithms faster and more efficiently.

Once entered into a computer, the information no longer looks like a graph.

Often, it takes the form of a sparsely populated matrix (a matrix containing a majority of zeros) called an adjacency matrix. During knowledge processing, intelligence is

extracted from the matrices using various algorithmic tools. A common kernel performed in these algorithms is the multiplication of two adjacency matrices. Tests on matrix multiplication algorithm performance have been conducted by group 102 of MIT Lincoln Laboratory. The results showed efficiencies, or the percentage of arithmetic operations performed out of the peak possible arithmetic operations, of between 0.05 and 0.1% when performed on conventional microprocessor systems (Bliss, 2007).

Our project focused on finding a matrix multiplication algorithm that performed with efficiency similar to those of current algorithms, but was highly parallelizable. We focused on demonstrating the parallelizable properties of our algorithm through implementation on a system of multiple parallel processors in an embedded system design. This design achieved speedup through the utilization of the matrix multiplication algorithm and a load distribution algorithm which distributed the workload evenly among parallel processors.

Since certain advantages can be had when dealing with a sparse matrix, this project explored various formats for the storage of sparse matrices. These formats were used to develop a more efficient algorithm for the multiplication of sparse matrices. Once an optimized matrix multiplication algorithm was developed, an effective method for parallelizing its operations on an embedded system was determined.

The final result of this project was to implement a field-programmable gate array (FPGA), a common type of programmable logic chip in embedded system design, which was capable of performing our algorithm. The FPGA implementation demonstrated how the matrix multiplication process, a key kernel in graph processing, can be made more

efficient by exploiting the sparsity of the matrices in a more efficient multiplication algorithm and how parallelization of operations can speed up the entire kernel.

The two main goals of this project were to develop an efficient algorithm for the multiplication of two sparse matrices and to implement a way of easily parallelizing this algorithm in a small embedded system. By utilizing a sparse matrix storage method, the storage requirements for many matrices that, if stored in full format, were too large to be stored on an FPGA, became small enough be processed in a single FPGA. With multiple processors working together in parallel, the final FPGA design performed perform many more non-zero arithmetic operations per second than a single processor could perform. The final result design can serve as an example for future research into the area of optimized sparse matrix multiplication. It can also serve as a model for a complete hardware implementation of this algorithm, such as the development of an Application-Specific Integrated Circuit (ASIC) which would be able to perform these multiplications faster than any other device.

# 1.1 Project Goals

The goals of this project were as follows:

- **1.** To determine a highly parallelizable method for the storage and multiplication of two sparsely populated matrices which can perform computations at efficiencies comparable to the 0.05% to 0.1% achieved by optimized sparse matrix multiplications on traditional microprocessor systems

- **2.** To demonstrate how the optimized multiplication algorithm can be parallelized on a single FPGA to achieve a parallel speedup by distributing the load over multiple processing elements.

#### 1.1.1 Goal Measurementt Metrics

To compute the product of two sparse matrices, there are a certain number of arithmetic operations that must occur regardless of how the matrix is stored. These operations are the multiplications and additions of non-zero entries in the two matrices.

In goal number one of this project, we aimed for efficiency and parallelizability. Efficiency means we will be calculating the total number of non-zero operations performed divided by the total number of possible non-zero operations. One clock tick on one processor is the time required to perform one non-zero operation. Therefore, our equation to calculate efficiency is as follows:

$$\% Efficiency = \frac{Nonzero Operations / Total Time}{Operating Frequency \times \# \ processors} x 100\%$$

Therefore, the efficiency of our algorithm is independent of the number of processors used and somewhat independent of the clock cycle of those processors.

Performance is only the numerator of the efficiency formula. Our measure of performance will depend solely on the number of non-zero operations done and the time required to perform them. The performance is expressed in units of non-zero operations per second:

$$Performance = \frac{NonzeroOperations}{TotalTime}$$

Therefore, the performance of our design can be increased with the addition of more processors working in parallel or by increasing the clock speed of those processors.

# 2 Background

## 2.1 Graph Processing

Graph processing extracts meaningful data from a graph of vertices and edges. Studying a graph of vertices with numerous interconnections between them is not only of interest to Lincoln Laboratory, but also can help scientists and engineers in other industries. An easily visualized example of modeling using a graph is a small social network. Suppose Diane is a popular member of her class, and knows many people such as Andre, Carol, and Ed. A graph representing her social network might look something like Figure 5:

Figure 5: Small Social Network Represented by a Graph

This figure shows how a social network of friends can be represented by a graph. The people in the graph are represented by vertices while the fact that two of them have some sort of relationship together is shown by an edge connecting their two vertices.

It is easy to see from this graph that Diane is obviously an important person in this network. Beverly and Fernando do not know each other, but the easiest way for them to meet would be through Diane. The same situation is had by Andre and Garth. Also, Heather, even though she doesn't know Diane, is an important person in this network; she

serves as the only connection between Ike and Jane and the rest of the network. (Robinson, 2007)

When these types of graphs are processed on a computer, they are stored in the form of an adjacency matrix. The following is an example of an adjacency matrix representation of Diane's network.

|          | Andre | Beverly | Carol | Diane | Ed | Fernando | Garth | Heather | lke | Jane |

|----------|-------|---------|-------|-------|----|----------|-------|---------|-----|------|

| Andre    | 0     | 1       | 1     | 1     | 0  | 1        | 0     | 0       | 0   | 0    |

| Beverly  | 1     | 0       | 0     | 1     | 1  | 0        | 1     | 0       | 0   | 0    |

| Carol    | 1     | 0       | 0     | 1     | 0  | 1        | 0     | 0       | 0   | 0    |

| Diane    | 1     | 1       | 1     | 0     | 1  | 1        | 1     | 0       | 0   | 0    |

| Ed       | 0     | 1       | 0     | 1     | 0  | 0        | 1     | 0       | 0   | 0    |

| Fernando | 1     | 0       | 1     | 1     | 0  | 0        | 1     | 1       | 0   | 0    |

| Garth    | 0     | 1       | 0     | 1     | 1  | 1        | 0     | 1       | 0   | 0    |

| Heather  | 0     | 0       | 0     | 0     | 0  | 1        | 1     | 0       | 1   | 0    |

| lke      | 0     | 0       | 0     | 0     | 0  | 0        | 0     | 1       | 0   | 1    |

| Jane     | 0     | 0       | 0     | 0     | 0  | 0        | 0     | 0       | 1   | 0    |

Figure 6: Adjacency Matrix Representation of Social Network Graph

This figure is an adjacency matrix showing how the graph in Figure 5 can be represented as sparsely populated matrix. The number of rows and columns is equal to the number of vertices in the graph. An edge is represented by a one in the intersecting rows and columns of the two vertices it connects.

The adjacency matrix shown above is a way of showing which vertices in a graph are connected by an edge. For example, the graph on the previous page showed that Diane knew six other people; these relationships were shown as an edge connecting Diane to her friends. In an adjacency matrix, these edges are shown as a one in the cell which is the intersection of Diane's column and her friends' rows. Also, a one will be found in the intersection of Diane's row and her friends' columns.

Zeros are found along the main diagonal, in the intersection of each person's row and column. Some adjacency matrices store all ones along the main diagonal and some do not; whether these cells are filled with zeros or not usually depends on the application. Also, while the adjacency matrix in Figure 6 has symmetry across the diagonal, not all adjacency matrices have this symmetry. In unidirectional adjacency matrices, vertex A can be connected to vertex B without B being connected back to A.

Adjacency matrices sometimes use values other than one in cells to show the strength of an edge. For example, if Andre and Fernando were brothers rather than just friends, a three or a four may be contained in their intersecting cells rather than just a one to signify a stronger relationship.

Once these graphs grow to contain hundreds or thousands of vertices and edges, computers become responsible for locating the important vertices. To find them, an algorithm to find the "betweenness centrality" of a certain vertex is used. Vertices which are on the shortest path between many other pairs of vertices have a high betweenness centrality. In the graph example, Diane appeared on the shortest path between many other people, therefore she was an important vertex on the graph.

The matrix representation of a graph is commonly large and sparsely populated. In the adjacency matrix above, there are 100 cells, only 36 of which contain a non-zero value; commonly, this type of matrix is referred to as a sparse matrix. For a graph with N vertices, the number of cells in its adjacency matrix is N<sup>2</sup>. When dealing with a graph of tens or even hundreds of thousands of vertices, adjacency matrices become too large to be processed by an average desktop computer.

Though betweenness centrality algorithms are complicated and outside the scope of this project, their performance "is dominated by sparse matrix multiply performance" (Robinson, 2007). The sparse matrix multiply kernel is *the* limiting factor in performing this algorithm. Conventional algorithms which perform these multiplications prove extremely inefficient. Since the number of zeros in a sparse matrix is high, the frequency of a meaningful calculation—multiplying or adding two non-zero values together—is low. Often, when sparse matrix multiplication algorithms are performed on a conventional processor, the frequency of non-zero multiplies with relation to the computer's clock cycle is low, between 0.05% and 0.1%. To effectively handle sparse matrices, specialized formats can be used to store only the non-zero values, thus shrinking the size of the matrix in memory greatly. These formats will be discussed in the next section.

# 2.2 Sparse Matrices

There is no concrete rule defining when a matrix is sparse and when it is not. Professor Tim Davis from the University of Florida claims a sparse matrix is: "...any matrix with enough zeros that it pays to take advantage of them" (Davis, 2007). This definition means that whether or not a matrix is sparse depends on how many zero entries it has as well as how well the user can take advantage of those zeros. When dealing with large sparsely populated matrices, an increasingly common technique to process and store them is to take advantage of their sparsity. Since many of the sparse matrices used in science and engineering today have large dimensions, on the order of tens or hundreds of thousands, exploiting the sparsity of a matrix can give enormous advantages in both storage space required and processing efficiency. There are two ways one would exploit

the sparsity of a matrix: first, to store only the non-zero elements of the matrix and second, to process only the non-zero elements of the matrix. (Zlatev, 1991)

#### 2.2.1 Sparse Matrix Storage

A full matrix representation of a matrix stores every value, regardless of whether it is zero or non-zero. The total size is approximately equal to:

$$FullMatrixMemory = (\#ofRows) \times (\#ofColumns)$$

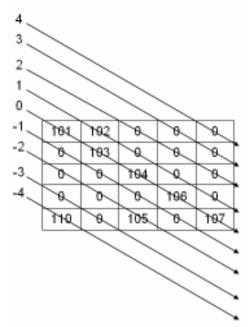

Note: This calculation is approximate because some other small values may be stored such as the number of rows and the number of columns. If this matrix is sparsely populated, meaning it contains a majority of zero entries, the storage space can be reduced greatly by using a sparse matrix storage technique. To demonstrate how one converts a sparsely populated matrix into a sparse matrix format an example will be given. Figure 7 is a five by five full matrix with only eight non-zero entries: Only eight non-zeros means the computer is storing 17 zero values which are not needed.

| 101 | 102 | 0   | 0   | 0   |

|-----|-----|-----|-----|-----|

| 0   | 103 | 0   | 0   | 0   |

| 0   | 0   | 104 | 0   | 0   |

| 0   | 0   | 0   | 106 | 0   |

| 110 | 0   | 105 | 0   | 107 |

Figure 7: Full Matrix Format

The full matrix storage format is shown above. It stores all values in the matrix, non-zero and zero. It becomes an inefficient storage method when the majority of the values are zero.

To take advantage of the fact that a matrix is sparse it can be converted into a sparse matrix storage format. A sparse format means only the non-zero entries are stored as well as their corresponding row and column indices. MATLAB, the powerful

mathematics and engineering program, currently uses this basic sparse matrix format.

The following figure is the same matrix as shown above stored in the basic sparse format.

| Row | Col | Val |

|-----|-----|-----|

| 1   | 1   | 101 |

| 5   | 1   | 110 |

| 1   | 2   | 102 |

| 2   | 2   | 103 |

| 3   | 3   | 104 |

| 5   | 3   | 105 |

| 4   | 4   | 106 |

| 5   | 5   | 107 |

**Figure 8: Sparse Matrix Format**

The most basic form of sparse matrix storage formats. It stores the corresponding row, column, and value of every non-zero entry in the matrix.

The total space required to store a matrix in the basic sparse matrix format is approximately equal to:

$$BasicSparseMatrixMemory = 3 \times (\# Nonzeros)$$

This method stores three values for every non-zero entry in the matrix. Therefore, for matrices with less than 33% density, the sparse matrix storage method will use less memory space than a full matrix storage method.

# 2.2.2 Compressed Column Storage (CCS)

The fact that the column vector is sorted can be taken advantage of to further compress this matrix. Instead of storing the column vector entirely, a column pointer can be stored. The column pointer is a vector telling the user when the column pointer

increments and can be made much shorter than the original column vector shown in Figure 8.

An extra number is added to the pointer vector equal to the total number of non-zero entries plus one. With the compression of the column vector to a pointer, the total number of values stored in memory will be approximately equal to:

$$CCSMatrixMemory = 2 \times (\#Nonzeros) + (\#ofColumns) + 1$$

Figure 9 shows the same matrix stored in a compressed column format (Dongarra, 2007). Two consecutive pointer values being equal indicates that the column vector has incremented twice on that entry and thus there is an empty column.

| Val: | 101 | 110 | 102 | 103 | 104 | 105 | 106 | 107 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Row: | 1   | 5   | 1   | 2   | 3   | 5   | 4   | 5   |

| Ptr: | 1   | 3   | 5   | 7   | 8   | 9   |     |     |

Figure 9: Compressed Column Format (CCS)

This figure is an example of the compressed column storage format. This format stores the value, row, and column pointer of the non-zero entries in the matrix. The column pointer tells the user on which entries in the value vector, are stored in the next column from the previous entry.

To find how many entries are in any column, the user just needs to find the difference between the sequential pointer values. For example: to find out how many entries there are in column three, entry three in the pointer would be subtracted from entry four. In the above example, the numbers are five and seven. We can conclude that there are two entries in column three and the first one is entry number five in the value vector. Likewise, if there are two repeated numbers in the pointer, there is an empty column in the matrix.

#### 2.2.3 Compressed Row Storage (CRS)

It is important to notice that the same process for compression applies to a compressed row format. The difference is that the entries will be sorted according to row rather than column and there will be a row pointer instead of a column pointer. The following is the same matrix stored in compressed row storage rather than compressed column. (Dongarra, 2007)

| Val: | 101 | 102 | 103 | 104 | 106 | 110 | 105 | 107 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Col: | 1   | 2   | 2   | 3   | 4   | 1   | 3   | 5   |

| Ptr: | 1   | 3   | 4   | 5   | 6   | 9   |     |     |

Figure 10: Compressed Row Format (CRS)

This figure is an example of the compressed row storage format. This format stores the value, column, and row pointer of the non-zero entries in the matrix. The row pointer tells the user on which entries in the value vector are stored in the next row from the previous entry.

Because the compressed row storage is similar to the compressed column storage, but stored by row rather than column, the total number of values required to store a compressed row matrix is equal to:

$$CRSMatrixMemory = 2 \times (\#Nonzeros) + (\#ofRows) + 1$$

#### 2.2.4 The Length Vector vs. Pointer

An alternate way to use a compressed row or column storage is to use a length vector instead of a pointer vector. The length vector has a size equal to the number of columns in the matrix and stores the number of values in each column (Zhuo & Prasanna, 2005). Below is the original matrix stored in compressed column format using a length vector rather than a pointer. In the case of the length vector, an empty column would be marked by a zero entry.

| Val: | 101 | 110 | 102 | 103 | 104 | 105 | 106 | 107 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

| Row: | 1   | 5   | 1   | 2   | 3   | 5   | 4   | 5   |

| Len: | 2   | 2   | 2   | 1   | 1   |     |     |     |

Figure 11: Compressed Column using Length Vector

This figure shows the Compressed Column format utilizing a Length vector rather than a Pointer. The Length vector tells the user how many Val entries are stored in the current column.

Compression using the length vector is very much the same as the compressed methods using the pointer vector. The only difference is that the length vector is exactly equal to the number of rows or columns while the pointer vector is equal to this value plus one. Therefore, the difference between the two formats is one value.

#### 2.2.5 Compressed Diagonal Storage (CDS)

A third type of compressed format that can be useful for some applications is compressed diagonal storage (CDS). Like the column and row compressed methods, CDS stores values that are in the same diagonal alongside one another in memory. CDS stores multiple vectors, one for each diagonal, with their corresponding diagonal indices. The diagonal indexes are assigned with diagonal zero always starting at the upper left-hand cell of the matrix, as shown in Figure 12.

Figure 12: Diagonal Assignments in Compressed Diagonal Storage

This figure is an example of Compressed Diagonal Storage. In this type of storage, the values that are located diagonally from upper-left to lower-right will be stored next to each other in memory. This type of compression format becomes especially effective when storing banded matrices.

The original full matrix, shown in Figure 7, would be stored as a vector of length four and a matrix with four rows and five columns. The vector contains the diagonal numbers and tells the user the diagonal indices of the values stored in the matrix. Because non-zero values exist on diagonals 1, 0, -2, and -4 in the matrix above, the diagonal index vector contains those diagonal indices:

| Diag: | 1 | 0 | -2 | -4 |

|-------|---|---|----|----|

| Diag. | ' | U |    | -4 |

Figure 13: Diagonal Vector Example

An example of what the diagonal vector for the original matrix stored in CDS would look like. This vector tells the user which diagonals the values in the diagonal values matrix below are located in.

The matrix that is stored along with this vector contains the values from each diagonal in a row of the matrix. For this matrix, the storage matrix is shown in Figure 14.

| 0   | 102 | 0   | 0   | 0   |

|-----|-----|-----|-----|-----|

| 101 | 103 | 104 | 106 | 107 |

| 0   | 0   | 105 | 0   | 0   |

| 110 | 0   | 0   | 0   | 0   |

Figure 14: Diagonal Values

This figure shows the diagonal values matrix for the Compressed Diagonal Storage of the original matrix. It would be stored in conjunction with the Diag. vector shown previously. In this case, the elements in row one are from diagonal one. The elements in row two are from diagonal zero. These diagonal indices are found in the Diag. vector.

The original matrix can be reassembled from the storage matrix and its corresponding diagonal vector. The values in row one of the storage matrix belong in diagonal one of the original. Because the first entry of diagonal one of the original matrix is outside its boundaries, the first entry is zero. Diagonal -4 only has one entry on the original matrix thus every entry but its first is filled in with a zero. (Dongarra, 2007)

The CDS format is most useful for banded matrices. Banded matrices are matrices with most of the entries stored diagonally across the matrix. They have a high frequency of non-zero entries along their diagonals. In the case of a banded matrix, CDS storage can become smaller than a row or column compressed format. There is no general formula for the number of values stored by the CDS format because it is so highly dependent on the structure of the matrix and the number and location of bands.

Figure 15: Banded Matrix Example

The image above is an example of what is called a banded matrix. Non-zero entries are shown as a non-white color. The majority of non-zero values are concentrated along diagonals from the upper left-hand side of the matrix to the lower right-hand corner. (Davis, 2007)

For most other cases, however, in which the original matrix is not banded, the diagonal method can actually become larger than the original matrix. This increase in size is due to the fact that the diagonals often overrun the boundaries of the matrix and are filled in with zeros where appropriate.

# 2.2.6 Storage Size Comparison

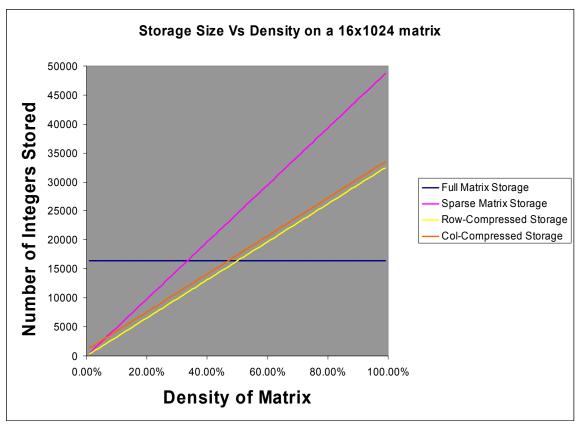

A plot has been generated to show the number of values in various matrix storage methods versus the density of the matrices. The methods that were compared were the full matrix storage method, the basic sparse matrix storage method, the row-compressed, and the column-compressed methods.

Figure 16: Storage Method Sizes on a Square Matrix

This figure shows the size of each storage method versus the density of the matrix. Because full matrix storage stores all values, regardless of their value, its size is consistent throughout the entire range of densities. For a basic sparse matrix storage method, it is smaller than a full matrix method for densities of less than 33%. The two compressed methods are smaller than full matrix storage up to almost 50% density. In this figure, row-compressed is smaller than column-compressed because its size is dependant on the number of rows while column-compressed depends on the number of columns.

It is shown in Figure 16; the sparse and compressed sparse matrix formats can be much smaller than a full matrix storage method for sparsely populated matrices. Once the matrix becomes more than half full of non-zero entries, the full matrix representation becomes the smallest method. In Figure 16 the row-compressed method is much smaller than the column compressed method. This size difference is due to the fact that the matrix has many fewer rows than columns. If the matrix were a square matrix, the sizes of the compressed methods would be exactly equal.

#### 2.2.7 Matrix Multiplication

As stated previously, matrix multiplication is a key kernel in knowledge processing and the analysis of graphs. The general format for multiplying two matrices is shown below where matrix A times matrix B is equal to matrix C. An important fact to note is the number of columns in matrix A must equal the number of rows in matrix B for the multiplication to be possible. The final matrix will have the same number of rows as matrix A and the same number of columns as matrix B. Therefore, a matrix with dimensions  $(X \times Y)$  multiplied by a matrix with dimensions  $(Y \times Z)$  will give a resultant matrix with dimensions  $(X \times Z)$ . Figure 17 shows the general form of a matrix multiplication:

#### Where:

$C_{11}=A_{11}B_{11}+A_{12}B_{21}+...A_{1Y}B_{Y1}$   $C_{12}=A_{11}B_{12}+A_{12}B_{22}+...A_{1Y}B_{Y2}$   $C_{X1}=A_{X1}B_{11}+A_{X2}B_{21}+...A_{XY}B_{Y1}$ and  $C_{X7}=A_{X1}B_{17}+A_{X2}B_{27}+...A_{XY}B_{Y7}$

Figure 17: General form for Matrix Multiplication

This figure shows the general form for performing the multiplication of two matrices. In this case, A is an X by Y matrix, B is a Y by Z matrix and the resultant, C is an X by Z matrix. (Weisstein, 2006)

The value in any cell of matrix C is equal to a multiplication of a row from matrix A and a column from matrix B. This vector by vector multiplication is also known as computing the dot product of two vectors. The value of a dot product is a single number that is the sum of the products of corresponding values from each vector. Figure 18 shows the general form for computing a dot product is as follows:

$$\begin{bmatrix} A_1 & A_2 & \cdots & A_x \end{bmatrix} \bullet \begin{bmatrix} B_1 \\ B_2 \\ \vdots \\ B_x \end{bmatrix} = \begin{bmatrix} A_1 B_1 + A_2 B_2 + \cdots + A_x B_x \end{bmatrix} = \begin{bmatrix} C \end{bmatrix}$$

Figure 18: General Form for Computing a Dot Product

This figure shows the general form to compute a dot product. The row vector A and the column vector B dotted together give the answer, C. C is the sum of the products of corresponding values from each vector.

Therefore, to compute the product of matrix A times matrix B, an algorithm must cycle through the rows of A and the columns of B, computing the dot product of each row and each column.

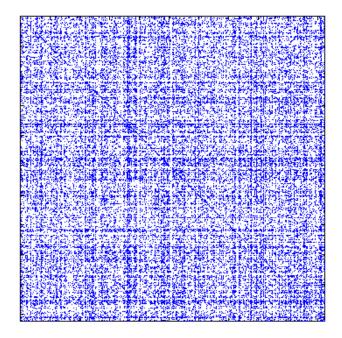

#### 2.3 Matrices of Interest

The matrices with which algorithm development will be based upon are sparsely populated adjacency matrices with density, or frequency of non-zero entries, of about 1%. These matrices can be generated by the RMAT function in MATLAB. RMAT is a MATLAB function designed to generate random adjacency matrices of different sizes and densities for testing. RMAT does not generate the same matrix every time it is given the same parameters. It was developed at MIT Lincoln Laboratory by Dr. Jeremy Kepner of group 102. RMAT generates matrices with a power-law distribution, meaning that there are few vertices on the graph with very high importance (high betweenness

centrality) and numerous vertices with low importance. The range of edge values also follows a power-law distribution, meaning there are many weak edges, signified by an entry of one in a cell, and few strong edges which are signified by larger integers. RMAT is capable of generating two types of matrices. The first will be referred to as a structured RMAT matrix; the second will be referred to as a randomized RMAT matrix.

The structured RMAT matrix is an adjacency matrix with properties similar to those found in a real world adjacency matrix. The structure is based on the idea of Kronecker Graphs (for more information on Kronecker Graphs see Leskovec & Faloutsos, 2007) and exhibits an interesting matrix structure to researchers at Lincoln Laboratory. Though the mathematical complexities of this matrix structure are beyond the scope of this project, it is important to understand its structure.

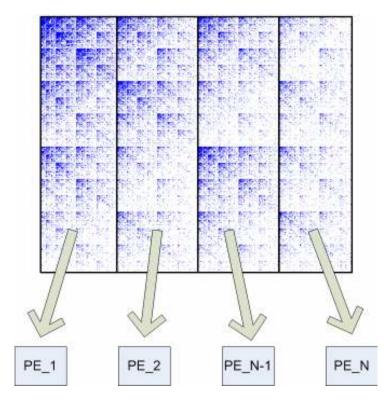

**Figure 19: Structured RMAT Matrix**

This figure shows a  $1024 \times 1024$  structured adjacency matrix generated by the RMAT function with density of 5%. This is the first type of structure used in the testing of the multiplication and parallelization algorithms. Non-zero entries are shown as blue dots in the figure.

The structured RMAT matrix shown in Figure 19 has a block like structure which is repeated throughout the matrix. The more dense rows and columns are found towards

the left and upper parts of the matrix. This same structure is repeated in smaller and smaller blocks throughout the entire structure. Because of this block structure, dense rows and columns are repeated at constant intervals throughout the matrix.

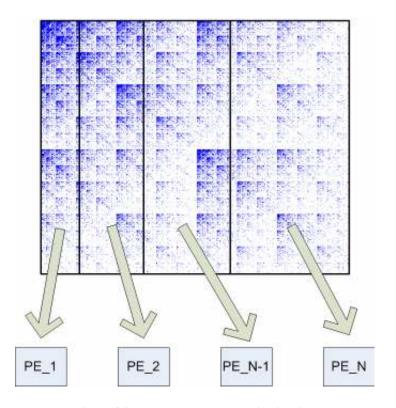

The randomized RMAT matrix contains the same type of data as a structured RMAT matrix but the vertices have been randomized. This randomization means that instead of being grouped together, the dense rows and columns are randomly and uniformly distributed throughout the matrix. This same randomization process could be applied to any adjacency matrix. It is as simple as reordering the vertex labels in the rows and columns.

Figure 20: Randomized RMAT Matrix

This figure shows a 1024 x 1024 randomized adjacency matrix generated by the RMAT function with density of 5%. This is the second type of structure used in the testing of the multiplication and parallelization algorithms. Non-zero entries are shown as blue dots in the figure

Figure 20 shows a Randomized RMAT matrix. The non-zero entries on the randomized version are much more evenly distributed throughout the matrix than in the case of the Structured RMAT matrix. It is important to note that although the RMAT matrices look

as though they might be symmetric across the major diagonal, they are unidirectional adjacency matrices and not symmetric.

# 2.4 Field Programmable Gate Arrays (FPGAs)

A final deliverable of this project was to parallelize the optimized sparse matrix multiply algorithm on a field-programmable gate array (FPGA). An FPGA is a type of programmable logic device (PLD) with which an engineer can develop almost any logic circuit s/he wishes, or even multiple copies of the same logic circuit. Using multiple copies of a specialized logic circuit enables an FPGA to perform operations simultaneously, thus processing data in parallel. Implementing parallel processing on a single chip gives a large advantage over an array of conventional microprocessors which is slowed by inefficient communication. Inside an FPGA, separate circuits have high connectivity and can transmit data between each other quickly and efficiently.

Research has shown that the implementation of an FPGA with multiple interconnected copies of the same circuit can parallelize operations and achieve "almost supercomputer-class performance" at a "tiny fraction of the cost of more general-purpose supercomputing hardware" (Pellerin, and Thibault, 2005). FPGAs enable developers to design a circuit which performs exactly the computations they need it to and nothing more. By parallelizing and optimizing for one algorithm, a device can be made much more capable to perform its job; however, this optimization simultaneously makes it less versatile:

Parallel architectures can be more powerful, but are less general. A special-purpose circuit can always outperform a microprocessor-based implementation for a small class of problems ....The very specialization which provides this parallelism also necessarily limits the range of its application.(Oldfield & Dorf, 1995)

FPGA's are often a good choice for the development of a complicated yet dedicated hardware circuit. Once a system becomes massively produced, implementing it on an Application Specific Integrated Circuit (ASIC) is usually more economical and can provide another level of optimization above the FPGA.

Embedded system developers constantly strive to achieve the same capabilities using smaller and more power-efficient packages. The low power consumption and small package size is another reason FPGAs are often utilized in embedded system engineering. Figure 21 shows the efficiencies of a field-programmable gate array versus those of a programmable processor or ASIC system.

Figure 21: Performance Density and Efficiency between device families

This plot shows a performance comparison between microprocessors, FPGAs, and VLSI circuits in GigaOperations per Second (GOPS) per volume (Liter) and power consumption (Watt). (Graph Courtesy of

MIT Lincoln Laboratory)

As shown in Figure 21, FPGAs can perform more operations per second than programmable processors while using less space and consuming less power. It is important to realize there is a cost factor missing from this chart. Much more time and

money will be spent to develop an FPGA solution to a problem rather than using a programmable processor. Even more resources will be needed to develop a Very Large Scale Integration (VLSI) implementation such as an ASIC. There is a direct relation between time, cost, level of development, and performance. For this project, achieving the performance of an FPGA implementation is a reasonable target for the available time and resources.

#### 2.4.1 FPGA Architecture

An FPGA is a reprogrammable semiconductor device which is becoming very commonly used in the development of embedded systems. Its ability to be reprogrammed in the field is unlike other programmable logic devices which, once configured, cannot be changed. On an FPGA, an engineer can implement almost any type of logic circuit. These logic circuits are implemented by using a hardware definition language (HDL) like Verilog or VHDL. The range of implementation can range from a simple logic gate such as an OR or an AND gate to extremely complex circuits. Figure 22 shows a diagram of the basic structure inside an FPGA.

Figure 22: FPGA Architecture

This figure shows the inner architecture of a basic FPGA. The blue blocks in the middle are Configurable Logic Blocks (CLBs), while the red blocks on the outer edges are I/O blocks. Between the blocks, in yellow, are the row and column programmable interconnects. (Floyd, 2006)

The inside of an FPGA is mainly comprised of a grid of programmable logic blocks and interconnections. By combining a number of these blocks and connecting them through the grid of programmable interconnects, the FPGA can take on the role of almost any logic circuit. A single programmable logic block consists of a Look-Up Table (LUT), a D Flip-Flop connected to the main clock of the device, and output logic (Computer Engineering Research Group, University of Toronto, 2007). Figure 23 shows the basic internal structure of a programmable logic block.

Figure 23: FPGA Logic Block

This figure shows the inner workings of a Configurable Logic Block. It consists of a Look-Up Table (LUT), a D flip flop and output logic. (Cofer & Harding, 2006)

The I/O blocks on an FPGA are also configured by the user. These blocks control how and where information is transferred in and out of the FPGA (which pin or pins the inputs are read through and the outputs are sent through). Modern FPGAs often have other hardware devices embedded in them such as block RAM, Universal Asynchronous Receiver-Transmitters (UARTs) or even PowerPC processors.

Many Intellectual Property (IP) or soft-cores can be implemented on an FPGA as well. IP cores are files written in a Hardware Definition Language (HDL) which can be obtained through various sources and perform a specific application. An engineer would have to load the HDL file onto the FPGA. There is a large variety of IP or Soft-cores available that perform commonly used circuits. A quick internet search can find

downloadable IP cores for encryptions, Fast Fourier Transforms (FFTs), USB controllers or even microprocessors. This high degree of versatility and performance is why FPGAs are often a good choice for embedded systems engineers.

#### 2.4.2 Soft-Core Microprocessors

Embedding a soft-core processor can reduce the time and effort involved in designing an embedded system with an FPGA. A soft-core processor is an entire microprocessor implemented in the hardware of an FPGA through an HDL file. These processors can run software, just like the processor in the average desktop computer. When implementing an algorithm on an FPGA, it is often most cost effective to implement only the most time-intensive parts of the algorithm in gate-level hardware, while leaving the less time consuming parts to be completed by software run by a soft-core processor. Soft-core microprocessors allow an engineer to develop a system on an FPGA which is a hybrid between hardware and software (Eskowitz et al., 2004). With the option of a soft-core software implementation, an engineer can decide which parts of their algorithm will benefit most from a gate-level hardware circuit and which ones are more efficiently performed by software.

A soft-core microprocessor can also increase a company's ability for rapid development and deployment of systems by allowing production and development times to overlap. An original design of an FPGA could perform most of its functions by a soft-core processor embedded on the FPGA. The company could begin mass production of a working product while its engineers were still developing and optimizing the design's logic circuits. Later, due to the FPGA's field programmability, the company could update its systems with more gate-level hardware implementations. This process could

continue until, eventually, the entire design was optimized through gate-level hardware implementations.

Perhaps the most commonly used soft-core microprocessor is the Xilinx Microblaze. The Microblaze is a soft-core processor designed for use on Xilinx's Spartan and Virtex lines of FPGAs. It is a 32 bit processor using RISC architecture which is capable of running at 100 MHz on the Virtex-II Pro FPGA. The Microblaze contains many features of a typical microprocessor including: 32 registers, an ALU, a multiplier, a divider, a barrel shifter, interrupts, UART, and an off-chip memory interface. (Xilinx Microprocessor Controller and Peripheral, 2007) A diagram of the Microblaze architecture is shown in Figure 24.

Figure 24: Microblaze Architecture

This figure shows the typical layout and architecture of the Xilinx Microblaze soft-core processor. (Rosinger, 2004)

The Microblaze is truly designed for use inside an FPGA. Since soft-cores run at much slower clock speeds than a hard-core processor, the primary reason for using a soft-core on an FPGA would be to use it in conjunction with other IP that can speed up the algorithm overall. Therefore, the Microblaze is designed with a port for high speed connection to specialized IP circuits called the Fast Simplex Link (FSL). For many designs, utilizing specialized IP cores can increase the overall efficiency of an algorithm. Figure 25 displays an example of the same algorithm performed by both software and hardware.

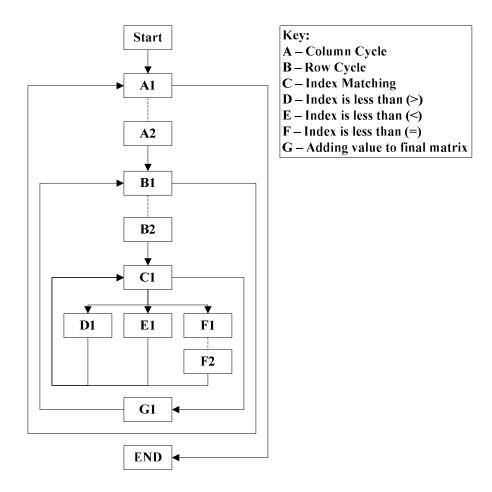

Figure 25: Software Algorithm vs. Hardware

This figure shows the same process performed by a microprocessor in software on the left and by a hardware circuit on the right. A, B, C, D, E, F, and G are assumed to be numeric values stored in the memory of the system. (Rosinger, 2004)

The hardware solution of this algorithm requires two clock cycles while the software requires 12. A specialized logic circuit is often the best choice for speeding up complicated functions in an FPGA design and often provides motivation for a soft-core processor to outsource some of its more time consuming jobs to hardware.

## 2.4.3 PowerPC processor

Another option to a developer using the Xilinx Virtex-II Pro FPGA is to utilize the embedded hard-core PowerPC microprocessor. This is a more powerful processor than the Microblaze. It consists of a 32 bit RISC architecture. Connecting IP circuits to

the PowerPC is different than in the Microblaze. Any IP cores utilized by the PowerPC are connected through the On-Chip Peripheral Bus rather than the Fast Simplex Link.

Figure 26: PowerPC Architecture

This figure shows an example of an embedded system utilizing an embedded PowerPC microprocessor on a Xilinx FPGA. (Xilinx PowerPC 405 Processor, 2007)

The embedded PowerPC will not be used in our hardware implementation, but it is available for future use.

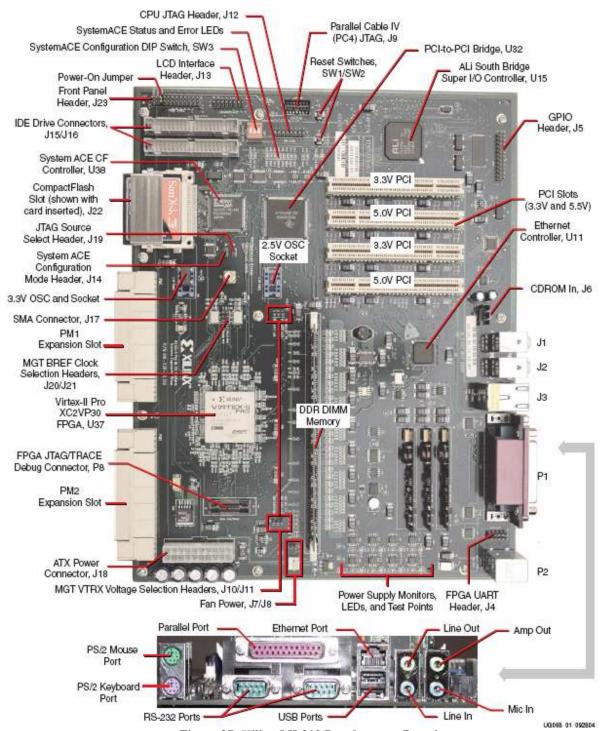

# 2.5 ML310 Development Board

The FPGA board that the final design of this project was implemented on is Xilinx's ML310 development board. The ML310 is a board meant for rapid system prototyping of embedded systems using the Virtex-II Pro FPGA. The ML310 comes standard with a Xilinx Virtex-II Pro XC2VP30 chip. It also comes with a myriad of peripheral devices such as USB ports, parallel and serial connections, IDE connections for hard drives or CD ROMs, an LCD interface, LEDs, a UART connector to send out

data to a terminal, an Ethernet port, audio in and out connections, a 512 MB CompactFlash card, 256 MB of DDR RAM, PS/2 mouse and keyboard ports, 5.0V and 3.3V PCI slots. Shown in Figure 27 is a picture of the ML310.

For this project, we only used the Virtex-II Pro itself as well as the UART terminal to print data to the computer screens. It was programmed through the JTAG cable, J9. The FPGA is shown as U37 in the diagram while its UART connector is shown as J4.

Figure 27: Xilinx ML310 Development Board

This figure is a diagram showing the Xilinx ML310 development board. The board is used for rapid embedded system prototyping and comes with many useable peripherals. The Virtex-II Pro FPGA is shown above as U37. The UART port we used to print text to our screen is marked J4 while the JTAG connector used to program the Virtex is marked at the top as J9. (ML310 User Guide)

#### 2.6 Xilinx Virtex-II Pro XC2VP30

The Virtex-II Pro XC2VP30 is a high performance FPGA platform developed by Xilinx Inc., a leading FPGA manufacturer. The Virtex-II Pro line of FPGAs is targeted towards communication and DSP applications and is manufactured using a 0.13 µm CMOS nine-layer copper process. The XC2VP30 model contains 30,816 logic cells, each consisting of a 4-input look-up table, a flip-flop, and carry logic. It also contains 136 18x18 bit multipliers and 136 blocks of RAM of 2.25 KB each; making the total RAM available 306 KB.

Furthermore, it contains eight RocketIO transceiver blocks which are responsible for high speed connectivity and conversions between parallel and serial interfaces. Two hard-core PowerPC microprocessors (400MHz) are also embedded on the XC2VP30. The Microblaze soft-core processor can also be implemented in the logic of the XC2VP30. An implementation of the Microblaze on this FPGA can run at a clock speed of 100MHz. (Virtex-II Pro Data Sheet)

# 3 Algorithm Performance Analysis

There are multiple techniques an engineering team could pursue when building and parallelizing an optimal sparse matrix multiplication algorithm. Because of the many options and the inherent memory constraints on an FPGA, we sought an algorithm which would both perform multiplication quickly and efficiently while keeping memory requirements to a minimum. The methodology section discusses the processes of both optimizing a multiplication algorithm and implementing the algorithm on an FPGA.

When developing the FPGA algorithm, multiple methods for the storage and multiplication of two sparse matrices were simulated in MATLAB to find a technique that both compressed the matrices effectively and performed the multiplication at a higher efficiency than a full matrix multiplication. After determining the formats and algorithm for optimized multiplication, load distribution methods were simulated to find one that efficiently parallelized the multiplication between multiple processing elements.

# 3.1 Optimized Matrix Multiplication Algorithm

To multiply a set of two matrices, a certain number of calculations must be performed regardless of storage type and indexing method. These calculations are the non-zero arithmetic operations; multiplying and summing the corresponding values in a row of matrix A and a column of matrix B. Each type of matrix multiplication has some overhead involved in performing these non-zero calculations. In the case of full matrix multiplication, the overhead takes the form of multiple zero operations (multiplying by a zero or adding zero) that are not important to product. In the case of sparse matrix multiplications, the overhead takes the form of more complicated indexing and searching

operations which find the intersecting values to be multiplied. The most efficient multiplication method will perform these non-zero operations with the least amount of overhead.

To determine the most efficient method to store and multiply two sparse matrices for multiplication, storage methods from those discussed in the background were tested to find one with high multiplicational efficiency and maximum compression of the matrices. The definition of efficiency we used was the number of non-zero operations divided by the maximum possible number of non-zero operations performed by the processor. The target matrices were adjacency matrices with less than 5% density. Four separate storage methods were tested to find a combination which organized the matrices optimally for multiplication.

Four different multiplication algorithms were tested for efficiency in MATLAB. Because MATLAB itself utilizes C functions to perform some of its calculations faster, none of the test functions ran faster than MATLAB's embedded matrix multiplication functions. The tests sought to test different multiplication methods against each other on the same level of development. MATLAB served as the common platform upon which all algorithms were built. Testing these algorithms in MATLAB provided an estimate of their relative efficiencies in other programming languages such as C or even hardware definition languages like VHDL.

During the testing procedures, the efficiency of each algorithm was calculated. To measure efficiency, two RMAT test matrices with dimensions 1024x1024 were generated for each density tested (1% to 99%). The total number of non-zero calculations (multiplications and additions) to multiply the two test matrices was counted

using a specialized function we developed. The multiplication was timed, and the number of calculations was divided by the total time. The performance of each algorithm, in non-zero operations per second, was divided by the clock speed of the processor, giving the efficiency of the algorithm. A plot was generated showing the efficiency of each matrix multiplication in non-zero operations per second.

These tests were run on machines with the same hardware specifications to ensure their consistency. During testing, the machines were monitored to ensure there was no additional CPU load unrelated to testing. The machines were Quad core 3.066 GHz processors with 2.5 Gigabytes of RAM each; part of the MIT-Lincoln Laboratory group 102 cluster. Five instances of each matrix multiplication test were run and averaged. The test's goal was to determine which multiplication method performed most efficiently on the target matrices and to determine the range of densities for which these methods performed at higher efficiency than a full matrix multiplication. The plot made strong suggestions as to which algorithm worked with the least overhead.

### 3.1.1 Full Matrix Multiplication

To multiply two full matrices in a full matrix storage format, a function was developed in MATLAB so each sparse method could be compared against it. Because all the RMAT matrices were originally stored in a full format, tests could easily be run on these matrices before converting them to various sparse formats to be tested. A full matrix multiplication stores and multiplies all entries inside the matrices regardless of whether they're zero or not. Building our own full matrix multiplication function allowed our plots to show the benefits of multiplication in the sparse domain versus the full domain.

MATLAB does have its own full matrix times full matrix function built in (matrixA\*matrixB), but MATLAB's function utilizes C-code which operates on a much lower level than MATLAB and is much faster. MATLAB's function would not be comparable to the sparse matrix multiplication methods which were tested. We therefore built our own function in MATLAB which would be comparable.

#### 3.1.1.1 Full Matrix Multiplication Algorithm

The following is pseudocode showing the full matrix multiplication algorithm which was tested:

```

for (x=1; x<matrixA.row; x++) //<- cycle for every row in A

for (y=1; y<matrixB.column; y++)) //<- cycle by column in B

Compute dot product of Row x in A and Column y in B

Write result to entry (x,y) in resultant matrix

end

end</pre>

```

This process cycles through the rows of A and the columns of B performing vector by vector multiplication. The dot product of each row by each column is computed and the answer is written to the corresponding cell in matrix C. The actual MATLAB code used for the simulation can be found in Appendix A.

### 3.1.2 Sparse Matrix Multiplication