## Video/Image Processing on FPGA

by

Jin Zhao

A Thesis

Submitted to the Faculty

of the

#### WORCESTER POLYTECHNIC INSTITUTE

In partial fulfillment of the requirements for the

Degree of Master of Science

in

Electrical and Computer Engineering

by

April 2015

APPROVED:

Professor Xinming Huang, Major Thesis Advisor

Professor Lifeng Lai

Professor Emmanuel O. Agu

#### Abstract

Video/Image processing is a fundamental issue in computer science. It is widely used for a broad range of applications, such as weather prediction, computerized tomography (CT), artificial intelligence (AI), and etc. Video-based advanced driver assistance system (ADAS) attracts great attention in recent years, which aims at helping drivers to become more concentrated when driving and giving proper warnings if any danger is insight. Typical ADAS includes lane departure warning, traffic sign detection, pedestrian detection, and etc. Both basic and advanced video/image processing technologies are deployed in video-based driver assistance system. The key requirements of driver assistance system are rapid processing time and low power consumption. We consider Field Programmable Gate Array (FPGA) as the most appropriate embedded platform for ADAS. Owing to the parallel architecture, an FPGA is able to perform high-speed video processing such that it could issue warnings timely and provide drivers longer time to response. Besides, the cost and power consumption of modern FPGAs, particular small size FPGAs, are considerably efficient. Compared to the CPU implementation, the FPGA video/image processing achieves about tens of times speedup for video-based driver assistance system and other applications.

#### Acknowledgements

I would like to sincerely express my gratitude to my advisor, Professor Xinming Huang. He offered me the opportunity to study and develop myself in Worcester Polytechnic Institute, guided me in the research projects and mentored me in my life.

Thanks to Sichao Zhu for his creative and helpful work in the traffic sign detection project. Thanks to Bingqian Xie for her ideas and experiments in the lane departure warning system project. Thanks to Boyang Li for helping me learn how to build basic video/image processing block using Mathworks tools.

Thanks to The Mathworks. Inc for their generously supporting our research, financially and professionally.

Thanks to all my lovely friends and my family for their help in the past years. They always encourage me and give me confidence to overcome all the problems.

# Contents

| 1        | Intr | oducti | on                           | 1  |

|----------|------|--------|------------------------------|----|

| <b>2</b> | Bas  | ic Vid | eo/Image Processing          | 3  |

|          | 2.1  | Digita | l Image/Video Fundamentals   | 3  |

|          | 2.2  | Mathw  | vorks HDL Coder Introduction | 5  |

|          | 2.3  | Color  | Correction                   | 7  |

|          |      | 2.3.1  | Introduction                 | 7  |

|          |      | 2.3.2  | Simulink Implementation      | 8  |

|          |      | 2.3.3  | FPGA Implementation          | 11 |

|          | 2.4  | RGB2   | YUV                          | 15 |

|          |      | 2.4.1  | Introduction                 | 15 |

|          |      | 2.4.2  | Simulink Implementation      | 17 |

|          |      | 2.4.3  | FPGA Implementation          | 18 |

|          | 2.5  | Gamm   | na Correction                | 19 |

|          |      | 2.5.1  | Introduction                 | 19 |

|          |      | 2.5.2  | Simulink Implementation      | 21 |

|          |      | 2.5.3  | FPGA Implementation          | 22 |

|          | 2.6  | 2D FI  | R Filter                     | 23 |

|          |      | 2.6.1  | Introduction                 | 23 |

|   |      | 2.6.2   | Simulink Implementation              | 26 |

|---|------|---------|--------------------------------------|----|

|   |      | 2.6.3   | FPGA Implementation                  | 28 |

|   | 2.7  | Media   | n Filter                             | 29 |

|   |      | 2.7.1   | Introduction                         | 29 |

|   |      | 2.7.2   | Simulink Implementation              | 30 |

|   |      | 2.7.3   | FPGA Implementation                  | 33 |

|   | 2.8  | Sobel 1 | Filter                               | 34 |

|   |      | 2.8.1   | Introduction                         | 34 |

|   |      | 2.8.2   | Simulink Implementation              | 35 |

|   |      | 2.8.3   | FPGA Implementation                  | 36 |

|   | 2.9  | Grayso  | cale to Binary Image                 | 37 |

|   |      | 2.9.1   | Introduction                         | 37 |

|   |      | 2.9.2   | Simulink Implementation              | 39 |

|   |      | 2.9.3   | FPGA Implementation                  | 41 |

|   | 2.10 | Binary  | /Morphological Image Processing      | 41 |

|   |      | 2.10.1  | Introduction                         | 41 |

|   |      | 2.10.2  | Simulink Implementation              | 43 |

|   |      | 2.10.3  | FPGA Implementation                  | 44 |

|   | 2.11 | Summa   | ary                                  | 45 |

| 3 | Δdv  | anced   | Video/Image Processing               | 46 |

| J |      |         |                                      |    |

|   | 3.1  |         | Departure warning system             | 46 |

|   |      | 3.1.1   | Introduction                         | 46 |

|   |      | 3.1.2   | Approaches to Lane Departure Warning | 47 |

|   |      | 3.1.3   | Hardware Implementation              | 52 |

|   |      | 3.1.4   | Experimental Results                 | 56 |

|   | 3.2  | Traffic | Sign Detection System Using SURF     | 58 |

| <b>4</b> | Con | clusio  | ns        |                                                      | 80 |

|----------|-----|---------|-----------|------------------------------------------------------|----|

|          | 3.4 | Summ    | ary       |                                                      | 79 |

|          |     | 3.3.3   | Results . |                                                      | 78 |

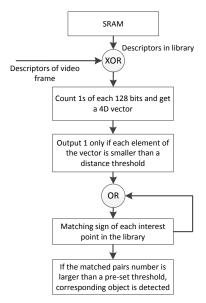

|          |     |         | 3.3.2.5   | Descriptor Matching Module                           | 77 |

|          |     |         | 3.3.2.4   | FREAK Descriptor                                     | 76 |

|          |     |         | 3.3.2.3   | Memory Management Unit                               | 75 |

|          |     |         | 3.3.2.2   | Integral Image Generator and Interest Point Detector | 74 |

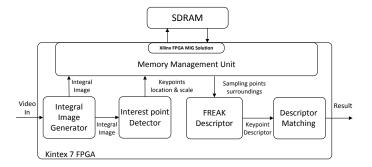

|          |     |         | 3.3.2.1   | Overall System Architecture                          | 73 |

|          |     | 3.3.2   | Hardwar   | e Implementation                                     | 73 |

|          |     | 3.3.1   | FREAK     | Descriptor                                           | 72 |

|          | 3.3 | Traffic | Sign Det  | ection System Using SURF and FREAK                   | 71 |

|          |     | 3.2.4   | Results . |                                                      | 70 |

|          |     |         | 3.2.3.6   | Descriptor Comparator                                | 69 |

|          |     |         | 3.2.3.5   | Interest point descriptor                            | 68 |

|          |     |         | 3.2.3.4   | Memory management unit                               | 67 |

|          |     |         | 3.2.3.3   | Interest points detector                             | 64 |

|          |     |         | 3.2.3.2   | Integral image generation                            | 63 |

|          |     |         | 3.2.3.1   | Overall system architecture                          | 62 |

|          |     | 3.2.3   | FPGA I    | mplementation of SURF                                | 61 |

|          |     | 3.2.2   | SURF A    | lgorithm                                             | 59 |

|          |     | 3.2.1   | Introduc  | tion                                                 | 58 |

# List of Figures

| 1.1  | Xilinx KC705 development kit                                                                    | 2  |

|------|-------------------------------------------------------------------------------------------------|----|

| 2.1  | Video stream timing signals                                                                     | 5  |

| 2.2  | HDL supported Simulink library                                                                  | 6  |

| 2.3  | Illustration of color correction                                                                | 8  |

| 2.4  | Flow chart of color correction system in Simulink                                               | 9  |

| 2.5  | Flow chart of video format conversion block                                                     | 10 |

| 2.6  | Flow chart of serialize block                                                                   | 10 |

| 2.7  | Flow chart of deserialize block                                                                 | 10 |

| 2.8  | Implementation of color correction block in Simulink                                            | 11 |

| 2.9  | Example of color correction in Simulink                                                         | 12 |

| 2.10 | HDL coder workflow advisor (1) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            | 13 |

| 2.11 | HDL coder workflow advisor (2) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 13 |

| 2.12 | HDL coder workflow advisor $(3)$                                                                | 14 |

| 2.13 | HDL coder workflow advisor (4) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                     | 14 |

| 2.14 | HDL coder workflow advisor (5) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                     | 15 |

| 2.15 | Example of color correction on hardware                                                         | 15 |

| 2.16 | Illustration of RGB to YUV conversion                                                           | 16 |

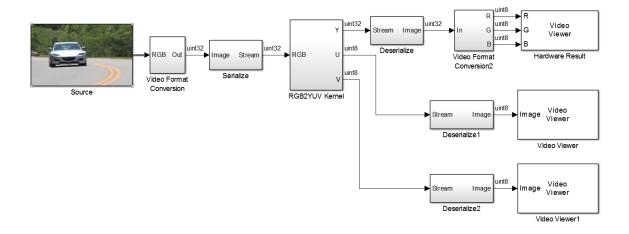

| 2.17 | Flow chart of RGB2YUV Simulink system                                                           | 17 |

| 2.18 | Implementation of RGB2YUV block in Simulink                                                     | 18 |

| 2.19 | Example of RGB2YUV in Simulink                                           | 19 |

|------|--------------------------------------------------------------------------|----|

| 2.20 | Example of RGB2YUV on hardware                                           | 20 |

| 2.21 | Illustration of gamma correction                                         | 21 |

| 2.22 | Flow chart of gamma correction system in Simulink                        | 22 |

| 2.23 | Parameter settings for 1-D Lookup Table                                  | 22 |

| 2.24 | Example of gamma correction in Simulink                                  | 23 |

| 2.25 | Example of gamma correction on hardware                                  | 24 |

| 2.26 | Illustration of 2D FIR filter                                            | 25 |

| 2.27 | Flow chart of 2D FIR filter system in Simulink                           | 26 |

| 2.28 | Flow chart of 2D FIR filter block in Simulink                            | 26 |

| 2.29 | Flow chart of Sobel Kernel block                                         | 27 |

| 2.30 | Architecture of kernel mult block                                        | 27 |

| 2.31 | Example of 2D FIR filter in Simulink                                     | 28 |

| 2.32 | Example of 2D FIR filter on hardware                                     | 28 |

| 2.33 | Illustration of median filter                                            | 30 |

| 2.34 | Flow chart of median filter block in Simulink                            | 31 |

| 2.35 | Flow chart of the median Simulink block                                  | 31 |

| 2.36 | Architecture of the compare block in Simulink $\hdots$                   | 32 |

| 2.37 | Implementation of basic compare block in Simulink $\ldots \ldots \ldots$ | 32 |

| 2.38 | Example of median filter in Simulink                                     | 33 |

| 2.39 | Example of median filter on hardware                                     | 34 |

| 2.40 | Illustration of Sobel filter                                             | 35 |

| 2.41 | Flow chart of Sobel filter block in Simulink                             | 35 |

| 2.42 | Flow chart of the Sobel kernel block in Simulink                         | 36 |

| 2.43 | Flow chart of the x/y directional block in Sobel filter system           | 37 |

| 2.44 | Example of Sobel filter in Simulink                                      | 38 |

| 2.45 | Example of Sobel filter on hardware                                           | 38 |

|------|-------------------------------------------------------------------------------|----|

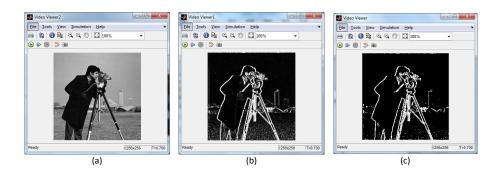

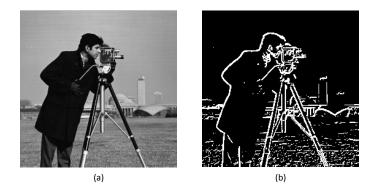

| 2.46 | Illustration of grayscale to binary image conversion                          | 39 |

| 2.47 | Flow chart of the proposed grayscale to binary image conversion systems       | 40 |

| 2.48 | Implementation of the gray2bin block in Simulink                              | 40 |

| 2.49 | Example of grayscale to binary image conversion in Simulink                   | 40 |

| 2.50 | Example of grayscale to binary image conversion on hardware $\ldots$ .        | 41 |

| 2.51 | Illustration of morphological image processing                                | 43 |

| 2.52 | Flow chart of the proposed image dilation block $\ldots \ldots \ldots \ldots$ | 44 |

| 2.53 | Detail of the bit operation block                                             | 44 |

| 2.54 | Example of image dilation in Simulink                                         | 45 |

| 2.55 | Example of image dilation on hardware                                         | 45 |

| 3.1  | Flow chart of the proposed LDW and FCW systems                                | 48 |

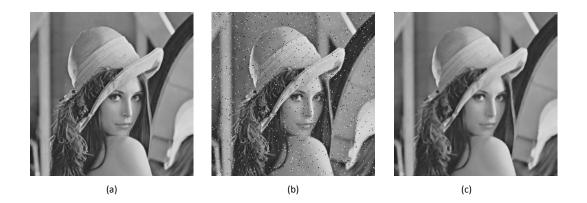

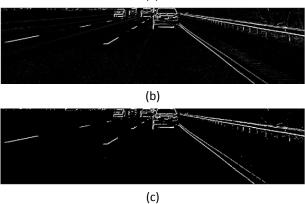

| 3.2  | Illustration of Sobel filter and Otsu's threshold binarization. (a) is        |    |

|      | the original image captured from camera. (b) and (c) are ROI after            |    |

|      | Sobel filtering and binarization, respectively                                | 50 |

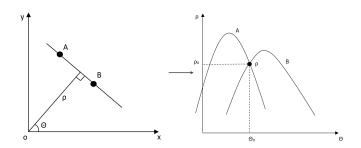

| 3.3  | Hough transform from 2D space to Hough space                                  | 51 |

| 3.4  | Sobel filter architecture                                                     | 53 |

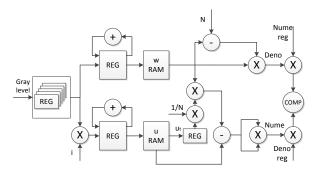

| 3.5  | Datapath for Otsu's threshold calculation                                     | 53 |

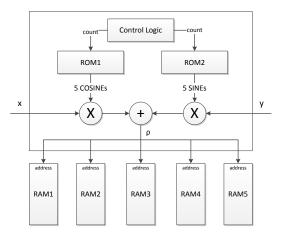

| 3.6  | Hough transform architecture                                                  | 54 |

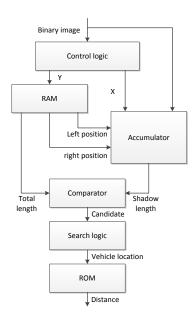

| 3.7  | Flow chart of front vehicle detection                                         | 55 |

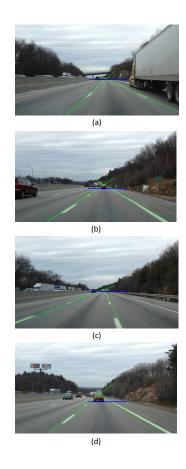

| 3.8  | Results of our LDW and FCW systems                                            | 57 |

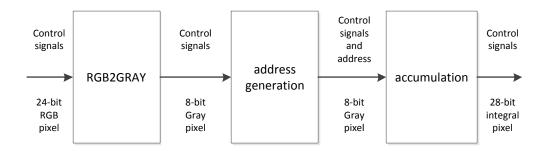

| 3.9  | Overall system block diagram                                                  | 62 |

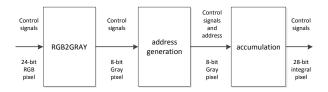

| 3.10 | Integral image generation block diagram                                       | 63 |

| 3.11 | Build_Hessian_Response block diagram                                          | 65 |

| 3.12 | Is_Extreme block diagram                                                      | 66 |

| 3.13 | Interest point descriptor block diagram                                       | 68 |

| 3.14 | Traffic sign detection system              | 71 |

|------|--------------------------------------------|----|

| 3.15 | Illustration of the FREAK sampling pattern | 72 |

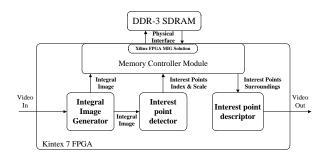

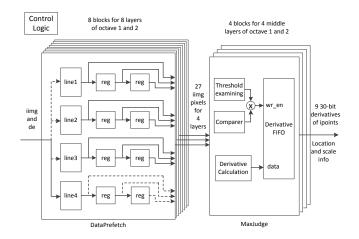

| 3.16 | FPGA design system block diagram           | 74 |

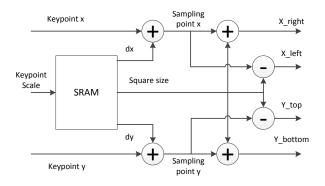

| 3.17 | Integral image address generator.          | 75 |

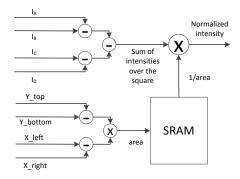

| 3.18 | Normalized intensity calculation.          | 76 |

| 3.19 | Descriptor matching flow chart             | 77 |

| 3.20 | A matching example of STOP sign detection  | 79 |

# List of Tables

| 3.1 | Device utilization summary | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 56 |

|-----|----------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 3.2 | Device utilization summary |   | • |   | • |   |   | • | • | • | • |   | • | • | • | • | • |   | • |   |   | • |   | 71 |

| 3.3 | Device utilization summary |   | • |   | • |   |   | • | • |   |   |   |   | • |   |   |   |   | • |   |   |   |   | 78 |

# Chapter 1

# Introduction

Video/image processing is any form of signal processing for which the input is an video/image, such as a video stream or photograph. Video/image needs to be processed for better display, storage and other special purposes. For example, medical scientists enhance x-ray images and suppress accompanying noises for doctors to make precise diagnosis. Video/image processing also builds solid groundwork for computer vision, video/image compression, machine learning and etc.

In this thesis we focus on real-time video/image processing for advanced driver assistance system (ADAS). Each year millions of traffic accidents occurred around the world cause loss of lives and property. Improving road safety through advanced computing and sensor technologies has drawn lots of interests from researchers and corporations. Video-based driver-assistance system is becoming an indispensable part of smart vehicles. It monitors and interprets the surrounding traffic situation, which greatly improves driving safety. ADAS includes, but is not limited to, lane departure warning, traffic sign detection, pedestrian detection, etc. Unlike general video/image processing on computer, driver assistance system naturally requires rapid video/image processing as well as low power consumption. Alternative solution should be considered for ADAS rather than general purpose CPU.

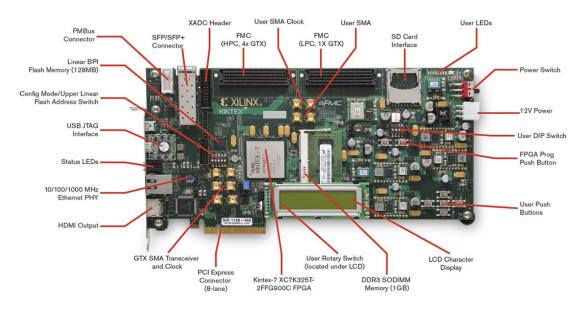

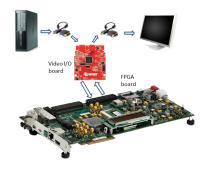

Field Programmable Gate Array (FPGA) is an reconfigurable integrated circuit. Its parallel computational architecture an convenient access to local memories make it the most appropriate platform for driver assistance system. An FPGA is able to perform real-time video processing such that it could issue corresponding warnings to the drivers timely. Besides, the cost and power consumption of modern FPGAs are relatively low, compared to CPU and GPU. In this thesis work, we employ Xilinx KC705 FPGA development kit in figure 1.1 as the hardware platform.

Figure 1.1: Xilinx KC705 development kit

This thesis is organized as follows. Chapter 2 introduces the basic video/image processing blocks and their implementation on FPGA. Chapter 3 presents advanced video/image processing algorithms for driver assistance system and their FPGA implementation. Chapter 4 concludes our achievements and possible improvement in the work of future.

# Chapter 2

# **Basic Video/Image Processing**

This chapter starts with introduction of digital video/image, then presents basic video/image processing blocks. Basic video/image processing is not only broadly used in simple video systems, but could be fundamental and indispensable component in complex video projects. In the thesis, we cover the following video processing functions: color correction, RGB to YUV conversion, gamma correction, median filter, 2D FIR filter, Sobel filter, grayscale to binary conversion and morphological image processing. For every functional block, this thesis introduces basic idea, builds the blocks using Mathworks Simulink and HDL Coder toolbox, and implements hardware block on FPGA.

### 2.1 Digital Image/Video Fundamentals

A digital image could be defined as a two-dimensional function f(x, y), where the x and y are spatial coordinates, and the amplitude of f(x, y) at any location of an image is called the intensity of the image at that point as (2.1).

$$f = \begin{bmatrix} f(1,1) & f(1,2) & \cdots & f(1,n) \\ f(2,1) & f(2,2) & \cdots & f(2,n) \\ \vdots & \vdots & & \vdots \\ f(m,1) & f(m,2) & \cdots & f(m,n) \end{bmatrix}$$

(2.1)

Color image includes color information for each pixel. It could be seen as a combination of individual images of different color channels. The mainly used color system in computer displays are RGB (Red, Green, Blue) space. Other color image representation systems are HSI (Hue, Saturation, Intensity) and YCbCr or YUV.

Grayscale image refers to monochrome image. The only color of each pixel is shade of gray. In fact, a gray color is one in which the red, green and blue components all have equal intensity in RGB space. Hence, it is only necessary to specify a single intensity value for each pixel, as opposed to represent each pixel with three intensities in full color images.

For each color channel of RGB image and grayscale image pixel, the intensity is within a given range between a minimum and maximum value. Often, every pixel intensity is stored using an 8-bit integer giving 256 possible different grades from 0 and 255. The black is 0 and the white is 255, respectively.

Binary image, or black and white image, is a kind of digital image that has only two possible intensity value for every pixel, 1 as white and 0 for black. The object is labeled with foreground color while the rest of the image is with the background color.

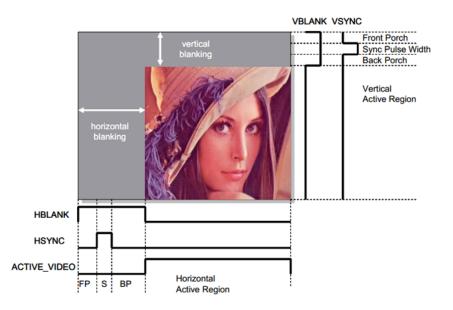

Video stream is a series of successive images. Every video frame consists of active pixels and blanking as figure 2.1. At the end of each line, there is a portion of waveform called horizontal blanking interval. The horizontal sync signal 'hsync' indicates start of the next line. Starting from the top, all the active lines on the

Figure 2.1: Video stream timing signals

display area are scanned in this way. Once the entire active video frame is scanned, there is another portion of waveform called vertical blanking interval. The vertical sync signal 'vsync' indicates start of the new video frame. The time slot of blanking could be used to process video stream, which we can see in the following chapters.

### 2.2 Mathworks HDL Coder Introduction

Matlab/Simulink is a high-level language for scientific and technical computing introduced by Mathworks, Inc. Matlab/Simulink takes matrix as basic data element and makes tremendous matrix operation optimization. Therefore, Matlab is perfect for video/image processing since video/image is naturally matrix.

HDL coder is a Matlab toolbox product. It generates portable, synthesizable Verilog and VHDL code from Mathworks Matlab, Simulink and Stateflow charts. The generated HDL code can be used for FPGA programming or ASIC (Application Specific Integrated Circuit) prototyping and design. HDL Coder provides a workflow advisor that automates the programming of Xilinx and Altera FPGAs. You can control HDL architecture and implementation, highlight critical paths, and generate hardware resource utilization estimates.

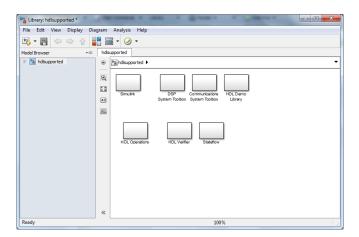

Compared to HDL code generation from Matlab, Simulink provides graphical programming tool for modeling, which is more suitable for building image/video processing blocks. Furthermore, HDL Coder provides traceability between your Simulink model and the generated Verilog and VHDL code. To look up what blocks in Simulink support HDL generation, just type 'hdllib' in Matlab command line. A window will be prompted as in figure 2.2 and customs could find all the HDL friendly Simulink blocks. In order to successfully generate HDL code, every model in the subsystem must be from the hdlsupported library.

Figure 2.2: HDL supported Simulink library

In the following content of this chapter, we will focus on construct basic image/video processing system in Simulink environment using HDL friendly models. The Simulink settings and workflow to generate HDL code are also advised.

### 2.3 Color Correction

#### 2.3.1 Introduction

Color inaccuracies exist commonly during image/video acquisition. An error white balance setting or inappropriate color temperature will produce color errors. In most digital still and video imaging systems, color correction is to alter the overall color of the light. In RGB color space, color image is stored in  $m \times n \times 3$  arrays and each pixel could be represented as 3D vector [R, G, B]'. The color channel correction matrix M is applied to the input images in order to correct color inaccuracies. The correction could be expressed by an multiplication as the following equality in (2.2):

$$\begin{bmatrix} R_{out} \\ G_{out} \\ B_{out} \end{bmatrix} = \begin{bmatrix} M_{11} & M_{12} & M_{13} \\ M_{21} & M_{22} & M_{23} \\ M_{31} & M_{32} & M_{33} \end{bmatrix} \times \begin{bmatrix} R_{in} \\ G_{in} \\ B_{in} \end{bmatrix}$$

(2.2)

or be unfolded in 3 items as

$$R_{out} = M_{11} \times R_{in} + M_{12} \times G_{in} + M_{13} \times B_{in} \tag{2.3}$$

$$G_{out} = M_{21} \times R_{in} + M_{22} \times G_{in} + M_{23} \times B_{in}$$

(2.4)

$$B_{out} = M_{31} \times R_{in} + M_{32} \times G_{in} + M_{33} \times B_{in} \tag{2.5}$$

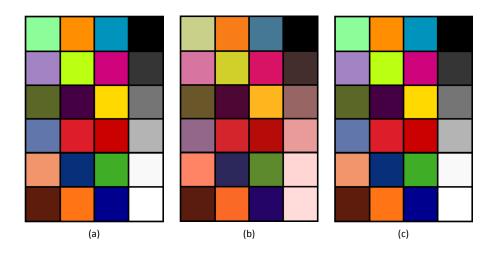

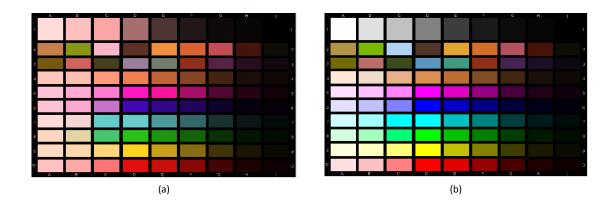

There are several solution to estimate the color correction matrix. For example, Least-squares solution could make the matrix more robust and less influenced by outliers. In the typical workflow, a test chart with known and randomly distributed color patches was captured by a digital camera with "auto" white balance. Comparison of means of the red, green and blue color components in the color patches, original versus captured, reveal the presence of non-linearity. The non-linearity could be described using a  $3 \times 3$  matrix N. In order to accurately display the real color, we employ inverse matrix  $M = N^{-1}$  to offset non-linearity of video camera. For example, In fig. 2.3, (a) is the generated original color patches. (b) is image (a) with color inaccuracies. All the color patches seem containing more red components. The color drifting could be modeled with matrix N and we could correct the incorrect color patches with  $M = N^{-1}$  and get recovered image (c).

Figure 2.3: Illustration of color correction

#### 2.3.2 Simulink Implementation

Simulink, provided by Mathworks, is a graphical block diagram environment for modeling, simulating and analyzing multi-domain dynamic systems. Its interface is a block diagramming tool and a set of block libraries. It supports simulation, verification and automatic code generation.

Simulink is easy-to-use and efficient way to modeling functional algorithms. The

method is pretty straightforward: 1) create a new Simulink model. 2) type 'simulink' in Matlab command line to view all available Simulink library blocks. 3) type 'hdllib' in Matlab command line and open all Simulink block that support HDL code generation. 4) use these HDL friendly block to build up functional blocks hierarchically. You can do so by copying blocks from Simulink library and hdlsupported library to your Simulink model, then simply draw connection lines to link blocks.

Simulink simulates a dynamic system by computing the states of all blocks at a series of time steps over a chosen time span, using information defined by the model. The Simulink library of solvers is divided into two major types: fixed-step and variable-step. They can further be divided within each of these categories as: discrete or continuous, explicit or implicit, one-step or multi-step, and singleorder or variable-order. For all the image processing demos in this thesis, variable step discrete solver is selected. You can go to Simulink  $\rightarrow$  Model Configuration Parameters and select correct solver in the Solver tab of prompted window.

We will elaborate the basic steps and other algorithms in this chapter follow the same guideline. It is important to point out that we just need to translate key processing algorithms to HDL and so other parts of Simulink model, such as source, sink, pre-processing and etc, are not necessarily from hdlsupported library.

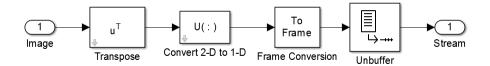

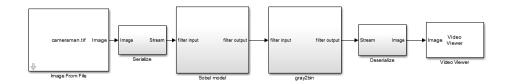

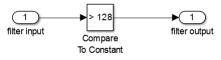

Figure 2.4: Flow chart of color correction system in Simulink

Figure 2.4 gives a big picture of the entire color correction Simulink system. The state flow is as follow: The source block takes image as system input. Video Format Conversion block concatenates three color components to a single bus as in Figure 2.5. Serialize block converts image matrix to pixel-by-pixel stream. Fig. 2.6 illustrates the inner structure of Serialize block. Color correction block is the key componentamong those modules. This block must be purely set up with fundamental blocks from hdlsupported library and hence could be translated to Verilog and VHDL using HDL coder work flow. The subsequent Serialize block as fig. 2.7, inverse of Serialize, convert serial pixel stream back to image matrix. The final block - Video Viewer displays filtering result in Simulink.

Figure 2.5: Flow chart of video format conversion block

Figure 2.6: Flow chart of serialize block

Figure 2.7: Flow chart of deserialize block

Fig. 2.8 illustrates color correction block Simulink implementation. The input bus signal is separated to three color components RGB. The gain blocks implement multiplication. The sum blocks sum up previous multiplication products. Matrix multiplication is implemented using these gain and sum blocks. Finally the corrected color components are concatenated again to a bus signal. The delay blocks inserted in between will be transferred to registers in hardware, which add more clock cycles to leverage higher clock frequency.

Figure 2.8: Implementation of color correction block in Simulink

Fig 2.9 gives the simulation result in Simulink environment. Image (a) is the RGB image with color inaccuracy and image (b) is the corrected image using color correction Simulink system.

#### 2.3.3 FPGA Implementation

After successfully making a functional Simulink project based on HDL friendly basic blocks, we could simply generate HDL code from it using Mathworks HDL coder toolbox.

Figure 2.9: Example of color correction in Simulink

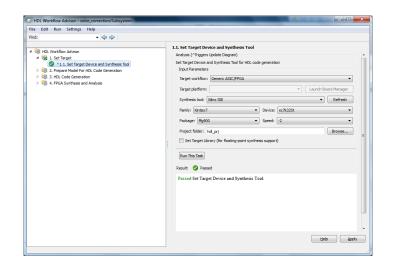

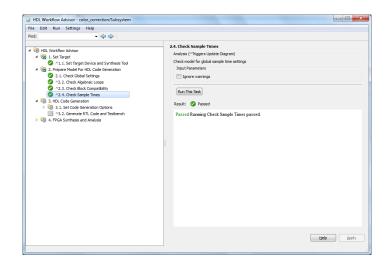

In the first step, right click the HDL friendly subsystem and select HDL Code  $\rightarrow$  HDL Workflow Advisor. In the Set Target  $\rightarrow$  Set Target Device and Synthesis Tool step, for Synthesis tool, select Xilinx ISE and click Run This Task as in fig. 2.10.

In the second step as in fig. 2.12, right-click Prepare Model For HDL Code Generation and select Run All. The HDL Workflow Advisor checks the model for code generation compatibility. You may encounter some incorrect model configuration settings problems for HDL code generation as figure 2.11. To fix the problem, click the Modify All button, or click the hyperlink to launch the Configuration Parameter dialog and manually apply the recommended settings.

In the HDL Code Generation  $\rightarrow$  Set Code Generation Options  $\rightarrow$  Set Basic Options step, select the following options, then click Apply: For Language, select Verilog, Enable Generate traceability report, Enable Generate resource utilization report. For the options available in the Optimization and Coding style tabs, you can use these options to modify the implementation and format of the generated code. This step is showed in fig. 2.13.

Figure 2.10: HDL coder workflow advisor (1)

| ile Edit Run Settings Help<br>Ind:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                        |                                       |               |             |          |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------|---------------|-------------|----------|-------|

| IDL Workfow Advisor       IDL Set Trayet       IDL IS | Input Parameters Ignore warnings Run This Task Result: S Failed Failed Incorrect me click the Modify A | tings for HDL code generation         | link to launc |             |          | ŕ     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                        | Model Settings for H                  |               |             |          |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                        | Settings                              | Current       | Recommended | Severity |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | color_correction                                                                                       |                                       | warning       | error       | warning  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | color_correction                                                                                       |                                       | off           | on          | warning  | -     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | color_correction                                                                                       | Conditional input branch<br>execution | on            | off         | warning  | -     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Action<br>Configure model for ro<br>Modify All<br>Result:                                              | ccommended simulation setting         | 15            |             | elo      | Apply |

Figure 2.11: HDL coder workflow advisor (2)

After Simulink successfully generate HDL code, you have two ways to synthesize and analyze the generated HDL code: 1) copy the HDL code to your HDL project and run the synthesis, translation, mapping and P&R in Xilinx ISE environment manually. 2) run those task in Simulink environment as in fig. 2.14.

In order to validate the entire color correction design, we conduct an experiment on a KC705 FPGA platform. The video streams from a camera or computer are sent to an on-board Kintex-7 FPGA via FMC module. The FPGA performs color

Figure 2.12: HDL coder workflow advisor (3)

| HDL Workflow Advisor - color_correction/Subsystem File Edit Run Settings Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Find: 🔹 🔶 🔿                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>IDL Workflow Advisor</li> <li>IDL 154 Stratt</li> <li>IDL 154 Stratt</li> <li>IDL 154 Tayst Device and Synthesis Tool</li> <li>IDL 154 Tayst Device and Synthesis Tool</li> <li>IDL 204 Globel Stratt</li> <li>IDL 204 Globel St</li></ul> | Concernet RTL Code and Testbenck      Andyser ("Pagners Lighter Daysen")      Generate RTL code and testberch (for the selected adoptem      Generate RTL code      Generate RTL code      Generate RTL code      Generate RTL testberch      Generate RT |

Figure 2.13: HDL coder workflow advisor (4)

correction on every video frame and exports the results to a monitor for display. We delay the video pixel timing signals vsync, hsync and de accordingly to match pixel delay cycles in Simulink.

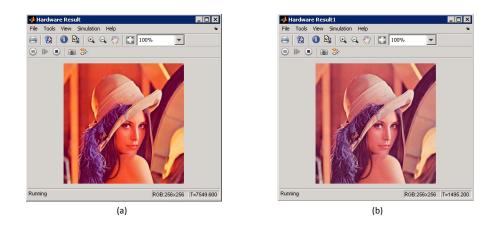

The reported maximum frequency is 228.94 MHz. The resources utilization of the color correction system on FPGA is as follows : 102 slice registers and 246 slice LUTs. Fig. 2.15 illustrates the result of our color correction system on hardware. Image (a) is an video image with color inaccuracy and image (b) is the corrected

| Find: 🔹 💠 🖨                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>D. Workfen Acksor</li> <li>D. S. K. Tuget</li> <li>D. 1. Set Tuget</li> <li>D. 1. Set Tuget</li> <li>D. 1. Set Tuget Device and Synthesis Tool</li> <li>D. 2. Device Model Furth C. Cole Careerasin</li> <li>D. 2. Device Model Furth C. Cole Careerasin</li> <li>D. 2. Device Model Furth C. Cole Careerasin</li> <li>D. 1. Cole Generation</li> <li>D. 1. Device Model Furth Cole Careerasin Calcon</li> <li>D. 1. Device Model Careerasin</li> <li>D. 1. Device Model Furth Cole Careerasin Calcon</li> <li>D. 1. Device Generation</li> <li>D. 1. Set Tool Careerasin Calcon</li> <li>D. 1. Set Tool Careerasin C</li></ul> | Al. Perform Logic Synthesis<br>Andyse<br>The Synthesis for guarding FROA device<br>The The Table<br>Result @ Pascel<br>Class later and the Synthesis |

Figure 2.14: HDL coder workflow advisor (5)

Figure 2.15: Example of color correction on hardware

image with accurate color.

# 2.4 RGB2YUV

### 2.4.1 Introduction

Color image processing is a logical extension to the processing of grayscale images. The main difference is that each pixel consists of a vector of components rather than a scalar. Usually, a pixel from an image has three components: red, green and blue. These are defined by the human visual system. Color is typically represented by a three dimensional vector and user can define how many bits each component have. Besides using RGB to represent the color of an image, there are different ways to represent an image to make subsequent analysis or processing easier, such as CMYK (subtractive color model, mainly used in color printing) and YUV (used for video/image compression and television system). Here Y stands for luminance signal, which is the combination of RGB components, with the color provided by two color difference signals U and V.

Because many video/image processing is performed in YUV space or simply in grayscale, so RGB to YUV conversion is very desirable in many video system. We can use simple functions to show convert these components like:

$$Y = 0.299R + 0.587G + 0.114B \tag{2.6}$$

$$U = 0.492(B - Y) \tag{2.7}$$

$$V = 0.877(R - Y) \tag{2.8}$$

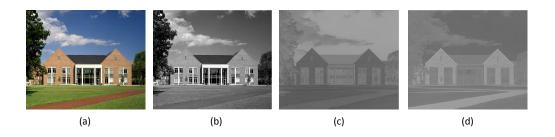

Figure 2.16: Illustration of RGB to YUV conversion

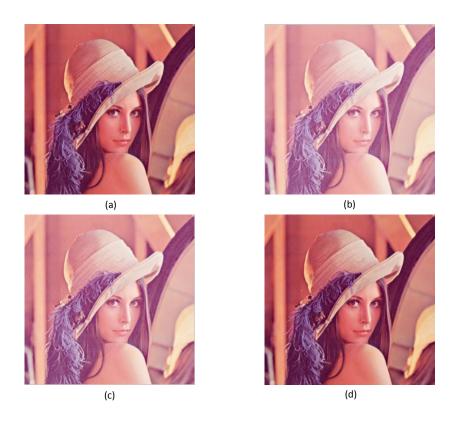

Fig 2.16 illustrates the result of convert color image in RGB domain to image with YUV components. Image (a) is the color image with RGB representation and (b) (c) (d) is YUV components of the image, respectively.

#### 2.4.2 Simulink Implementation

Figure 2.17: Flow chart of RGB2YUV Simulink system

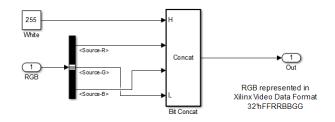

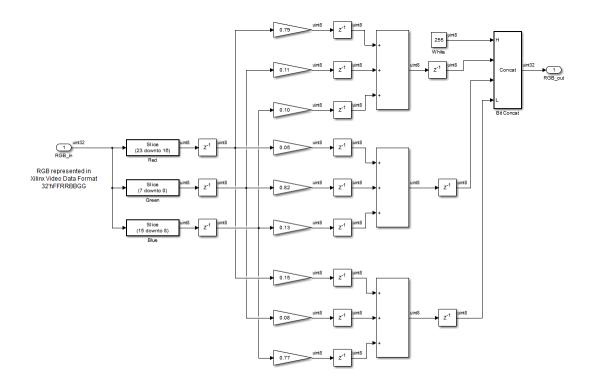

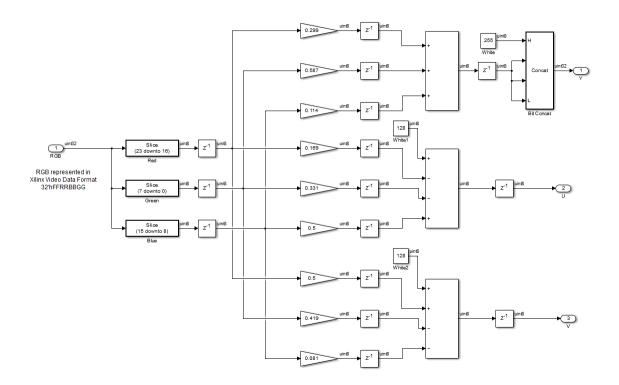

Figure 2.17 gives an overview of the entire RGB2YUV Simulink system. The other blocks are exactly identical with those in color correction model except the RGB2YUV kernel block. The kernel block detail is shown in fig. 2.18. The input bus signal is represented in Xilinx video data format, which is 32'hFFRRBBGG. So we first separate the bus signal to three color components RGB. Red component is bit 23 to 16; Green is bit 7 to 0; Blue is bit 15 to 8. The gain blocks implement multiplication. The sum blocks calculate add and subtract result, which are defined in block parameter. Matrix multiplication is implemented using these gain and sum blocks. Finally the corrected color components are concatenated again to a bus signal. The delay blocks inserted in between will be transferred to registers in hardware, which break down the critical path to achieve higher clock frequency.

Figure 2.18: Implementation of RGB2YUV block in Simulink

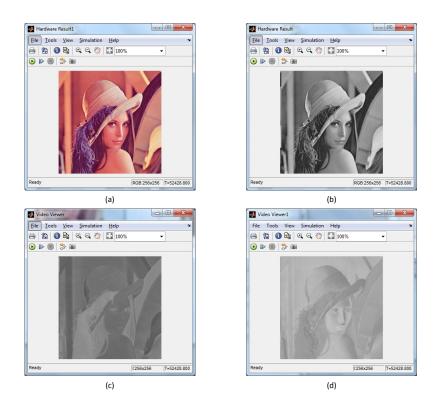

Fig 2.19 gives the simulation result in Simulink environment. Image (a) is the color image with RGB representation and (b) (c) (d) is YUV components of the image, respectively.

#### 2.4.3 FPGA Implementation

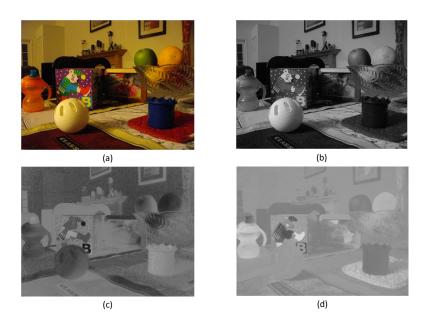

We validate the entire RGB2YUV design on a KC705 FPGA platform using generated HDL code. The reported maximum frequency is 159.69 MHz. The resources utilization of the RGB to YUV system on FPGA is as follows: 106 slice registers and 286 slice LUTs. Fig. 2.20 illustrates the result of our RGB to YUV system on hardware. Image (a) is the color image with RGB representation and (b) (c) (d) is YUV components of the image, respectively. To display Y(U/V) component in gray scale, we assign the value of signal component to all RGB channels.

Figure 2.19: Example of RGB2YUV in Simulink

### 2.5 Gamma Correction

### 2.5.1 Introduction

Gamma correction is a nonlinear operation used to adjust pixel luminance in video or still image systems. Image seems bleach out or too dark when it is not properly corrected. Gamma correction controls the overall brightness of an image, crucial for displaying an image accurately on a computer screen.

Gamma correction could be defined by the following power-law expression:

$$V_{out} = K \times V_{in}^r \tag{2.9}$$

where K is a constant coefficient and  $V_{in}/V_{out}$  is non-negative real values. In the

Figure 2.20: Example of RGB2YUV on hardware

common case of K = 1, the inputs and outputs are normalized in the range of [0, 1]. For 8-bit grayscale image, the input/output range is between [0, 255]. For the case that gamma value r < 1, it is called an encoding gamma; conversely a gamma value r > 1 is called a decoding gamma.

Gamma correction is necessary for image display due to nonlinear property of computer monitor. Almost all computer monitors have an intensity to voltage response curve which is roughly r = 2.2 power function. When computer monitor is sent a certain pixel of intensity x, it will actually display a pixel with intensity  $x^{2.2}$ . This means that the intensity value displayed is less than what it is expected to be. For instance,  $0.5^{2.2} = 0.22$ .

To correct this annoying bug, the input image intensity to the monitor must be gamma corrected. Since the relationship between the voltage sent to monitor and intensity displayed could be depicted by gamma coefficient r and monitor manufactures provide the number, we could correct the signal before it reaches the monitor

Figure 2.21: Illustration of gamma correction

using a  $\frac{1}{r}$  gamma coefficient. The procedure is shown in fig. 2.21. Image (a) is original video frame; (b)depicts how the image looks like on monitor of gamma coefficient 2.2 without gamma correction. We adjust pixel intensity using a  $\frac{1}{r}$  gamma coefficient and get image(c), which looks like image (d) on the monitor with nonlinear property.

If gamma correction is performed perfectly for the display system, the output of monitor correctly reflects the image (voltage) input. Note that monitor systems have many influencing factors, such as brightness and contrast setting other than gamma adjustment. Adjusting monitor display is a comprehensive task.

#### 2.5.2 Simulink Implementation

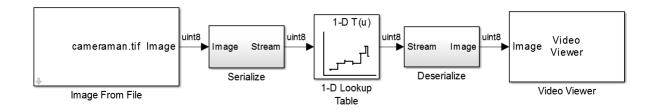

Figure 2.22 gives an overview of the entire gamma correction Simulink model. The Image From File block, Serialize block, Serialize block and video viewer block are

Figure 2.22: Flow chart of gamma correction system in Simulink

shared with those in previous color correction system. The key block of gamma correction system is 1-D lookup table from hdlsupported library. The gamma curve is described in block parameter as in fig. 2.23.

| 🚡 Function Bloc  | k Paramete   | rs: 1-D Lookup | Table      |   |                                       |                |              | ×             |

|------------------|--------------|----------------|------------|---|---------------------------------------|----------------|--------------|---------------|

| – Lookup Table ( | n-D)         |                |            |   |                                       |                |              |               |

|                  | ariables. Bi | reakpoint sets |            |   | arches. The tab<br>ositions in the ta |                |              |               |

| Table and Brea   | akpoints     | Algorithm      | Data Types |   |                                       |                |              |               |

| Number of table  | e dimensio   | ns: 1          |            | • |                                       |                |              |               |

| Table data:      | (([0:255]    | /255).^0.45)*  | \$255      |   |                                       |                |              |               |

| Breakpoints 1:   | 0:255        |                |            |   |                                       |                |              |               |

| Edit table and   | breakpoint   | ts             |            |   |                                       |                |              |               |

| Sample time (-:  | L for inheri | ited): -1      |            |   |                                       |                |              |               |

|                  |              |                |            |   |                                       |                |              |               |

|                  |              |                |            |   |                                       |                |              |               |

|                  |              |                |            |   |                                       |                |              |               |

|                  |              |                |            |   |                                       |                |              |               |

|                  |              |                |            |   |                                       |                |              |               |

|                  |              |                |            |   |                                       |                |              |               |

|                  |              |                |            |   |                                       |                |              |               |

|                  |              |                |            |   | <u>O</u> K                            | <u>C</u> ancel | <u>H</u> elp | <u>A</u> pply |

Figure 2.23: Parameter settings for 1-D Lookup Table

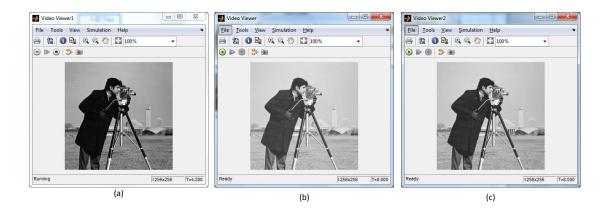

Fig 2.24 gives the gamma correction simulation result in Simulink environment. Image (a) is the the original video frame in grayscale and (b) (c) is the corrected image entering nonlinear computer monitor with gamma coefficient 2.2 and 1.8.

#### 2.5.3 FPGA Implementation

We validate the entire gamma correction design on a KC705 FPGA platform using generated HDL code. The reported maximum frequency is 224.31 MHz. The

Figure 2.24: Example of gamma correction in Simulink

resources utilization of the gamma correction system on FPGA is as follows: 50 slices, 17 slice flip flops and 95 four input LUTs. Fig. 2.25 illustrates the result of our gamma correction system on hardware. We apply the same gamma correction block on all RGB color channels. Image (a) is the original color image with RGB representation. Image (b) and (c) are the result of gamma correction system of coefficients 2.2 and 1.8. Image (d) is what the color image looks like on a real monitor with nonlinear property.

### 2.6 2D FIR Filter

#### 2.6.1 Introduction

The 2D FIR filter is a basic filter for image processing. The output signals of a 2D FIR filter can be computed using the input samples and previously computed output samples as well as filter kernel. For a causal discrete-time FIR filter of order N of 1 dimension, each value of the output sequence is a weighted sum of the most recent input values, as shown in equation (2.10):

Figure 2.25: Example of gamma correction on hardware

$$y[n] = b_0 x[n] + b_1 x[n-1] + b_2 x[n-2] + \dots + b_N x[n-N]$$

(2.10)

where x[n] is the input signal and the y[n] is the output signal. N is the filter order, an Nth order filter has (N+1) terms on the right hand side.  $b_i$  is the value of the impulse response at the i-th instant for  $0 \le i \le N$  of an Nth order FIR filter. For 2-D FIR filter, the output signals rely on both previous pixels of current line and pixels of upper lines. Upon the 2D filter kernel, the 2D FIR filter could be either high-pass filter or low-pass filter. Equation (2.11) and (2.12) gives example of typical high pass filter kernel and low pass filter kernel.

$$0 \quad -1 \quad 0$$

$$HighPass = \begin{bmatrix} -1 & 4 & -1 \end{bmatrix}$$

$$0 \quad -1 \quad 0$$

$$1/16 \quad 1/8 \quad 1/16$$

$$LowPass = \begin{bmatrix} 1/8 & 1/4 & 1/8 \end{bmatrix}$$

$$1/16 \quad 1/8 \quad 1/16$$

$$(2.12)$$

Figure 2.26: Illustration of 2D FIR filter

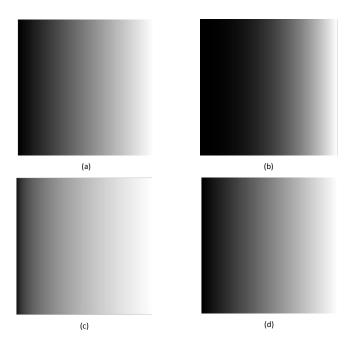

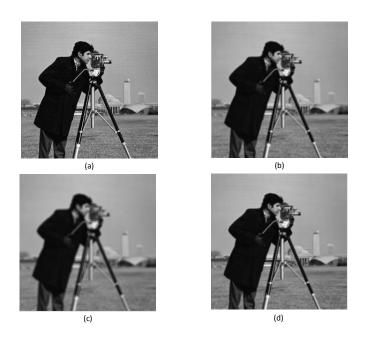

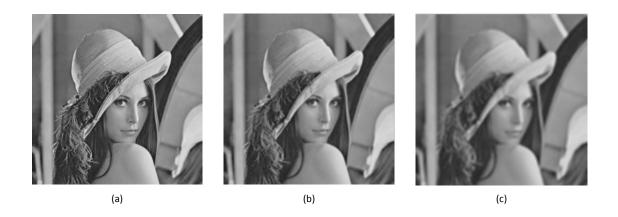

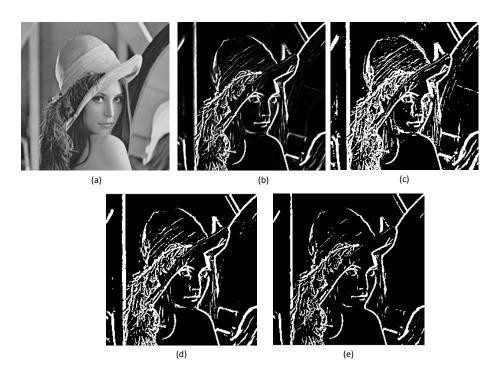

In this chapter, we will take low pass filter for example. Fig 2.26 illustrates the result of low pass filter using different filter kernel. Image (a) is the original image and (b) (c) (d) is the filtered image, respectively.

Figure 2.27: Flow chart of 2D FIR filter system in Simulink

#### 2.6.2 Simulink Implementation

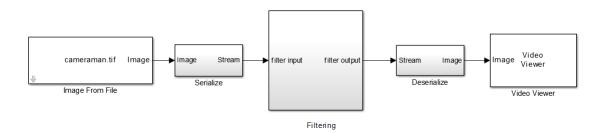

Figure 2.27 gives an overview of the entire 2D FIR filter Simulink system. The architecture is also shared with following 2D filters in this chapter. The filtering block is the only difference. Other blocks are the very same ones.

Figure 2.28: Flow chart of 2D FIR filter block in Simulink

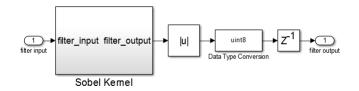

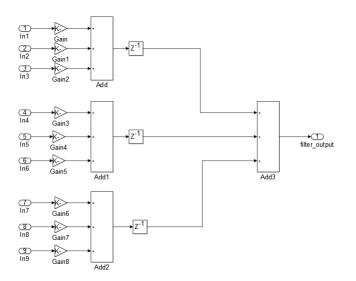

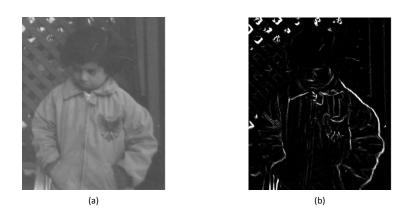

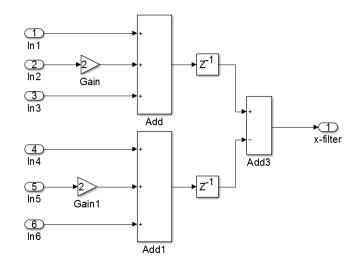

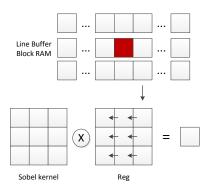

Sobel filter block is implemented as fig. 2.28. We design a Sobel kernel block to calculate the filter response of input image, then calculate the response absolute value and convert it to uint8 data type for further display.

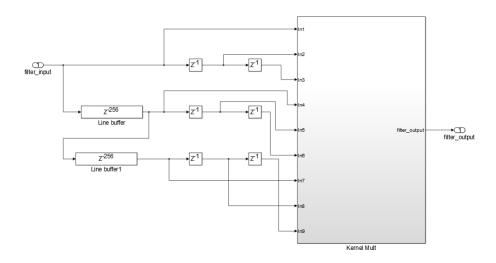

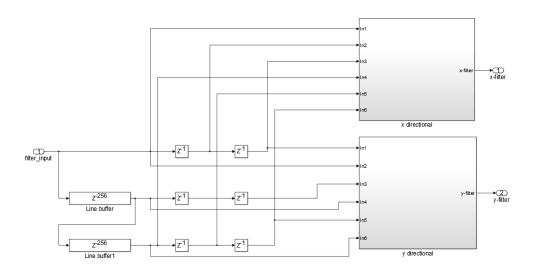

Fig. 2.29 is the architecture of Sobel kernel block. The 2D FIR algorithm maintains three line buffers. Each iteration the input pixel is pushed into the current line buffer that is being written to. The control logic rotates between these three buffers when it reaches the column boundary. Each buffer is followed by a shift register and data at the current column index is pushed into the shift register. At each iteration a 3x3 kernel of pixels are formed from the pixel input, shift registers

Figure 2.29: Flow chart of Sobel Kernel block

and line buffer outputs. The kernel are multiplied by a 3x3 filter coefficient mask and the sum of the result values is computed as the pixel output as in figure 2.30.

Figure 2.30: Architecture of kernel mult block

Fig 2.31 gives the low pass 2D FIR filter result in Simulink environment. Image (a) is the original video frame in grayscale and (b) is smoothed image output using low pass filter in equation (2.12).

Figure 2.31: Example of 2D FIR filter in Simulink

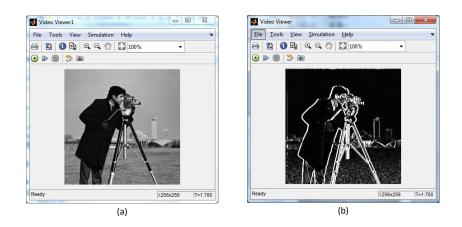

## 2.6.3 FPGA Implementation

Figure 2.32: Example of 2D FIR filter on hardware

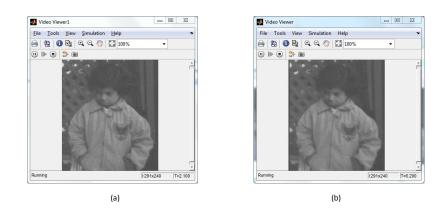

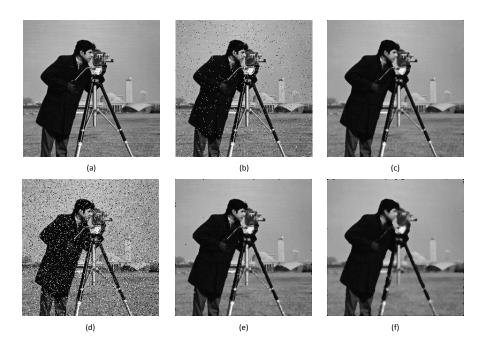

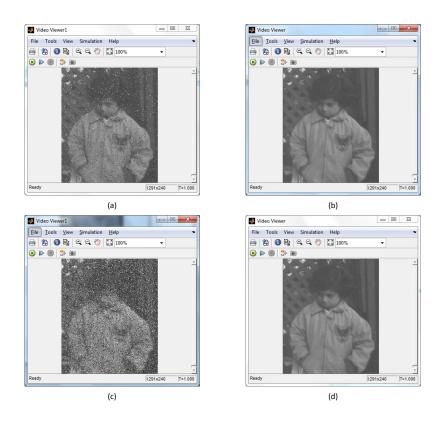

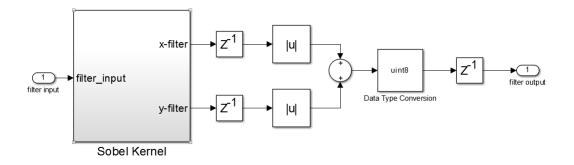

We validate the entire 2D FIR filter design on a KC705 FPGA platform using generated HDL code. The reported maximum frequency is 324.45 MHz. The resources utilization of the 2D FIR filter system on FPGA is as follows: 71 slices, 120 flip flops, 88 four input LUTs and 1 FIFO16/RAM16. Fig. 2.32 illustrates the 2D FIR filter system on hardware. Image (a) is the color image in grayscale and (b) (c)is blurred image using different kinds of low pass filter kernels.

# 2.7 Median Filter

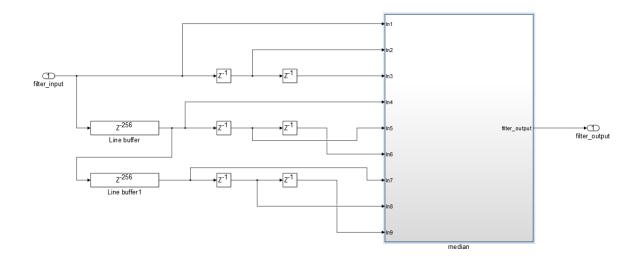

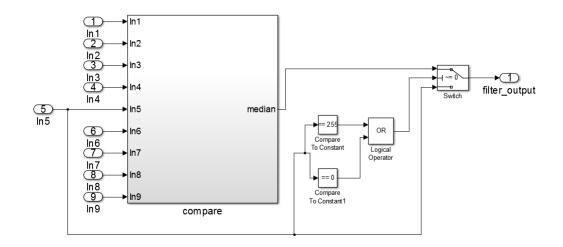

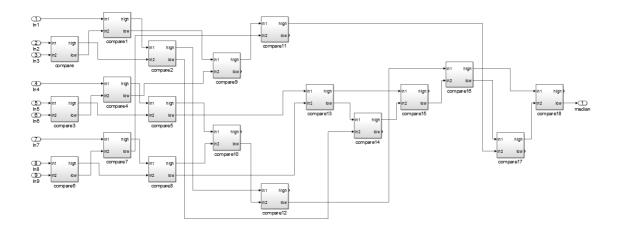

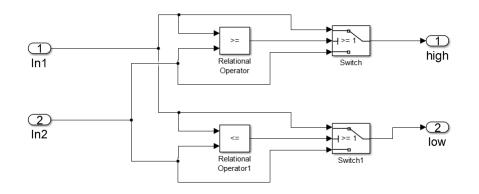

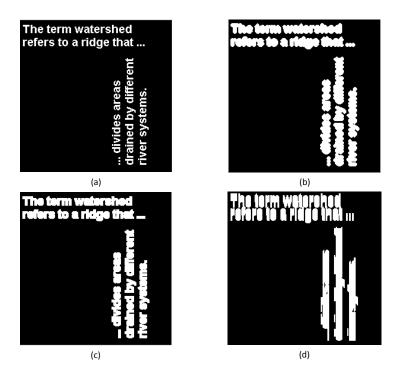

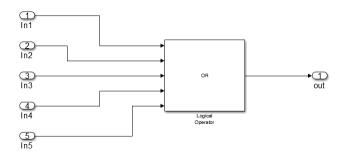

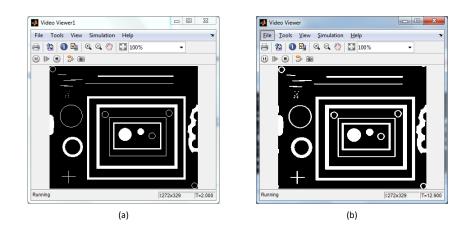

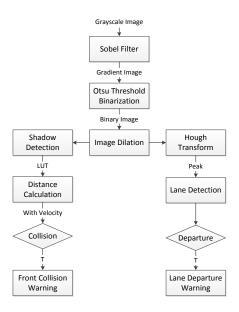

#### 2.7.1 Introduction