### A PARALLEL EMBEDDED NEURAL NETWORK FOR AN INTELLIGENT TURN-BASED GAME ENGINE

### A Major Qualifying Project Report:

submitted to the Faculty

of the

### WORCESTER POLYTECHNIC INSTITUTE

in partial fulfillment of the requirements for the

Degree of Bachelor of Science

by

Stephen Mann ECE Matthew Netsch ECE/CS

Date: May 03, 2010

Approved:

Professor David C. Brown, CS Major Advisor

1. Neural Network

- 2. Embedded

- 3. Parallel

Professor Stephen J. Bitar, ECE Major Advisor

# Abstract

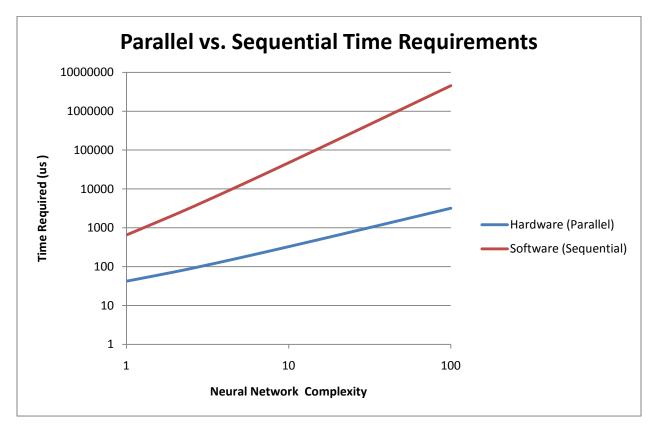

The purpose of this project was to design a parallel digital circuit that performs neural network (NN) calculations more efficiently than traditional software implementations, by taking advantage of the NN's inherent parallel structure. User interfaces for NN training and testing were developed. Tic-Tac-Toe position evaluation was used as a test domain. Testing showed that the parallel hardware NN decreased the number of required clock cycles by an order of magnitude.

# Contents

| Abstract2 |                                                      |    |

|-----------|------------------------------------------------------|----|

| Contents  | S                                                    | 3  |

| 1 Intro   | roduction                                            | 5  |

| 1.1       | Problem Statement                                    | 5  |

| 1.2       | Background                                           | 6  |

| 1.2.      | .1 The Neural Network Model                          | 6  |

| 1.2.      | .2 Forward Propagation                               | 7  |

| 1.2.      | .3 Negamax                                           | 10 |

| 1.2.      | .4 Back-Propagation                                  | 11 |

| 1.3       | Requirements and Goals                               | 17 |

| 1.3.      | .1 Parallel Neural Network Design                    |    |

| 1.3.      | .2 Software Evaluation Tool                          |    |

| 1.3.      | .3 Verify Parallel System Efficiency and Correctness |    |

| 2 Des     | sign                                                 | 20 |

| 2.1       | General System                                       | 20 |

| 2.1.      | .1 TAC                                               | 20 |

| 2.1.      | .2 Software Driver                                   | 21 |

| 2.1.      | .3 Hardware Driver                                   | 21 |

| 2.1.      | .4 Hardware NN                                       | 22 |

| 2.2       | Trainer, Analyzer, Controller                        | 22 |

| 2.2.      | .1 Network Tab                                       | 24 |

| 2.2.      | .2 Device Tab                                        | 27 |

| 2.2.      | .3 Test Tab                                          |    |

| 2.2.      | .4 Train Tab                                         | 31 |

| 2.2.      | .5 Developing for TAC                                |    |

| 2.2.      | .6 File Specifications                               | 40 |

| 2.3       | Parallel Neural Network                              | 40 |

| 2.3.      | .1 Parallel Structure Analysis                       | 40 |

|   | 2   | 2.3.2 |        | Efficiency                |

|---|-----|-------|--------|---------------------------|

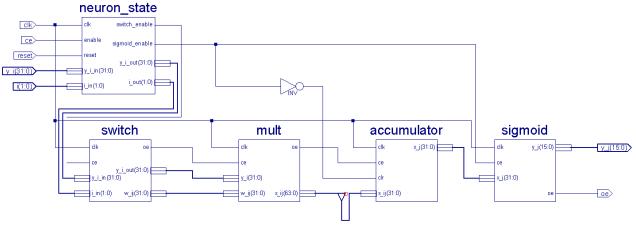

|   | 2   | 2.3.3 |        | Neuron                    |

|   | 2.4 |       | Hard   | dware and Software Driver |

|   | 2   | 2.4.1 |        | Software Driver           |

|   | 2   | 2.4.2 |        | Hardware Driver54         |

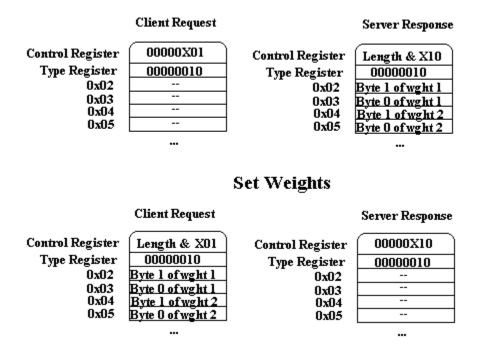

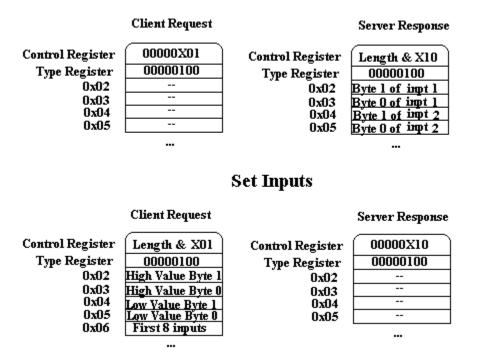

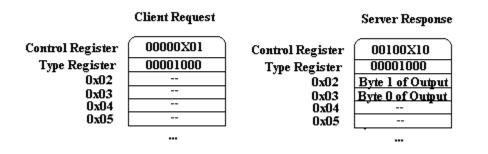

|   | 2   | 2.4.3 |        | Message Types             |

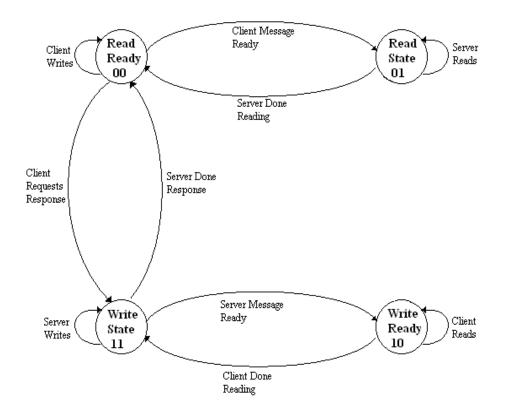

|   | 2   | 2.4.4 |        | Connection Protocol61     |

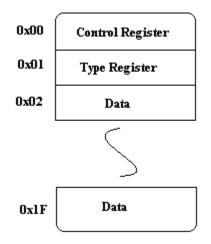

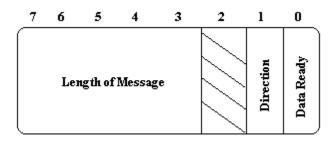

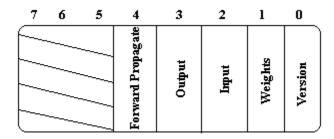

|   | 2   | 2.4.5 |        | Registers62               |

|   | 2   | 2.4.6 |        | Driver Tester Interface   |

| 3 | A   | Analy | /sis . |                           |

|   | 3.1 |       | Hard   | dware Neural Network      |

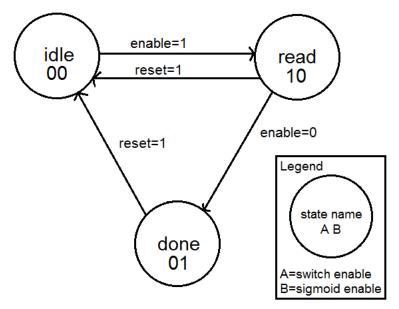

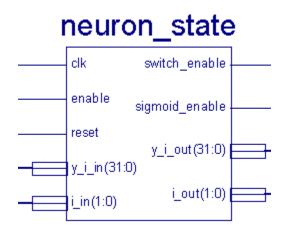

|   | 3   | 8.1.1 |        | Neuron State              |

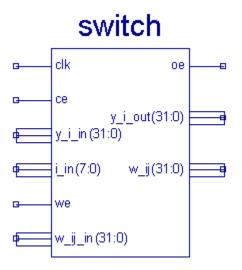

|   | 3   | 3.1.2 |        | Switch70                  |

|   | 3   | 3.1.3 |        | Multiplier71              |

|   | 3   | 3.1.4 |        | Accumulator72             |

|   | 3   | 3.1.5 |        | Sigmoid73                 |

| 4 | C   | Conc  | lusio  | on82                      |

| 5 | F   | Refei | rence  | es85                      |

| 6 | A   | Appe  | ndix   | A- Distribution of work   |

|   | 6.1 |       | Step   | hen Mann86                |

|   | 6   | 5.1.1 |        | Deliverables              |

|   | 6   | 5.1.2 |        | Paper                     |

|   | 6.2 |       | Mati   | thew Netsch               |

|   | 6   | 5.2.1 |        | Deliverables              |

|   | 6   | 5.2.2 |        | Paper                     |

| 7 | A   | Appe  | ndix   | B - Lessons Learned       |

|   | 7.1 |       | Stev   | e87                       |

|   | 7.2 |       | Mat    | t87                       |

# **1** Introduction

The purpose of this project is to design an efficient hardware neural network (NN) and to apply this NN to solving a real world problem: playing Tic-Tac-Toe. Common computer implementations of artificial NN's are inefficient due to the sequential nature of their processors, which can only execute one calculation at a time; artificial NN's contain, due to their parallel nature, many independent calculations which can be executed simultaneously on custom hardware to greatly improve the efficiency.

This project will be designed to run on a Field Programmable Gate Array (FPGA). FPGA's are hardware devices that can be programmed to implement custom digital designs by physically mapping paths between the logic gates on each device. Using an FPGA allows the structure of the NN to be reprogrammed without any monetary cost.

The FPGA containing the NN design will be able to receive inputs and to send output results to a common computer through a Universal Serial Bus (USB) interface. This connection allows software to communicate with the FPGA NN, enabling the software to perform NN calculations using the connected device.

All of these components will be combined and used to play Tic-Tac-Toe, a turn based board game. Evaluating Tic-Tac-Toe positions using the FPGA will verify that the hardware design correctly implements the artificial NN algorithm and that the accuracy of the hardware implementation of the artificial NN is satisfactory.

Once all of these parts are designed and integrated, the performance of both the hardware NN and a software NN will be compared to determine the efficiency improvement of the hardware implementation over the software implementation.

# **1.1 Problem Statement**

Artificial NN's are models used to simulate the human brain (Orr 1999). These simulations, while far from accurately modeling a biological brain, have been proven to be effective at pattern classification and are commonly used for image processing and speech recognition (Li 1990). However, the complexity of NN's makes them inefficient to compute using modern processors.

Computers are useful tools for solving problems written in a sequential algorithmic form. However, NN models cannot be efficiently written in such a way. The problem lies in the massively parallel structure of the NN, as each of its parallel connections must be computed in sequence in order to produce its output.

There are ways to distribute work with computers and simulate parallelism. However, for the size of a NN model for a small application such as Tic-Tac-Toe, this would require many physical processor cores. A common application such as image processing would require on the order of thousands of cores. Further, to make matters worse, many NN applications would be useful in mobile devices where

processing resources are limited. Solutions neglecting the benefit of true parallelism are therefore currently infeasible without substantial computing power.

Part of the problem is that computer processors are designed to be generic problem solvers. This makes them inefficient and expensive for this specific parallel application. A processor especially designed to carry out NN operations would make this more efficient. This technique of distributing specialized computation is commonly used in devices such as video cards for rendering graphics and sound cards for processing sound. Our work involves designing a custom processor for providing the parallel computations of a NN model.

# **1.2 Background**

An artificial NN is modeled after the human brain (Orr 1999). Artificial neural networks are computational models which can be trained to recognize patterns, known as a pattern classifier. What makes this particular pattern classifier useful is that, if trained correctly, it can apply previous knowledge to unencountered situations and produce a satisfactory result. For example, in the application of image processing, a NN can be trained to recognize tanks looking at images from an unmanned air vehicle (UAV) (Bianchini, et al. 2004). However, most classifier algorithms over-fit what they were trained to recognize. In other words, they can classify objects they have seen before very well, but not if the object is in a slightly different situation. In the UAV application, if the NN was trained with images of tanks from a military base, but the UAV is operating in the desert, the lighting will be different enough to make other classifiers not work effectively.

# 1.2.1 The Neural Network Model

Many neurons are arranged together in the brain in a complex network. A single neuron acts as a valve to change the flow of information propagating through the NN. Neurons will strengthen some signals and limit others in order to produce the final resulting output. In a brain, neurons collect inputs like water flowing into a dam. When the water attains a certain predefined level, it empties everything into its outputs and starts over again.

http://www.greenspine.ca/media/neuron\_culture\_800px.jpg

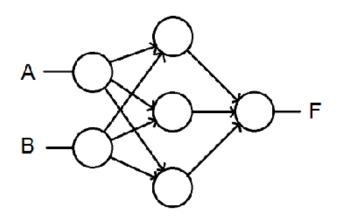

Figure 1 – A biological neural network (left); a simulated computer model (right)

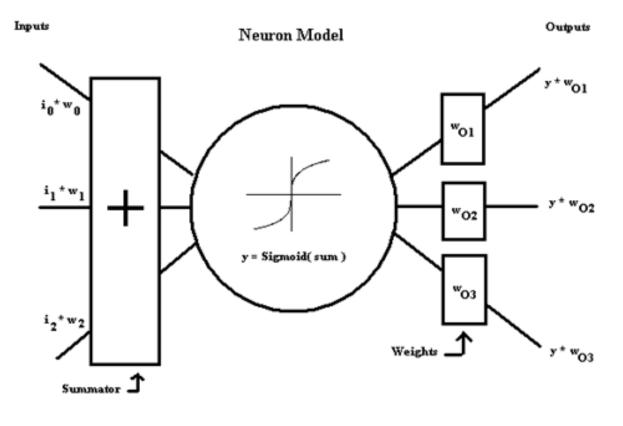

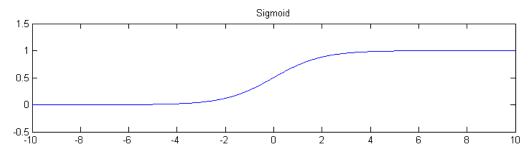

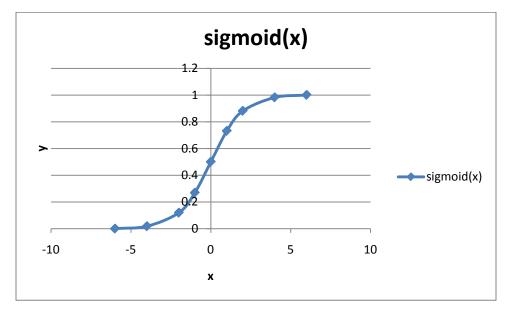

The model shown in Figure 1 is called a multi-layered perceptron. This special type of NN is **feed**-**forward**, meaning that there are no loops in the directed graph. This also means that the neurons are grouped into layers and that every neuron in a layer is connected to every neuron in the layer after it. This simple model consists of three layers; an input layer, a hidden layer, and finally an output layer. In order to simulate the limiting of the signal that the biological model has, connections are assigned coefficients, called **weights**, each of which multiplies any signal passing through it. Once all of the signals from input connections to a neuron are obtained, the resulting value is summed. The neuron takes this sum and applies a **sigmoid** activation function to it, commonly a hyperbolic tangent or  $\frac{1}{1+e^{-x}}$ , where 'x' is the sum of the inputs to the neuron. This function limits the output of the neuron, and its result is then applied to each output connection. Each output connection then scales the value applied to it, leading into its output neuron as an input.

### **1.2.2 Forward Propagation**

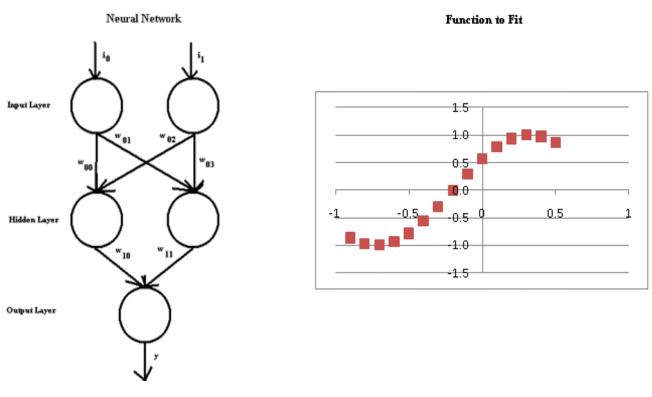

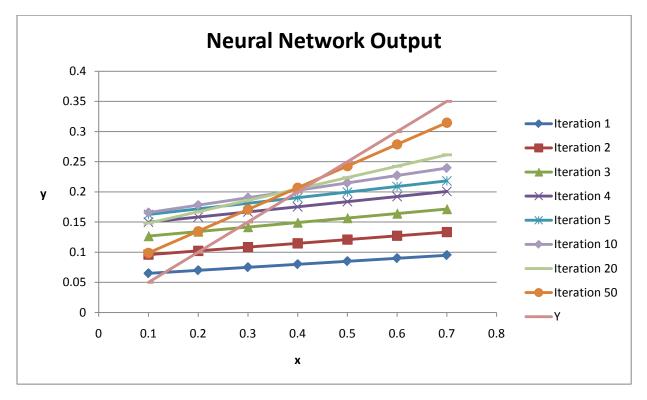

The application that we use our NN for is a common technique called curve fitting. Curve fitting is the process of determining a function that closely matches a given set of input, output pairs. Neural networks are good at doing this because they are able to recognize patterns in the data set and fill in the missing information between each data point. Figure 3 shows a simple neural network to use as an example. This NN will be used to fit a third order polynomial.

Figure 3 – The simple neural network (left); Target function to fit (right)

When adjusted, the connection weights in the NN cause its output to change shape. That is, the weights along the NN's connections can be chosen in such a way that the output of the neural network resembles a specific cubic function when its input varies. The goal of training a network is to adjust its weights in such a way that the output function closely matches the training data. The process of how a neural network produces its output from its given inputs is called **forward propagation**.

As shown before, each simulated neuron has the output function:

$$\sigma(x) = Neuron \ activation \ function = \frac{1}{1 + e^{-x}}$$

Eq 1.1

$$y = \sigma\left(\sum_{j=1}^{n} i_j w_j\right)$$

Eq 1.2

Therefore, after some algebra, the equation of the final output of the example neural network in Figure 3 is:

$$y(\vec{i},\vec{w}) = \sigma \Big( w_{10}\sigma(w_{00}i_0 + w_{02}i_1) + w_{11}\sigma(w_{01}i_0 + w_{03}i_1) \Big)$$

Eq 1.3

The weights act as the neural network's memory and will cause the neural network to produce the target cubic function when chosen correctly. Techniques for determining weights that allow the neural

network to approximate functions will be discussed in section 1.2.4. The target function we are trying to approximate for this example is:

$$f(x) = \sin\left(3\left(x + \frac{1}{5}\right)\right)$$

Eq 1.4

Though it is beyond the scope of this section, we decided to use the sigmoid of f(x) as the target function. This choice had to do with problems obtaining negative output values when determining weights. Therefore, after training the NN to approximate the sigmoid of f(x), we applied the inverse of the sigmoid on the output of the neural network to obtain the original f(x). The weights that allow this neural network to produce a good approximate of f(x) over the arbitrarily chosen bounds of -0.9 to 0.5 are:

$$\vec{w} = \{-3.562126, -2.166572, -0.784935, -0.562360, -9.525776, 9.823804\}$$

The simplified output equation of the neural network becomes:

$$out(x) = \sigma(-\sigma(-3.562126x - 0.784935) * 9.525776 + \sigma(-2.166572x - 0.562360) * 9.823804)$$

where  $\vec{i} = \{x, 1\}$

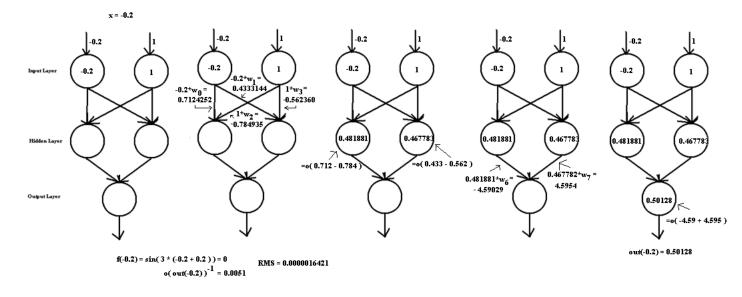

out(x) above is about equivalent to f(x) over the range -0.9 to 0.5. Note that the input vector, 'i,' contains a second term that is always one. This input value is constant, and is passed through to the next layer because no sigmoid function is applied to the input neuron. The output of this neuron shifts the output of the entire network by a nearly constant value, helping to offset the output function in a way that might be difficult for the varying input terms. Figure 4 demonstrates how the neural network produces out(x).

**Figure 4-Forward Propagation**

For the weights chosen, the output produced by the neural network when given x = -0.2 is 0.50128. Remember, as stated previously, that the out(x) function must have the inverse sigmoid applied to it. The actual result is therefore 0.0051, and when compared to the expected value of 0 it has a root mean squared (RMS) error of only 1.64E-6. This value is calculated by taking the square root of the sum of all squared output errors, where the errors are calculated by subtracting the actual output from the expected output. Given a set of input, output pairs, the neural network performs well, producing outputs with an RMS error of only 1.34746E-5. Determining the weights that will produce the expected output is a topic for later.

### 1.2.3 Negamax

Our work uses a neural network to perform a function approximation of a function called Negamax. Negamax is a recursive function that evaluates a game position and returns a value representing the favorability of the position with respect to the current player. Using Negamax even for simple games such as Tic-Tac-Toe requires a lot of recursion and on a modern computer can take up to a couple seconds to produce a result.

The underlying data structure of the Negamax algorithm is a game tree. At the root of a game tree is the first position in the game to be analyzed. Each branch of the root node represents a position possible to reach by making a single move in the root position. The same properties are true for each node in the game tree—the child positions represent possible positions resulting from their parent positions. All leaf nodes in a game tree represent positions in which the game has ended.

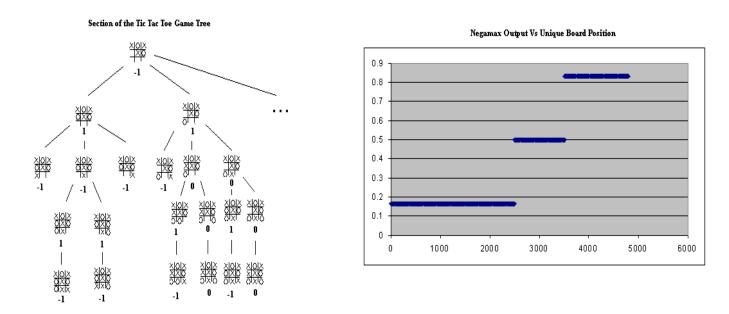

#### Figure 5 – Section of the Tic Tac Toe game tree (left); Negamax output as a function (right)

Although Tic-Tac-Toe has a game tree with hundreds of thousands of different positions, there are only 4804 unique board positions. The graph in Figure 5 only shows these unique board positions on the x axis (indexed). The expected output for the Tic-Tac-Toe function is shown on the y axis for the given

board position. This is the function our neural network should approximate. The diagram in the Figure 5 on the left shows how Negamax evaluates up the game tree from the leaf nodes.

Negamax produces its result by traversing through the entire game tree. When the algorithm hits a leaf node it assigns it a 1 for the current player winning, a 0 for draw, and a -1 for the current player losing. Whether or not the position is win or a loss is decided from the context of the next player to move. For example, if X was the last player to place and resulted in a win then the result would be -1 as it is a loss for the next player to place an O. The node directly above the leaf node will take the inverse of the scores all of its children and assign itself the greatest of these values. This occurs until the root node is reached.

Our algorithm takes the score of the root node and assigns a 0.8333 if -1 is returned, 0.5 if 0 is returned, and 0.1667 if 1 is returned. These values are chosen to help with the training and will be explained later.

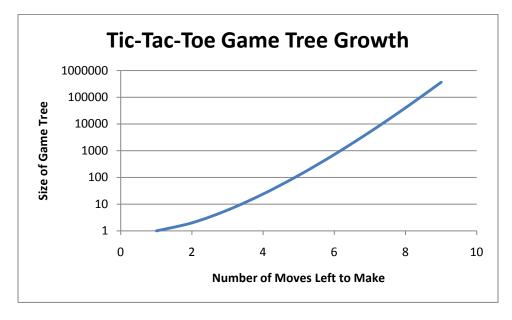

#### Figure 6 - Tic-Tac-Toe Game Tree Growth

The number of recursive Negamax function calls is on the order of hundreds of thousands seen in Figure 6, even for a small game tree generated from Tic-Tac-Toe. However, a NN would only require a fixed number of multiplications and a handful of sigmoid calculations to get close to the same result. The Negamax algorithm grows exponentially with the depth of the tree it searches. Therefore, the neural network is a more efficient way of producing this result, since it always takes the same amount of time to execute. This assumes we have the correct weights to produce the Negamax function, which are obtained through using the back-propagation algorithm.

### **1.2.4 Back-Propagation**

A neural network must be trained before it produces meaningful results. Most problems require neural networks with different structures, which require that there be some way to generate a network structure relevant to a problem. The size of a network—the number of neurons and the number of

interconnected neurons—must be chosen specifically for a problem. Once this structure is determined, the weights of the connections between neurons must then be adjusted such that the output of the NN matches its expected output.

The goal of adjusting the weights in a NN is to reduce the NN's output error. Given a set of correct inputs and outputs, the network produces a corresponding set of outputs. The difference between the given outputs and the NN's outputs is the error, represented by:

$$\begin{split} o_{k} &= Expected \ output \ of \ neuron \ k \\ y_{k} &= Actual \ output \ of \ neuron \ k \\ E &= \frac{1}{2} \sum_{k \in output \ neurons} (o_{k} - y_{k})^{2} \end{split} \tag{Eq 1.5}$$

If  $y_k$  is adjusted such that E = 0, then the network will have a perfect fit to the set of expected outputs. In most cases, this is computationally infeasible to calculate due to the large number of neurons and weights resulting in the need to solve a set of large multivariable equations. So instead of finding the global minimum error, most training algorithms attempt to find a local minimum resulting in an error below a predetermined threshold.

Local minima and maxima of the error function are found at the points of a curve where the derivative is equal to zero. To find those points, the derivative of the error function must be determined.

A neural network trained to find the best-fit line for a given set of data is a simple example of this.

$$\begin{aligned} x_k &= Weighted \ sum \ of \ neuron \ k's \ inputs \\ w_{jk} &= Weight \ from \ neuron \ j \ to \ neuron \ k \\ inputs(j) \rightarrow Set \ of \ input \ neurons \ to \ neuron \ j \\ x_k &= \sum_{j \in inputs(k)} w_{jk} y_j \\ y_k &= \sigma(x_k) \end{aligned}$$

Eq 1.6

Since this network is designed to fit a line, an activation function of  $\sigma(x) = x$  is used. This significantly simplifies the output of the NN by making it linear. For example, the output of a simple three neuron NN with two output neurons, is represented by  $y = \sigma(w_{01}\sigma(y_0) + w_{11}\sigma(y_1)) = w_{01}y_0 + w_{11}y_1$ , where  $y_0$  and  $y_1$  are the inputs to the network and y is the output.Similarly, the general neuron output equation simplifies to:

$$y_k = x_k = \sum_{j \in inputs \ to \ k} w_{jk} y_j$$

Eq 1.7

The gradient of the error function with respect to its weights points in the direction of steepest error increase. The opposite vector gives the direction of steepest decrease. Interpolating weights along this vector results in a smaller error, giving new weights of:

Introduction 13

$$\begin{array}{l} \alpha \rightarrow Learning \ rate; \ 0 < \alpha \leq 1 \\ w_{ij}' = w_{ij} + \alpha \frac{dE}{dw_{ij}} \end{array} \hspace{1cm} \mbox{Eq 1.8} \end{array}$$

The error gradient derivation:

$$\begin{aligned} \frac{dE}{dw_{ij}} &= \frac{d}{dw_{ij}} \left( \frac{1}{2} \sum_{k \in output \, neurons} (o_k - y_k)^2 \right) \\ &= (o_k - y_k) \left( -\frac{dy_k}{dw_{ik}} \right) \\ &= -(o_k - y_k) \frac{d}{dw_{ij}} \left( \sum_{i \in inputs(j)} w_{ij} y_i \right) \end{aligned}$$

$$= -(o_k - y_k)y_i$$

Eq 1.9

Now there is enough information to calculate the weight changes for the entire network. The final weight update is:

$$w'_{ij} = w_{ij} - \alpha \frac{dE}{dw_{ij}}$$

=  $w_{ij} + \alpha (o_j - y_j)y_i$  Eq 1.10

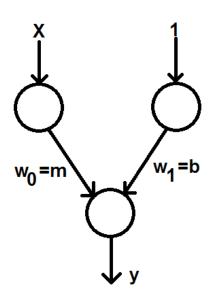

The network in Figure 7, a network specifically designed to model the equation y = mx + b, uses this weight update rule and a linear activation function to find the best fit line for a set of data points. The weights of the network are represented by "m" and "b," and the inputs are the coefficients of these weights, "x" and "1," respectively.

Figure 7 -Best fit line neural network

In order to test the effectiveness of the linear weight update rule, a set of data points following the line  $y = \frac{1}{2}x$  is used as training data. A plot of the network output after each pass over the data set is shown in Figure 8.

Figure 8 - Linear fit neural network output over time

Each iteration over the training data shifts the line towards the expected output. Figure 8 shows a graph of the error function, *E*, after each iteration.

Figure 9 - Linear fit network error

The error approaches zero as the number of iterations approaches infinity, giving final, correct weights of  $w_0 = \frac{1}{2}$  and  $w_1 = 0$ .

This example demonstrates the concept of error minimization in a single layer; back-propagation uses similar update rules, but also accounts for the error propagated from the output layer into the hidden layers. This derivation becomes much more complicated than that for the linear network due to the exponential activation function, often  $\sigma(x) = \frac{1}{1+e^{-x}}$ . This changes the weight update rule considerably:

$x_k = Sum of neuron k's inputs$   $w_{jk} = Weight on the connection from neuron j to neuron k$  inputs(j) = Set of input neurons to neuron j outputs(j) = Set of output neurons from neuron j $\alpha = \text{Learning rate}; (0 \le \alpha \le 1)$

$$x_k = \sum_{j \in inputs \ (k)} w_{jk} y_j$$

Eq 1.11

$$y_k = \sigma(x_k) = \frac{1}{1 + e^{-x_k}}$$

Eq 1.12

This new equation for  $y_k$  which uses the sigmoid activation function produces a new error function derivative and weight update:

$$\frac{dE}{dw_{ij}} = -(o_j - y_j)\frac{dy_j}{dw_{ij}}$$

Eq 1.13

$$\frac{dy_k}{dw_{ij}} = \frac{d}{dw_{ij}}\sigma(x_j) = \frac{dy_j}{dx_j}\frac{dx_j}{dw_{ij}}$$

$$= \frac{d}{dw_{ij}}\frac{1}{1+e^{-x_j}}$$

$$= -\frac{e^{-x_j}}{(1+e^{-x_j})^2}\left(-\frac{dx_j}{dw_{ij}}\right)$$

$$= \frac{1}{(1+e^{-x_j})^2}y_i$$

$$= \frac{1}{1+e^{-x_j}}\left(1-\frac{1}{1+e^{-x_j}}\right)y_i$$

$$= \sigma(x_j)\left(1-\sigma(x_j)\right)y_i$$

$$= y_j(1-y_j)y_i$$

$$w'_{ij} = w_{ij} - \alpha\frac{dE}{dw_{ij}}$$

$$= w_{ij} - \alpha\left(-(o_j - y_j)\frac{dy_j}{dw_{ij}}\right)$$

$$= w_{ij} + \alpha y_i y_j(1-y_j)(o_j - y_j)$$

This update equation is proportionate to the linear weight update equation by a factor of  $y_j(1-y_j)$ , which turns out to be  $\frac{dy_j}{dx_j}$ . The corresponding error  $\frac{dE}{dx_j}$  is referred to as the **error signal**,  $\delta_j$ . Regardless of the layer or activation function, all weight updates are in the form of:

$$w_{ij}' = w_{ij} + \alpha \delta_j y_i$$

In order to calculate the error gradient for the hidden weights, the derivative of the error in terms of a hidden weight is:

$$\frac{dE}{dw_{ij}} = \sum_{k \in outputs(j)} \frac{dE}{dx_k} \frac{dx_k}{dy_j} \frac{dy_j}{dx_j} \frac{dx_j}{dw_{ij}}$$

$$= \sum_{k \in outputs(j)} \delta_k w_{jk} y_j (1 - y_j) y_i$$

$$= y_j (1 - y_j) y_i \sum_{k \in outputs(j)} \delta_k w_{jk}$$

And since  $\delta_i = \frac{dE}{dx_i}$  and  $\frac{dE}{dw_{ij}} = \frac{dE}{dx_j} \frac{dx_j}{dw_{ij}} = \delta_i \frac{dx_i}{dw_{ij}} = \delta_i y_i$ , then the error signal for the update of the hidden layer weights simplifies to:

# Introduction 17

$$\delta_j = \frac{\frac{dE}{dw_{ij}}}{y_i} = y_j (1 - y_j) \sum_{k \in outputs(j)} \delta_k w_{ij}$$

Eq 1.14

This gives the hidden weight update equation:

$$w'_{ij} = w_{ij} + \alpha y_i y_j (1 - y_j) \sum_{k \in outputs(j)} \delta_k w_{ij}$$

Eq 1.15

In summary, the following steps are performed to train the neural network for one data point:

1. Calculate the error signal,  $\delta_k$ , for each output layer neuron.

$$\delta_k = y_k (1 - y_k) (o_k - y_k)$$

Eq 1.16

2. Calculate the error signal,  $\delta_i$ , for the next layer above the output layer.

$$\delta_j = y_j (1 - y_j) \sum_{k \in outputs(j)} \delta_k w_{ij}$$

Eq 1.17

- 3. Repeat step two for each previous hidden layer.

- 4. Update the weights between each layer using the weight update rule.

$$w_{ij} \coloneqq w_{ij} + \alpha \delta_j y_i$$

Eq 1.18

Executing these steps for each data point in a set of training data is called a **training epoch** (Univ. of Nottingham). Given enough training epochs, the NN's RMS error over its set of training data will converge to a local minimum, producing an output that is a function fit to the training data.

### **1.3 Requirements and Goals**

The intent of our work is to improve upon the efficiency of the sequential neural network simulations. Neural networks are inherently parallel systems, and simulating them on sequential processors greatly reduces the efficiency. The goals of this project are to design and evaluate a parallel neural network design. Specifically, the goals are to:

- Design and simulate a parallel hardware neural network

- Verify that the parallel design produces a correct output more efficiently than the sequential design

The parallel neural network will be designed and applied in a real world application: an automated, intelligent turn-based game move. The turn-based game we have chosen is Tic-Tac-Toe because its exact solution can be fully computed in a reasonable amount of time. This will aid in proving correctness of the approximation that the neural network provides, since the correct output of every possible input is known. The requirements that fulfill the project goals are:

- Develop a parallel hardware neural network capable of communicating with a computer

- Develop an interface for this communication and a software tool for testing it

- Develop a software tool for training, analyzing, and connecting to the neural network

- Develop a Tic-Tac-Toe application for testing the correctness of the automated move selector

- Prove efficiency improvement of the hardware design

- Prove correctness through comparing functionality to a sequential neural network

### 1.3.1 Parallel Neural Network Design

A parallel computation device will be designed for calculating NN outputs. Modern processors execute instructions in sequence; therefore, a new hardware computation device designed to execute a NN calculations in parallel will improve upon the efficiency.

The hardware neural network must be designed to take advantage of the parallel neural network structure, while still producing the correct outputs. It must read inputs from an external device, and then send back the output. The hardware neural network must also be able to load neural networks from an external device. This allows the neural network weights to be changed without requiring redesign. This neural network must connect to a software application through an interface.

### **1.3.2 Software Evaluation Tool**

The hardware parallel NN must have means for external devices to perform testing and evaluating operations on it. The neural network can be controlled from a personal computer through an interface. This enables the hardware to be used in software applications which provides flexibility. A software application can choose its own method for offline training while still taking advantage of the online parallel efficiency. Also, by having a common interface, any custom software application can use the parallel nature of the hardware device.

A graphical Tic-Tac-Toe application must be developed to effectively demonstrate the correctness of the neural network. This interface must display the game, record and show statistics about the performance of the move selector, and allow users to make moves or initiate automated moves.

Another graphical interface must also be developed in order to test, analyze and control the hardware neural network. This interface must allow users to open and save neural network configurations, and allow users to upload them to a hardware NN. The interface must also allow users to train the neural network to fit a given set of training data, while displaying statistics of its current progress. These features provide the necessary actions for testing, analyzing, and controlling the hardware neural network.

Lastly, a software NN must be developed in order to verify the correctness of the hardware NN. This software NN must have the same software interface as the hardware NN driver so that the training application does not need to know whether it is talking to hardware or to software. In this way, the evaluation can be determined in precisely the same manner for both NN's.

## 1.3.3 Verify Parallel System Efficiency and Correctness

The output of the parallel neural network and the output of the sequential neural network must be proven equivalent. The efficiency improvement of the parallel neural network must also be verified. If the efficiency component of a parallel computation device does not improve upon the efficiency of its sequential counterpart, then manufacturing such a device would be useless. Likewise, the parallel system would be useless if it does not produce correct results. These cases are not desirable.

The number of sequential additions and multiplications must be calculated for both the parallel and sequential neural network algorithms. This proves that the parallel neural network operates more efficiently than the sequential neural network, verifying that the project intent is met. The correctness of the neural network output must also be verified. This is proven by comparing the hardware NN output with a sufficient number of input, output pairs used in a working software NN. The training data is chosen from the set of correct Tic-Tac-Toe moves and the network's convergence on this data set is demonstrated through using the Tic-Tac-Toe application.

# 2 Design

# 2.1 General System

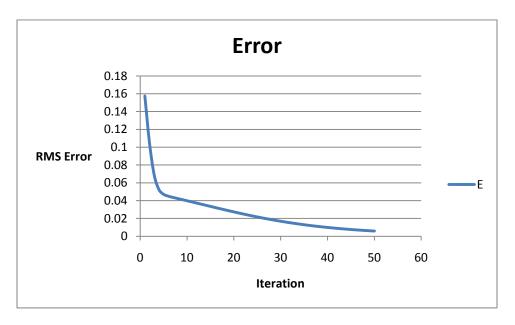

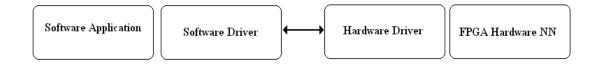

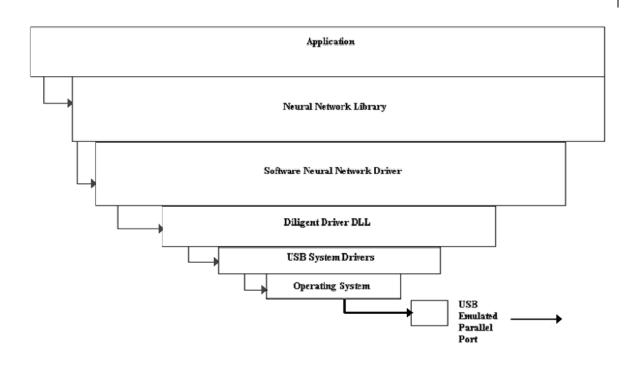

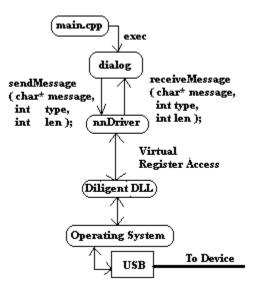

Figure 10 shows the general system diagram of our project. Our main processor unit is an average Windows PC which runs the Trainer, Analyzer, Controller (TAC) and the software driver. We also designed the neural network logic for the Xilinx Virtex-6 DSP FPGA and the hardware driver for the Diligent Nexys 2 FPGA development board. The TAC communicates over USB through the software and hardware drivers to send and receive messages from the hardware neural network.

### 2.1.1 TAC

The Trainer, Analyzer, Controller is a tool meant to aid neural network developers. Some of the tasks the TAC can do are create, open, save, edit, and view a neural network on the computer. Other tasks include the ability to batch test and train the neural network as well as view the results from these processes.

Finally, a developer can connect to an external device with the TAC and use the neural network in a particular application. The structure of the neural network, testing and training processes, and external device adapters and applications can all be developed as plug-ins for the TAC to make the program extensible. A device is external to the TAC's core components such as our FPGA. Devices implement a neural network service that can be recognized by the developer's adapters such as TTTDevice. Although devices like our FPGA are meant to be external to a computer they do not have to be. A developer could very well write a device adapter for a software component.

The software neural network shown in Figure 10 has all of the testing, training, editing, viewing, opening, and saving performed on it by the TAC. The structure of this neural network can be extended by a developer to suit their application as long as the neural network remains a fully-connected, layered neural network. However, the neural network also must be used in an external device.

The user can store and load weights between the external device and the software neural network. Loading the weights from the device will allow the user to view, edit, test, train, save, and open that particular neural network in software. Storing the weights to the device allows the user to use the software neural network on the device with the device's application. Each device is required to provide an application view to the TAC so that the user can interact with the external device.

The external device that our program uses is TTTDevice seen in Figure 10. This device provides to the TAC a Tic Tac Toe application which knows how to use the external device to select moves. Although TTTDevice is part of the TAC, it serves as an adapter to an external device and is in turn thought of as a class that is external to the TAC. When discussing the software portion of the project, this adapter is sometimes referred to as the external device or as the device.

The external device knows how to communicate to the software driver developed in the project. Through this, TTTDevice is able to evaluate board positions and intelligently select moves for Tic Tac Toe. In short, TTTDevice is an adapter for the hardware neural network; a Tic Tac Toe user interface; and an automated move selector for Tic Tac Toe. Any other external device is required to implement these specific functions as well. Developing neural network plug-in models for the TAC like Tic Tac Toe is discussed later in the TAC's section.

# 2.1.2 Software Driver

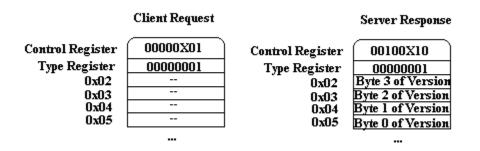

The software driver uses Diligent's libraries to communicate over USB to the Nexys 2 development board. The software driver is intended to be used as a dynamic-linked library (\*.dll) in software applications such as the TAC. Not shown in the diagram is a driver test user interface, which also uses the software driver for testing both the hardware and software drivers. The message, communication, and register protocols are discussed in the driver section.

# 2.1.3 Hardware Driver

The hardware driver is developed in Xilinx ISE to be synthesized for the Spartan 3E FPGA. This is the FPGA that the Diligent Nexys 2 development board uses. The main hardware driver message switch has been developed to be able to send and receive messages through Diligent's emulated parallel port (EPP)

communication protocol. This protocol allows the software driver the ability to use Diligent's libraries in order to establish connection to the FPGA through USB. This driver has been implemented and deployed on the FPGA and functionality has been tested through the use of the driver test user interface on the computer.

# 2.1.4 Hardware NN

The design of the hardware neural network has been developed in Xilinx ISE to be synthesized for the Virtex-6 FPGA. The actual FPGA was not obtained and therefore all testing of the design was done through software simulation using ISE's test benches. The reason for using this board over the board used for the hardware driver is because we needed an FPGA with a greater number of block RAM for the nodes' activation function and a greater number of block multipliers.

The Spartan 3E simply did not contain enough internal block hardware and logic gates to satisfy the requirements. The hardware driver was already developed for the Spartan 3E when this limitation was realized, and there was not enough time to port the driver to the new FPGA. Logically the design should be identical on either board so the goal of producing hardware designs is still satisfied for the hardware driver.

# 2.2 Trainer, Analyzer, Controller

The Trainer, Analyzer, Controller (TAC) is an application that allows users to create their own neural networks locally or using an external device. This application is written in C++ and uses the LGPL version of the Qt 4.6.1 library<sup>1</sup>. The TAC satisfies several goals of our project. These include: develop testing and training methods for a software neural network; train and test the neural network to make it play our example application; and allow the neural network to be used in the TAC through an external hardware neural network device. The requirements that this application must follow in order to satisfy these goals are:

# Requirements

- Users can view the layers, nodes, and weights of the loaded neural network so that they can view the neural network and validate its data.

- Users can expand layers of the neural network to view the layer's nodes and click on the nodes to view a list of its output connections.

- Users can open and save a neural network to and from a file so that they can retrieve a configuration.

- Users can randomize the weights of a neural network or create a new neural network so that they can start off fresh.

- Users can open training data from a file so that they can batch train the neural network.

- Users can open test data from a file so that they can batch test the neural network.

- Users can start and stop a batch training session so that the neural network can learn.

- Users can start and stop a test session so that they can test the neural network.

<sup>&</sup>lt;sup>1</sup> http://qt.nokia.com/products/library

- Users can set training options so that the training cycle can be customized.

- Users can set testing options so that the test cycle can be customized.

- Users can observe the output of testing and training cycles as well as view the results graphically.

- Users can connect the application to an external neural network device so that they may use the neural network in an application.

- Users can store and load weights to and from the external device so that the two neural networks may be synched.

- Users can use an external device in the application so that they can test the actual functionality of the neural network.

- Developers can program their own type of neural network with its own configuration so that it may be used by users of the TAC.

- Developers can program their own testing and training methods so that the user may choose to use these options.

- Developers can program their own external device and application so that the neural network may be used for their particular application.

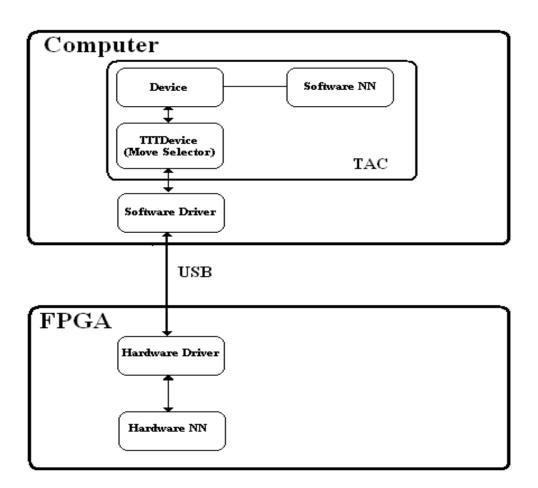

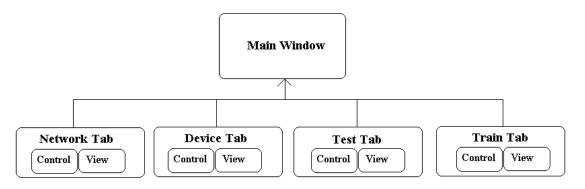

The TAC user interface is broken up into four tabs, as seen in Figure 11, each with their own controls and view. The menu bar is connected to the appropriate controls for each tab and the actual tabs provide the view, as seen in Figure 11. All of these classes are connected together through the MainWindow class. However this connection is trivial and therefore the design of which is not significant. The design of interest lies around the tabs.

The TAC requires that developers program their own services for performing several functions in the program. Therefore, the TAC's main design is based around a simple plug-in framework. The class of interest here is the ServiceLocator which can be extended by a developer who wishes to provide his or her services. The ServiceLocator is the way in which core components of the TAC can locate custom classes provided from an extended version of the TAC. This allows developers to extend the TAC

to provide support for new types of neural networks without changing the core components. A detailed description on ServiceLocator and how this process works can be found in section Error! Reference source not found.

### Figure 12 - TabView

The TabView class is an abstract class that all tabs implement. This class provides the constructs for the view of each tab. The view provides a simple splitter for a main view and for a support view on the left, as seen in Figure 12. These two views can be set and updated by its child classes. TabView also provides some constructs for interfacing with MainWindow which includes providing functionality for getting information for the status bar and posting updates to the status bar.

# 2.2.1 Network Tab

The network tab allows a user the ability to be able to create, open, and save a neural network. Neural networks are contained in neural network (\*.nn) files. Specification of this file type can be found in section **Error! Reference source not found.** Each file contains the version of its stored NNand also the weights for each of the NN's connections. The version is used by the TAC to determine which neural network structure is stored in the file; the only version implemented in our project represents the Tic-Tac-Toe neural network. A developer must provide a unique id for each neural network he adds to the application. Therefore, the neural network files effectively contain the unique structure and memory of the neural network. The user also has the ability to randomize the weights of the loaded neural network

through these controls. Finally, the user can graphically view the layers of the neural network; view a layer's neurons; and a neuron's outbound connections. The user also has the option of manually setting the weights in the neuron's outbound connections.

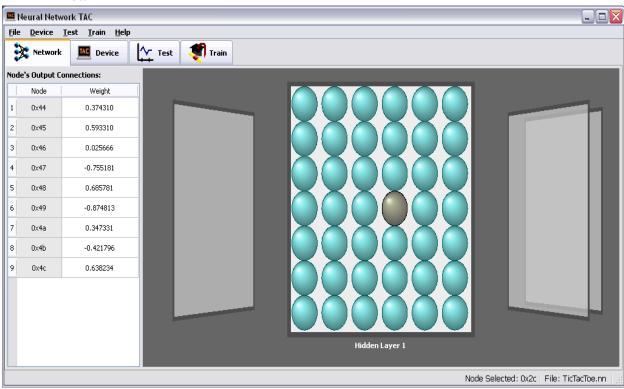

### 2.2.1.1 View

The main view of the Network Tab is a graphical representation of the neural network. Every layer of the neural network is shown in this view. Layers may be rotated through by clicking on the slides to the left and right of the current layer. The current layer in Figure 13 is called "Hidden Layer 1" and contains 48 neurons. The neurons contained within this layer are the blue orbs seen. A neuron, when it is clicked, changes its color to black in order to indicate that it has been selected. Figure 13 shows a selected neuron in the fourth row and fourth column of the neuron grid.

The support view on the left in the Network Tab is a table containing all of the output connections for the selected node. That is the table will display the node identifiers of all the neurons that the current neuron is connected to through its outputs. The only neural network allowed at the moment is a feed-forward, fully connected, layered network and therefore all of the nodes in the same layer will connect to the all of the nodes in the next layer through their output connections. The weights along these connections can be changed in the table by double clicking the weight and typing a new value.

### 2.2.1.2 Controls

| New<br>Open<br>Save<br>Save As | Ctrl+N<br>Ctrl+O<br>Ctrl+S |

|--------------------------------|----------------------------|

| Randomi:                       | ze                         |

| Exit                           | Alt+F4                     |

Figure 14 - Network Tab Controls (Under "File" menu)

The menu bar contains the controls for all of the tabs. The controls for the Network Tab are contained under File. This is because the main propose of the Network Tab is to open, save, and create a neural network. All of these actions are typically under the "File" menu, as seen in Figure 14, and therefore is named as such so that the user will not have much difficulty finding them. It should be noted that a neural network must be opened into the TAC before any other operations can take place. Therefore everything will be grayed out and disabled until the user does this.

The Open, Save, and Save As actions work the same as any other application. These actions all open the standard file dialog of the operating system and look for "\*.nn" files. The appropriate plugin is chosen from the ServiceLocator to create the neural network when Opening it. The appropriate plug-in is determined by finding the ServiceLocator with the same identifier as the one in the neural network file. Each different plug-in knows the structure of its neural network. The plug-in constructs a neural network with this structure and initializes it to the weights found in the neural network file. Finally, this constructed neural network is loaded into the TAC as the current software neural network. However, the \*.nn file does not change between versions of neural networks so that writing to the file is the same process for every version. Therefore the writer does not need a service in order to produce the file. The specification of the \*.nn file is shown in section **Error! Reference source not found.**.

| 💻 New Neural Network 🛛 🔹 🔀               |  |

|------------------------------------------|--|

| Please select the type of neural network |  |

| Tic tac toe (19->48->9->1) 💌             |  |

| OK Cancel                                |  |

Figure 15 – New Neural Network Dialog

The New action in the File menu opens a dialog shown in Figure 15. This dialog lists all of the types of neural networks that the developers have added to the application. The user may select his or her preference and open a new neural network of that type. The numbers shown in Figure 15 refer to the configuration of the neural network. The configuration shown means the Tic Tac Toe neural network will have 19 nodes in its input layer, 48 nodes in its first hidden layer, 9 nodes in its second hidden layer, and finally 1 node in its output layer.

The Randomize action will take the software neural network that is loaded into the TAC and randomize all of its weights. This allows the user to possibly restart the neural network to an initialized condition in case the training session was not favorable. Typically, the output error of a neural network converges to a local minimum during training. Randomizing the weights and starting again will help in this situation. Randomizing the weights of the neural network effectively clears the neural network's memory.

## 2.2.2 Device Tab

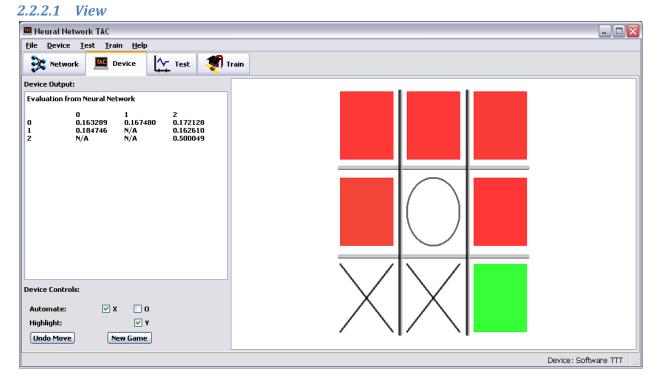

The device tab allows the user the ability to use the hardware neural network loaded into the TAC in an example application. The external device which runs the neural network used in the application can be chosen through the device options. The user has the ability to load and save the weights from the current software neural network to the device's hardware neural network. The view allows the user the ability to view device output as well as interact with the application to which the device is attached, such as Tic-Tac-Toe. This tab requires the most services from a developer as the entire application and device must be provided.

### Figure 16 – Device Tab View

Figure 16 shows the view for the device tab. This example view shows the TAC playing the Tic-Tac-Toe device application. Device applications can choose what inputs to load to the external device and how to interpret the results. In fact, this entire process is done externally from the TAC. All the TAC knows is that a device is connected and is being displayed. All of the logic of the application must be provided by the developer of the device. The process of how to develop for the TAC is described in section **Error! Reference source not found.**

### 2.2.2.2 Controls

Figure 17 – "Device" Options Menu

The TAC allows for devices and their applications to be very generic so that a broad range of applications can be written for them. Therefore, there are only a few and simple controls that can relate to every device and its view. There exists a neural network in the memory of the TAC whenever one is loaded from the File menu. This neural network may contain different weights than what is on the external device. Therefore we wish the ability to store the weights to the device so that the device may be used by the application. Also we wish to be able to load the weights from the device so that we may use them for viewing, testing, and training using the other tabs. These options may be chosen from the "Device" menu, as seen in Figure 17.

| 💻 Device Op   | otions         | ? 🔀       |

|---------------|----------------|-----------|

| Select Device | Software TTT 💌 | Configure |

|               | ОК             | Cancel    |

We must also have the ability to first select the device we wish to use. The device options action in the menu spawns the device options dialog shown in Figure 18. This options box is populated with all of the loaded devices in the current ServiceLocator that the developer provided. Each time a neural network is loaded, a service locator for that version type is found. Each service locator provides its own devices. Therefore, only devices that are compatible with the currently loaded neural network will show up.

If the developer so chooses, he or she can specify a configuration dialog for which additional options may be set for the currently select device. These options should be connection specific such as timeout or port used. Once the device is selected, the Device Controller queries the device for its application and then the Device View displays this application in the Device Tab's main view. All devices are required to produce an application view that utilizes the device. In the case of our project, the "Software TTT" device produces the Tic Tac Toe user interface that gets displayed in the Device Tab's main view. All other logic is then handled by the device's application until another device is connected to or the current device has lost its connection.

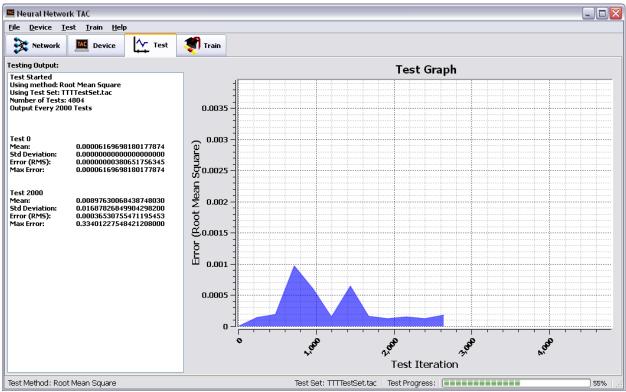

### 2.2.3 Test Tab

The test tab allows the user the ability to load a test file and to initiate various tests to determine the error of the NN loaded into the TAC. The user may also terminate the testing operation at any time as

well as view its progress and the results. Test files (\*.tac) contain a series of test sets which are basically a series of inputs to the neural network and their expected results. The specification for this file type is provided in section **Error! Reference source not found.**. The typical usage of this tab is to determine the quality of performance of the loaded neural network. The developer may choose his or her own testing methods as well as graphically display any statistical information. The output of the testing procedure is also determined by the method chosen.

## 2.2.3.1 View

### Figure 19 – Test Tab View

The main view of the Test Tab is the graph as seen in Figure 19. This graph is updated by the testing method chosen and displays whatever information the method wishes. The scale and labels on the left axis are also fully provided by the test method in question. In the case of the "Root, Mean, Square" method, the graph displays the RMS for every test in the test set. It should be noted that the graph expects large test sets typically containing thousands of data points and therefore separates the test sets into several bins, averaging all of the content in each bin to get the data point. The x-axis is linked to how many tests the loaded test set contains and cannot be changed by the testing method. The graph's interface uses mouse controls to zoom and pan the graph. Scrolling the mouse wheel up and down zooms in and out of the graph; clicking and dragging the graph pulls the graph with the cursor; clicking and dragging the middle mouse button, which on a modern mouse this action requires clicking the

mouse wheel, drags the graph with the mouse The rendering software for the graph is provided in a third party library called Qwt<sup>2</sup>.

The support view of the Test Tab contains the output of the test method. The test method is a method extended by a subclass of the test thread. The test method takes in the expected outputs and actual outputs of the neural network and returns the result of the test. This value is typically used as a type of error value such as root mean square. The test method is queried by the run method in the test thread's base class every so often to provide stats to the test view. Figure 19 displays the statistics for all of the tests up to the current test iteration in the output. The number of iterations that the view displays the stats can be configured in test options.

## 2.2.3.2 Controls

| Open Test Set<br>Start Testing |

|--------------------------------|

| Stop Testing                   |

| Testing Options                |

Figure 20 – "Test" Options Menu

The act of testing does not require many controls; these few controls can be selected from the "Test" menu, seen in Figure 20. A user can open a test set which loads in a .tac file of their choosing. This file contains a series of inputs and expected outputs that describe the behavior that the neural network should exhibit. These data points are used during testing. The "Start Testing" menu option in the "Test" menu starts the test thread. This thread takes all of the inputs from the data file and feeds them into the TAC's loaded software NN one by one. Each output is then compared to the expected output and an error is calculated by the testing method provided by the developer. Afterwards, that error and statistics are posted to the view. This cycle can be stopped at any time by choosing the "Stop Testing" menu item from the "Test" menu.

| 💻 Testing Options      | ? 🔀              |

|------------------------|------------------|

| Error Determination    | Root Mean Square |

| Output Every Iteration | 2000             |

|                        | OK Cancel        |

Figure 21 – Testing Options Dialog

The "Testing Options" dialog, seen in Figure 21, allows the user to choose the testing method. It also allows them to choose how many cycles to skip before outputting another statistic. Figure 21 shows that the user has selected "Root Mean Square" as the testing method and for the console to display testing

<sup>&</sup>lt;sup>2</sup> http://qwt.sourceforge.net/

information once every 2000 iterations over the test data. Testing methods are provided by a developer and are all displayed in this dialog. Remember that each neural network version has its own subclass of ServiceLocator to provide the application with the services for that neural network. A testing method does not have to be neural network specific but it must be added to every ServiceLocator of every type of neural network that wishes to use it. This is to allow the flexibility that some versions might not wish to have certain methods and allows for the possibility that the methods can be version specific.

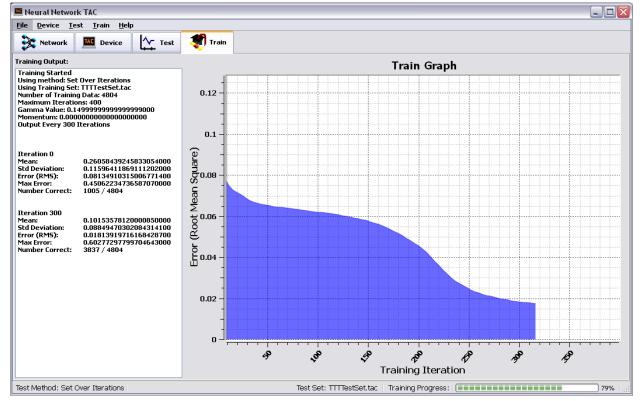

# 2.2.4 Train Tab

The "Train" tab allows the ability to make the neural network more intelligent. This is done by allowing the user to open a neural network data file (\*.tac) and initiate a training session. The user can also stop the training session as well as configure options for a training session. Finally a user also has the ability to view the training session's progress and results. The typical usage of this tab is to train the neural network for a specific application as described by the data file. The data file's specification is described in section **Error! Reference source not found.**. The developer may choose his own training methods as well as display graphically any statistical information he wants. The output of the training procedure is also determined by the method chosen.

## 2.2.4.1 View

The main view of the Train Tab is the graph as seen in Figure 22. This graph is updated by the training method chosen and displays whatever information the method wishes. The scale and labels on the left

axis are also fully provided by the training method in question. In the case of the "Set Over Iterations" method, the graph displays the RMS of the entire neural network after each iteration of training. It should be noted that the graph expects a large number of training iterations and therefore separates the training iterations into several bins, averaging all of the content in each bin to get the data point. The x-axis is linked to however many iterations the user wishes to display. This graph's interface also uses mouse controls to zoom and pan the graph. The rendering software for the graph is provided in a third party library called Qwt.

The support view of the Train Tab contains the output of the training method. The training method is queried by the training engine every so often to provide stats. These statistics can be anything required by the training method. The number of iterations between each output of the statistics can be configured in the "Test Options" dialog.

### 2.2.4.2 Controls

Figure 23 – "Train" Options Menu

Training does not require many controls as seen in the "Train" menu in Figure 23. A user can open a training set which loads in a .tac file of their choosing. This file contains a series of inputs and expected outputs that describe the behavior that the neural network should exhibit. These data points will be used when training has begun. The "Start Training" starts the training engine. The training process used by the training engine is fully provided by the train method, which is provided by the developer. The method can post updates to the view at any time and stops when the maximum number of training iterations has been completed. However, the cycle can be stopped at any time by choosing the "Stop Training" menu item from the "Train" menu.

| 💻 Training Options     | ? 🔀                 |

|------------------------|---------------------|

| Training Method        | Set Over Iterations |

| Output Every Iteration | 300                 |

| Max Iterations         | 400                 |

| Gamma                  | 0.150000            |

| Momentum               | 0.000000            |

|                        | OK Cancel           |

Figure 24 – Training Options Dialog

The "Training Options" dialog, shown in Figure 24, allows the user to choose the training method. It also allows the user to choose how many cycles to skip before outputting another statistic. Also, the user can provide the total iterations he or she wishes to perform on the neural network as well as set some of the training constants such as gamma or momentum. Gamma is the learning rate constant described in section **Error! Reference source not found.** Momentum is a constant in a modified weight update rule. This constant is multiplied by the last weight update used and then added to the new weight update. All this constant is used for is to help the weight's error optimization to not become stuck in a local minimum. Figure 24 shows that the user has selected "Set Over Iterations" as the testing method and for the training statistics to be outputted to the console every 300 iterations. Testing will go on for 400 iterations and will use 0.15 as gamma and 0.0 as momentum.

The training methods are provided by a developer and are all displayed in this dialog. Remember, that each neural network version has its own subclass of ServiceLocator to provide the application with the services for that neural network. A training method does not have to be neural network specific but it must be added to every ServiceLocator of every type of neural network that wishes to use it. This is to allow the flexibility that some versions might not wish to have certain methods and allows for the possibility that the methods can be version specific.

## 2.2.5 Developing for TAC

This section briefly covers the steps and significant classes required to implement new neural networks for the TAC. The TAC implements a simple plug-in architecture centered on the ServiceLocator class. Any client program that derives from the TAC can use this simple architecture to change the types of neural networks that it can support without changing any of the TAC's core components. In fact, only a little bit of knowledge of the core components is needed in order to extend this functionality. Extendable components include the types of neural networks, testing and training methods, and finally external devices and their applications.

Client developers extend several external class components to provide this extended functionality. They also extend ServiceLocator itself to return the extended components when asked. Each subclass of ServiceLocator must provide a unique version id to show which type of neural network it is compatible with. This version number is used in every file and device to determine compatibility and to identify the appropriate components. Finally, the subclass of ServiceLocator must be loaded into ServiceLocator itself in order for the application to see the extension.

```

int main(int argc, char *argv[])

£

QApplication app(argc, argv);

srand(time(NULL));

/* Set up providers for application */

DeviceProvider* deviceProvider = new DeviceProvider();

deviceProvider->load(new TTTDeviceSW());

TestProvider* testProvider = new TestProvider();

testProvider->load(new RMSTester());

testProvider->load(new WLDTester());

TrainerProvider* trainerProvider = new TrainerProvider();

trainerProvider->load(new SOITrainer());

/* Set up service locator */

TTTServiceLocator* myServiceLocator = new TTTServiceLocator();

myServiceLocator->setDeviceProvider(deviceProvider);

myServiceLocator->setTestProvider(testProvider);

myServiceLocator->setTrainerProvider(trainerProvider);

ServiceLocator::load (myServiceLocator);

MainWindow wind;

wind.show();

return app.exec();

}

```

### Figure 25 - Tic Tac Toe Client Implementation

Figure 25 shows the main method of our project. This shows all that is required for the developer to do in order for the TAC to provide all of the functionality for custom neural networks. The above is all that has been required for the TAC to support our Tic Tac Toe neural network. The actual classes and methods for extending everything is documented in the following sections.

### 2.2.5.1 ServiceLocator

The ServiceLocator class is at the heart of the simple plug-in system that the TAC implements. The first step in providing a new neural network type is to subclass the ServiceLocator. Subclassing this class involves overriding the methods that follow.

```

virtual NNFactory* LocateNNFactory();

virtual DeviceProvider* LocateDeviceProvider();

virtual TestProvider* LocateTestProvider();

virtual TrainerProvider* LocateTrainerProvider();

virtual int getVersion();

virtual char* toString();

```

The previous methods must be overridden to locate the appropriate classes for the application when requested. If this is done then the TAC will be able to successfully integrate all of the features that a new type of neural network has to offer. Details about the returned classes from the locator methods will follow later in this section.

The getVersion method must return the type of neural network this ServiceLocator belongs to. All of the neural network files and data files that this ServiceLocator can handle must implement the same version number. Two different types of neural networks must not return the same version number or incompatibilities may occur.

The toString method must return an identifier string so that a human can identify if this neural network type is the type that he or she wants. Specifically, this is mostly used in the drop down box of the "New Neural Network Dialog" seen in Figure 15. Naming the type of neural network should have something to do with its use: such as "Tic-Tac-Toe" or "Battleship."

# 2.2.5.2 NNFactory

The NNFactory class allows the creation of a particular type of neural network. Whenever a neural network is opened it needs to be created in memory. This builds a representation of the specific type of neural network (NNApprox class) that the file version has asked for. This class is meant to be subclassed and should override the method that follows.

```

virtual NNApprox* build(double* weights, int length);

```

The previous method is the only method that's required to be overridden. This method takes in an array of weights and the total number of weights and returns the specific type of neural network that this class builds. The type of neural network that this class builds should be the same as the ServiceLocator it belongs to. An example for the Tic Tac Toe application follows in Figure 26.

```

/**

* Matthew Netsch

Feb 2010

* TTTFactory.cpp

* Implements a Neural Network Factory.

* Constructs a tic tac toe neural network.

*/

#include "TTTFactory.h"

/* Creates the neural network */

NNApprox* TTTFactory::build(double* weights, int length)

Ł

/* Creates the neural network approximator */

NNApprox* approx = new TTTApprox();

approx->store_weights(weights, length);

return approx;

}

```

Figure 26 – TTTFactory.h – A subclass of NNFactory

### 2.2.5.3 NNApprox

The NNApprox class is an abstract class that provides access to an underlying neural network. This class must be implemented by a subclass to provide a particular type of neural network. The main purpose of this class is to break out the functionality of the underlying nn class as well as keep track of its configuration. The only method that subclasses need to override follows.

virtual void build();

The previous method builds up the underlying neural network to the configuration that the version type that this subclass implements. The developer must also set the version member variable to the version number that this subclass implements as well. An example for the Tic Tac Toe application follows in Figure 27.

```

/**

* Matthew Netsch

* Feb 2010

* TTTApprox.cpp

* Implements a Neural Network Approximator.

* Builds a neural network that can be used for

* tic tac toe. Registered as Version 2.

*/

#include "TTTApprox.h"

/* Constructor */

TTTApprox::TTTApprox()

£

version = 2;

build();

¥.

/* Builds the neural network for a tic tac toe application */

void TTTApprox::build()

Ł

int numLayers = 4;

int counts[] = {19, 48, 9, 1};

double gamma = 0.1;

double momentum = 0.5;

net = new nn(&(counts[0]), numLayers, gamma, momentum);

}

```

#### Figure 27 – TTTApprox.h – A subclass of NNApprox.h

#### 2.2.5.4 Device Provider

The DeviceProvider class is used by the TAC to retrieve all of the devices that are implemented for the loaded neural network. This class also keeps track of the device's connectivity and alerts the TAC if a device disconnects. However, although it is possible to subclass DeviceProvider, that is not the typical usage of this class. Typically the developer would load his or her NNDevice classes into a new DeviceProvider instance. The developer would then load this provider into his or her ServiceLocator instance so that it could be returned when requested by the TAC. The same situation applies for the TestProvider and the TrainerProvider.

#### 2.2.5.5 NNDevice

The NNDevice class is an abstract class that represents a device. This class is meant to be subclassed so that the TAC can interface with a specific device. The methods that require overriding follow.

| virtual | int      | getVersion();                       |

|---------|----------|-------------------------------------|

| virtual | QString* | getName();                          |

| virtual | void     | <pre>load(NNApprox* approx);</pre>  |

| virtual | void     | <pre>store(NNApprox* approx);</pre> |

| virtual | bool     | isConnected();                      |

```

virtual void

testConnection();

virtual void

setConnected(bool connected);

virtual void

configure();

virtual bool

isConfigurable();

virtual void

reload();

virtual double

evaluate(double* inputs, int numInputs);

virtual void

constructViews(NNDevice*

device,

DeviceView**

view, QWidget** controls);

```

- The getVersion method must return the type of neural network this NNDevice belongs to.

- The toString method must return an identifier string so that a human can identify what device this represents.

- The load method stores the weights of the device into the neural network passed into it.

- The store method stores the weights from the neural network passed into it to the device.

- The isConnected method returns the status of the connection.

- The testConnected method tries to ping the external device with a blocking behavior.

- The setConnected method sets the connection status.

- The configure method opens a configuration dialog so that a user may change the connection settings.

- The isConfigurable method returns if the device has a configuration dialog or not.

- The reload method attempts to reinitialize the connection to the external device. This is called when the device has been deemed unconnected.

- The evaluate method gives the inputs to the neural network and returns the result from the device.

- The constructViews method constructs the main view and the support view for the device so that the Device Tab may display the Device's application.

# 2.2.5.6 NNTester

The NNTester class is an abstract class that provides a particular testing method. The TAC uses this method provided from the TestProvider returned from the ServiceLocator class of the loaded neural network. It takes these methods and provides for the user a set of selectable options in order to run a testing session. The methods a subclass must override in order to create a new testing method follow.

virtual QwtScaleDraw\* getScaleDraw();

The getError method takes in the expected output and the outputs of the neural network and returns the error. The error could be whatever the testing method wishes it to be.

The getName method returns a human readable identifier so that the TAC may provide a label for this testing method.

The getStats method returns what is to be printed on the console to the left of the graph in the view. This however is only printed at every iteration that the user has specified in options.

The getScaleName method returns the label of the y-Axis for the graph.

The getScaleDraw method returns the drawing class for the labels on the y-Axis. Please see Qwt documentation on QwtScaleDraw.

#### 2.2.5.7 NNTrainer

The NNTrainer class is an abstract class that provides a particular training method. The TAC uses this method provided from the TrainerProvider returned from the ServiceLocator class of the loaded neural network. It takes these methods and provides for the user a set of selectable options in order to run a training session. The methods a subclass must override in order to create a new training method follow.

| virtual | void          | run();                     |

|---------|---------------|----------------------------|

| virtual | QString*      | getName();                 |

| virtual | QString*      | getStats();                |

| virtual | QString*      | <pre>getScaleName();</pre> |

| virtual | double        | getScaleMax();             |

| virtual | QwtScaleDraw* | <pre>getScaleDraw();</pre> |

The run method is the main method of the trainer. This method should post updates as training cycles are completed.

The getName method returns a human readable identifier so that the TAC may provide a label for this training method.

The getStats method returns what is to be printed on the console to the left of the graph in the view. This however is only printed every iteration that the user has specified in options.

The getScaleName method returns the label of the y-Axis for the graph.

The getScaleDraw method returns the drawing class for the labels on the y-Axis. Please see Qwt documentation on QwtScaleDraw.

### 2.2.6 File Specifications

The file specifications that the TAC uses are as follows.

#### 2.2.6.1 Neural Network File

Format of a neural network (\*.nn) file:

32 bit integer which specifies the version of the neural network 32 bit integer which specifies how many weights follow 64 bit floating point numbers that specifies the weights of the neural network ... ( More weights until the length is satisfied above )

The version integer effectively specifies the structure of the Neural Network, which can be used to interpret the connections that each weight is assigned to. In this way an entire neural network's configuration can be saved and loaded, including its structure and memory.

### 2.2.6.2 TAC Data File

Format of the TAC data (\*.tac) file used in testing and training:

32 bit integer which specifies the version of the neural network

32 bit integer which specifies the number of inputs that follow

64 bit floating point numbers that specifies the inputs of the neural network

... ( More inputs until the length is satisfied above )

64 bit floating point number that specifies the output corresponding to the inputs above

... ( More number of inputs, inputs, and output chunks until end of file )

This file effectively stores input/output pairs which specify the correct behavior of the neural network. This allows for both testing and training the neural network using this data. The algorithms in which it does this are out of the scope of this document.

### 2.3 Parallel Neural Network

The parallel neural network must process a set of inputs and produce an output that is the same as that of the sequential neural network algorithm. This embedded system must take advantage of neural network parallelism to produce an output more efficiently than a sequential processor. The only difference between the inputs and outputs of the parallel and sequential neural networks should be the time taken to calculate them.

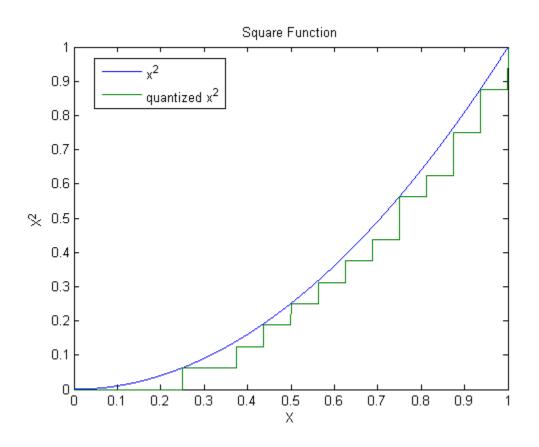

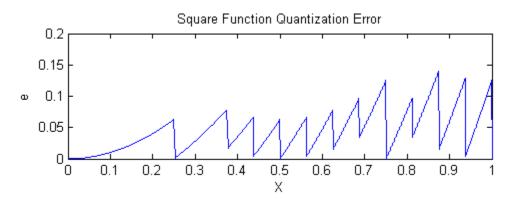

#### 2.3.1 Parallel Structure Analysis

Considering a neural network consisting of multiple fully connected layers of neurons helps identify which parts of the network may be calculated in parallel. It is impossible for each of the sequential layers to calculate an output without having the entire output of its previous layer; therefore, it is impossible to take advantage of any parallelism concerning consecutive layer calculations, limiting the parallel calculation to the neurons within a layer. The parallelism of a layer of neurons is possible because the output of each neuron does not depend on the output of any of the other neurons in the layer. Each neuron must simply iterate over the set of outputs from the previous layer and calculate its output using the neuron output equation:

$$\sigma(x_k) = \frac{1}{1 + e^{-x_k}}$$

$$y_j = \sigma\left(\sum_{i \in inputs(j)} y_i w_{ij}\right)$$

Given that each neuron in a layer has the same number of inputs, this method of parallel neuron calculations will improve the efficiency of each layer by a factor equal to the number of neurons in that layer. For example, a layer containing ten neurons, each with five inputs, must perform the neuron output equation ten times; a sequential algorithm would perform the calculations sequentially ten times—once for each neuron in the layer. Each neuron calculation requires scaling five inputs, resulting in five multiplications. The output calculation also requires summing each scaled input, resulting in four additions. The activated output must then be calculated from the final accumulated sum of scaled inputs. The result for a sequential neural network is:

$$10 \text{ neurons} * 5 \frac{\text{inputs}}{\text{neuron}} * 1 \frac{\text{multiplication}}{\text{input}} = 50 \text{ sequential multiplications}$$

$$10 \text{ neurons} * 4 \frac{\text{additions}}{\text{neuron}} = 40 \text{ sequential additions}$$

$$10 \text{ neurons} * 1 \frac{\text{sigmoid}}{\text{neuron}} = 10 \text{ sequential sigmoids}$$

In contrast, the parallel neural network performs all ten neuron calculations in parallel, giving 5 sequential multiplications, 4 sequential additions, and 1 sigmoid. For this example, the number of sequential calculations is reduced by a factor of ten, which is the number of neurons in the layer.

|                           | Sequential Multiplications | Sequential Additions | Sequential Sigmoids |

|---------------------------|----------------------------|----------------------|---------------------|

| Sequential Neural Network | 50                         | 40                   | 10                  |

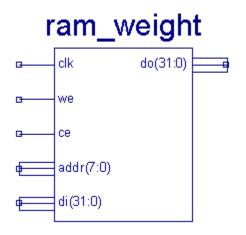

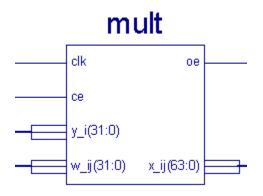

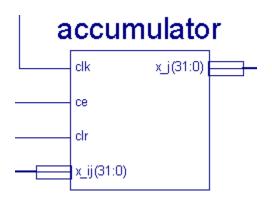

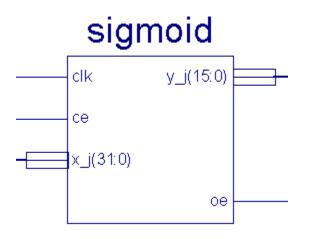

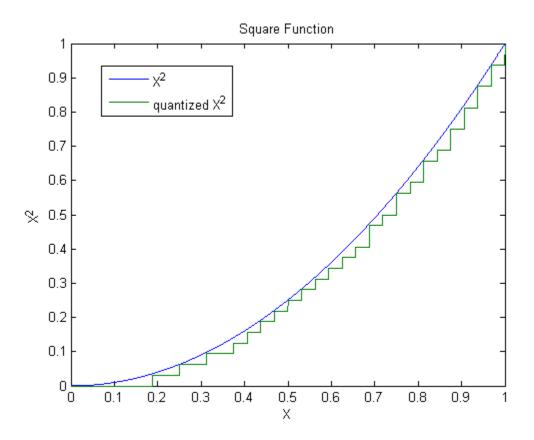

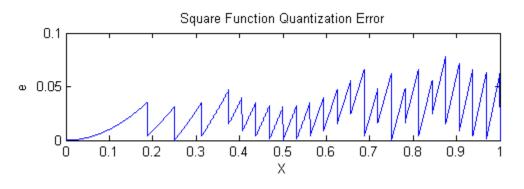

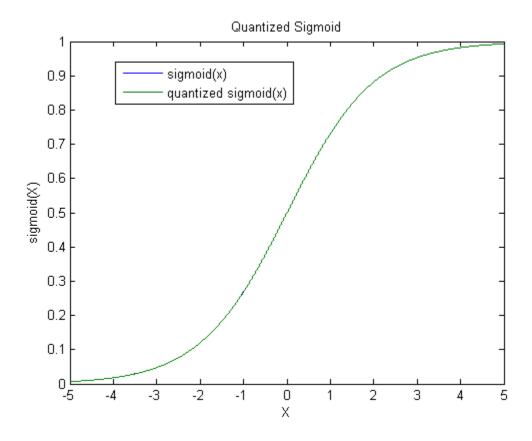

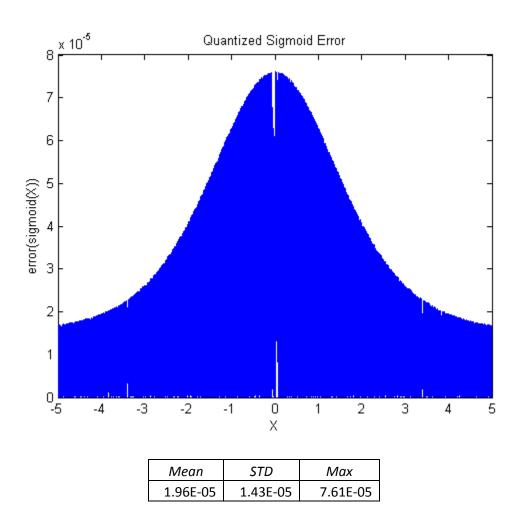

| Parallel Neural Network   | 5                          | 4                    | 1                   |