# Kodiak Electric Vessel MQP

Casey Hayes

Michael Murillo

Jason Rosenman

Christopher Sontag

# Contents

| 1        | Intr | roduction                                                                                                   | 1   |

|----------|------|-------------------------------------------------------------------------------------------------------------|-----|

| <b>2</b> | Bac  | ckground                                                                                                    | 2   |

|          | 2.1  | Kodiak Island and Alaska                                                                                    | 2   |

|          |      | 2.1.1 Alaska                                                                                                |     |

|          |      | 2.1.2 History of Alaska                                                                                     |     |

|          |      | 2.1.3 Alaskan Climate                                                                                       |     |

|          |      | 2.1.4 Kodiak Island                                                                                         |     |

|          | 2.2  | Power Devices                                                                                               |     |

|          |      | 2.2.1 Inverters                                                                                             |     |

|          |      | 2.2.2 Genset                                                                                                |     |

|          |      | 2.2.3 Storage Devices                                                                                       |     |

|          |      | 2.2.4 Insulated Gate Bipolar Transistor                                                                     |     |

|          |      |                                                                                                             |     |

| 3        | Pro  | oblem Statement                                                                                             | 9   |

| 4        | Met  | ethodology                                                                                                  | 11  |

| -        | 4.1  | Original Implementation                                                                                     |     |

|          | 4.2  | Proposed Implementation                                                                                     |     |

|          |      | 4.2.1 Sealed Enclosure                                                                                      |     |

|          |      | 4.2.2 Distributed Layout                                                                                    |     |

|          |      | 4.2.3 Direct-to-Digital Conversion                                                                          |     |

|          |      | 4.2.4 AD/DC Sensor Boards                                                                                   |     |

| -        | D    |                                                                                                             | 1.4 |

| 5        |      | sign Description                                                                                            | 14  |

|          | 5.1  | Voltage Sensing Board                                                                                       |     |

|          | 5.0  | 5.1.1 Schematic of Voltage Sensing Board                                                                    |     |

|          | 5.2  | Current Sensing Board                                                                                       |     |

|          |      | 5.2.1 Description of circuit                                                                                |     |

|          | •    | 5.2.2 Schematic of Circuit                                                                                  |     |

|          | 5.3  | IGBT Driver Link Board                                                                                      |     |

|          | 5.4  | DC Link Capacitor                                                                                           |     |

|          | 5.5  | Flyback Transformer - "Pre-Charge Circuit"                                                                  |     |

|          |      | 5.5.1 LT3750                                                                                                |     |

|          |      | 5.5.2 Voltage Source                                                                                        |     |

|          |      | 5.5.3 Transformer $\ldots$ |     |

|          |      | 5.5.4 Bypass Capacitors                                                                                     |     |

|          |      | 5.5.5 Resistors                                                                                             |     |

|          |      | 5.5.6 FPGA Control                                                                                          | 44  |

|              |     | 5.5.7                                       | Diodes                                                                                                                         | 5 |

|--------------|-----|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---|

|              |     | 5.5.8                                       | MOSFET                                                                                                                         | 5 |

|              |     | 5.5.9                                       | Snubber Circuit                                                                                                                | 3 |

|              |     | 5.5.10                                      | Voltage Divider                                                                                                                | 7 |

|              | 5.6 |                                             | Communications                                                                                                                 | 3 |

|              |     | 5.6.1                                       | Backplane Connectors                                                                                                           |   |

|              |     | 5.6.2                                       | Positive/Negative Side Boards                                                                                                  |   |

|              |     | 0.0.2                                       |                                                                                                                                | ĺ |

| 6            | Res | ults                                        | 50                                                                                                                             | ) |

|              | 6.1 | Voltag                                      | ge Sensing Board                                                                                                               | ) |

|              |     | 6.1.1                                       | Basic Functionality - DC                                                                                                       | ) |

|              |     | 6.1.2                                       | AC Functionality Tests and BODE Plots                                                                                          |   |

|              | 6.2 |                                             | nt Sensing Board                                                                                                               |   |

|              | 0   | 6.2.1                                       | Single Ended Input                                                                                                             |   |

|              |     | 6.2.2                                       | Differential Input                                                                                                             |   |

|              | 6.3 |                                             | harge Circuit                                                                                                                  |   |

|              | 0.0 | 6.3.1                                       | PCB                                                                                                                            |   |

|              |     | 6.3.2                                       | Simulation                                                                                                                     |   |

|              |     | 6.3.2                                       |                                                                                                                                |   |

|              |     | $\begin{array}{c} 0.3.3\\ 6.3.4\end{array}$ | 8                                                                                                                              |   |

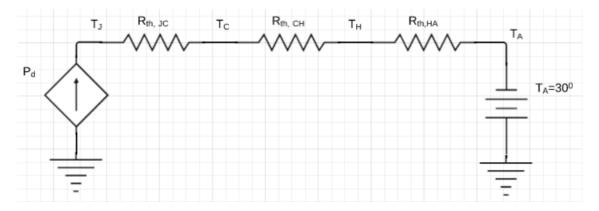

|              |     | 0.3.4                                       | Thermal Modeling                                                                                                               | L |

| 7            | Con | clusio                                      | n & Recommendations 63                                                                                                         | 3 |

| •            | 7.1 |                                             | $mendations \dots \dots$ |   |

|              | 1.1 | 7.1.1                                       | Voltage Sensing   64                                                                                                           |   |

|              |     | 7.1.1<br>7.1.2                              | Current Sensing   64                                                                                                           |   |

|              |     | 7.1.2<br>7.1.3                              | Pre-Charge                                                                                                                     |   |

|              |     | 1.1.0                                       | 11e-Onarge                                                                                                                     | ± |

| $\mathbf{A}$ | Par | ts List                                     | 66                                                                                                                             | 3 |

|              |     |                                             |                                                                                                                                |   |

| В            | Dat | asheet                                      | s 74                                                                                                                           | 1 |

|              | B.1 | ADS83                                       | 364 A/D Converter                                                                                                              | 4 |

|              | B.2 | Voltag                                      | ge Sensing Circuit                                                                                                             | 1 |

|              |     | B.2.1                                       | Potentiometer                                                                                                                  | 1 |

|              |     | B.2.2                                       | AVAGO Opto-Isolator                                                                                                            | 4 |

|              |     | B.2.3                                       | Voltage Regulator                                                                                                              | 4 |

|              |     | B.2.4                                       | DC/DC Converter                                                                                                                | 4 |

|              |     | B.2.5                                       | $1M\Omega$ Resistor                                                                                                            | 4 |

|              | B.3 | Currer                                      | nt Sensing Circuit                                                                                                             | 4 |

|              |     | B.3.1                                       | TAMURA L31S***S05FS Current Sensor                                                                                             | 4 |

|              |     | B.3.2                                       | TAMURA L06P***S05 Current Sensor    75                                                                                         |   |

|              |     | B.3.3                                       | Analog Devices AD8366                                                                                                          |   |

|              |     | B.3.4                                       | $10k\Omega \text{Resistor}$                                                                                                    |   |

|              | B.4 |                                             | ck Transformer                                                                                                                 |   |

|              | D.1 | B.4.1                                       | CT05 Transformer                                                                                                               |   |

|              |     | B.4.1<br>B.4.2                              | LT3750 Capacitor Charge Controller                                                                                             |   |

|              |     | B.4.2<br>B.4.3                              | MBR1645G Diode                                                                                                                 |   |

|              |     | Б.4.3<br>В.4.4                              | IDP30E120 Diode                                                                                                                |   |

|              |     | в.4.4<br>В.4.5                              | IPP114N12N3 OptiMOS 3 Power Transistor MOSFET                                                                                  |   |

|              |     | D43                                         | TEELIANTZINA UDUUVUUA A POWER TRADSISTOR VIUSEET (2                                                                            | J |

|              |     |                                             |                                                                                                                                | - |

|              |     | B.4.6<br>B.4.7                              | Resistors   75     Capacitors   76                                                                                             |   |

|   | B.5  | IGBT    | Platform Board                         | 76 |

|---|------|---------|----------------------------------------|----|

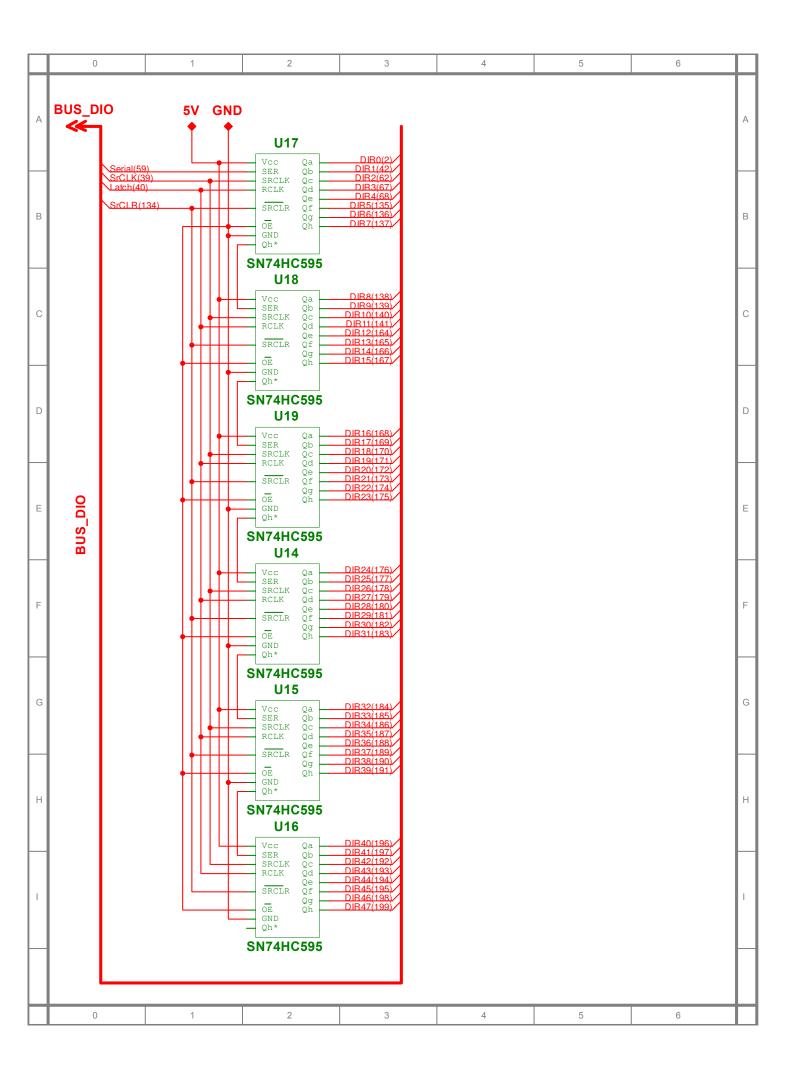

|   |      | B.5.1   | TI SN**LBC170 Differential Transceiver | 76 |

|   |      | B.5.2   | TI SN**HC595 Shift Registers           | 76 |

|   |      | B.5.3   | 100 Ohm Resistor Array                 | 76 |

|   |      | B.5.4   | High Density Connector                 | 76 |

|   |      | B.5.5   | PCIe Connector                         | 76 |

|   |      | B.5.6   | Molex HD Mezz Plug                     | 76 |

| С | Inve | erter E | Block Diagram                          | 77 |

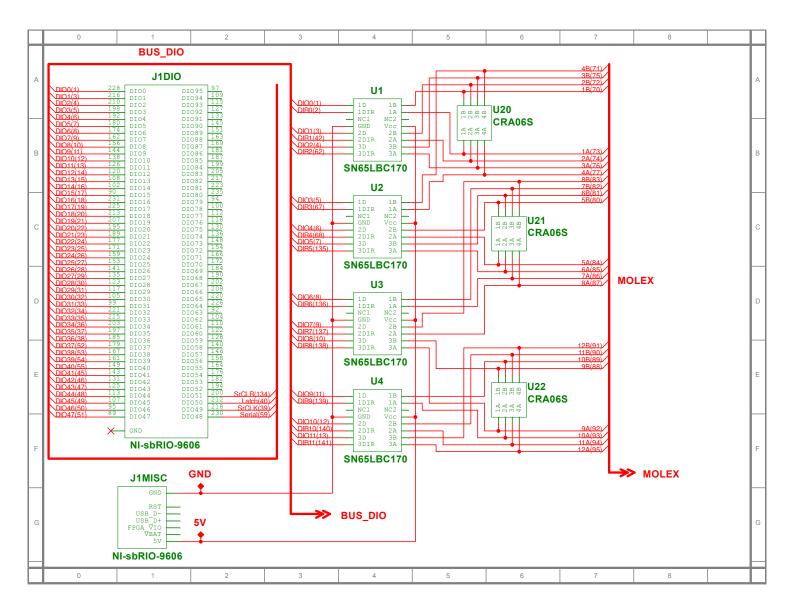

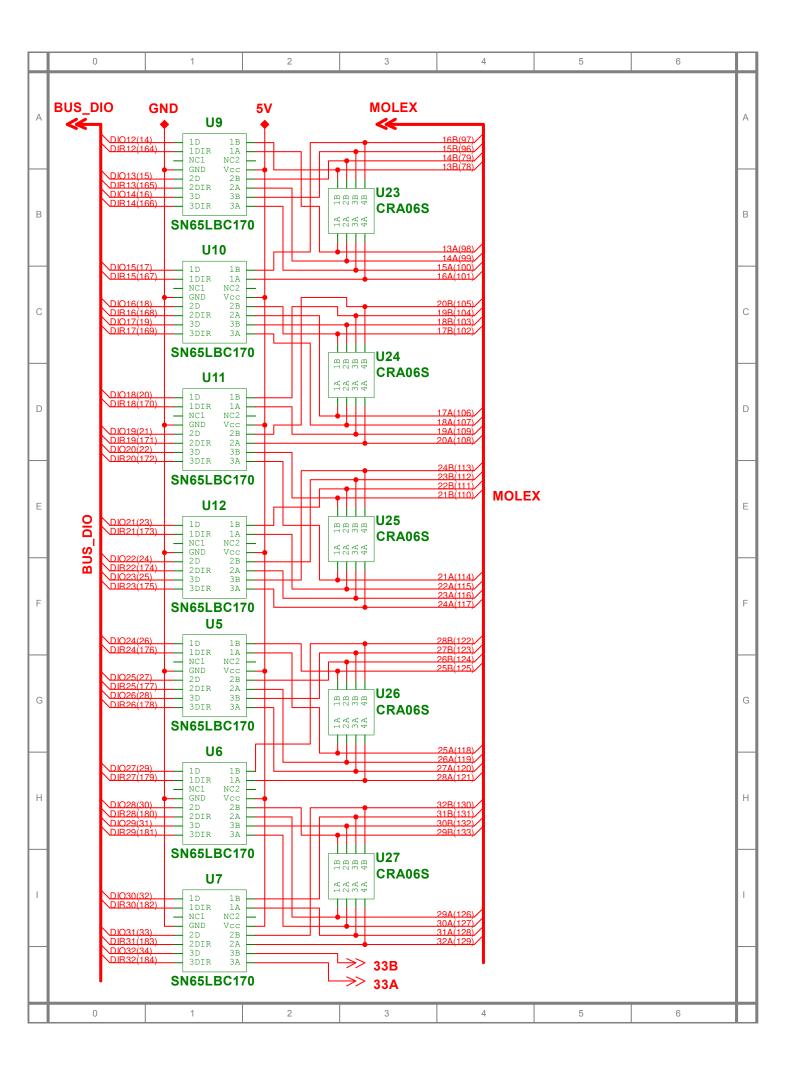

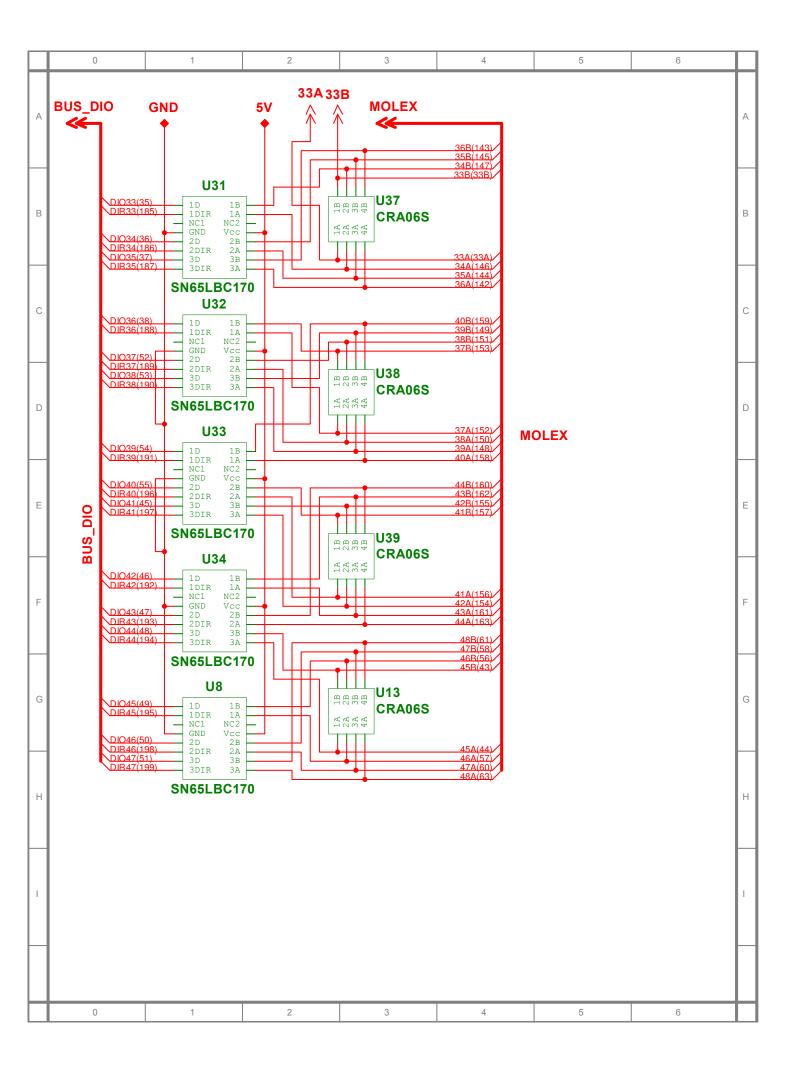

| D | IGE  | BT Pla  | tform Board Schematic                  | 79 |

# List of Figures

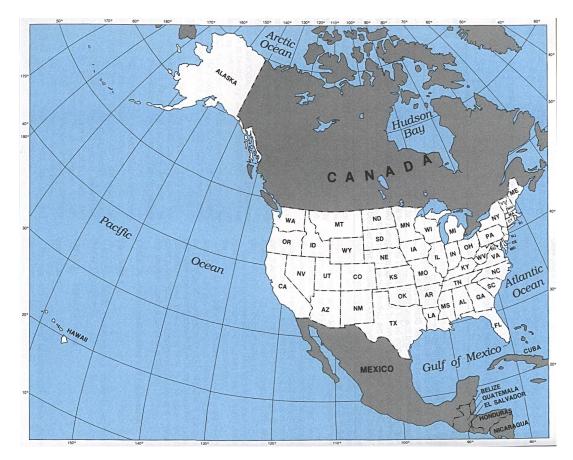

| 2.1  | Map of North America                                                                           | 3  |

|------|------------------------------------------------------------------------------------------------|----|

| 2.2  | Climate Regions of Alaska                                                                      | 4  |

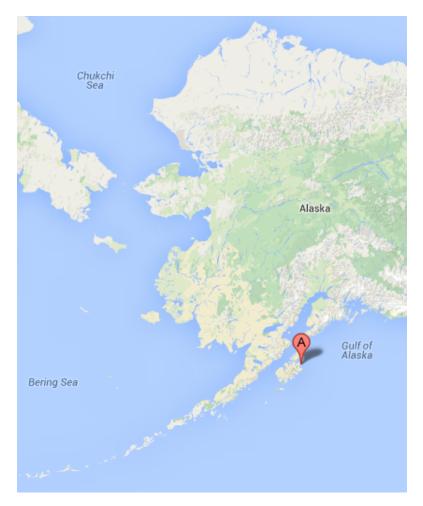

| 2.3  | Map of Alaska, with Kodiak Island                                                              | 5  |

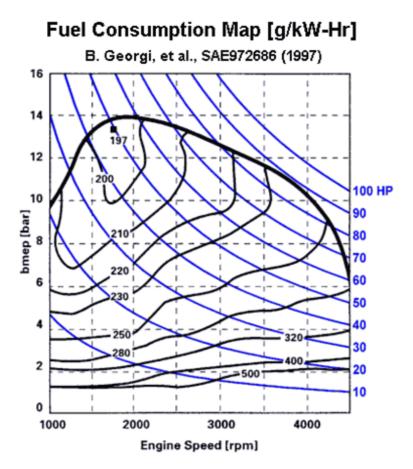

| 2.4  | Diesel Efficiency Map                                                                          | 6  |

| 2.5  | Control Flow Diagram                                                                           | 7  |

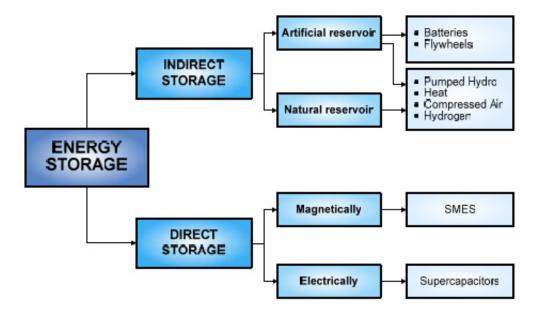

| 2.6  | Tree Diagram of Energy Storage options                                                         | 7  |

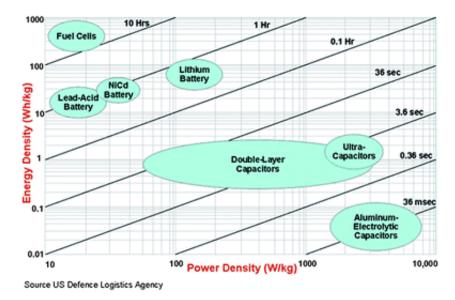

| 2.7  | Ragone Chart comparing storage devices                                                         | 8  |

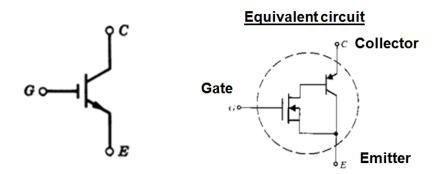

| 2.8  | IGBT circuit symbol                                                                            | 8  |

| 2.9  | IGBT I-V characteristic                                                                        | 8  |

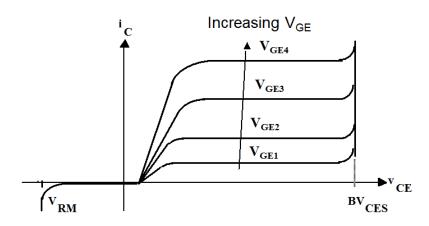

| 4.1  | CAD Model of Sealed Enclosure                                                                  | 12 |

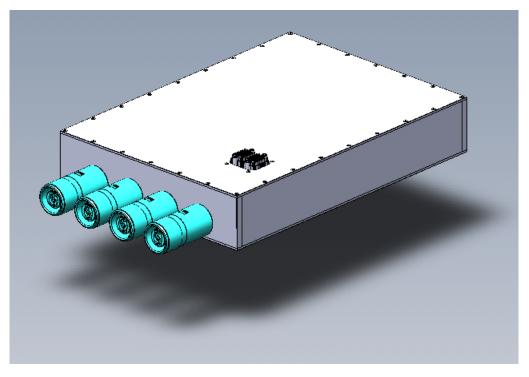

| 5.1  | 3D rendering of the inverter without the enclosure $\ldots \ldots \ldots \ldots \ldots \ldots$ | 14 |

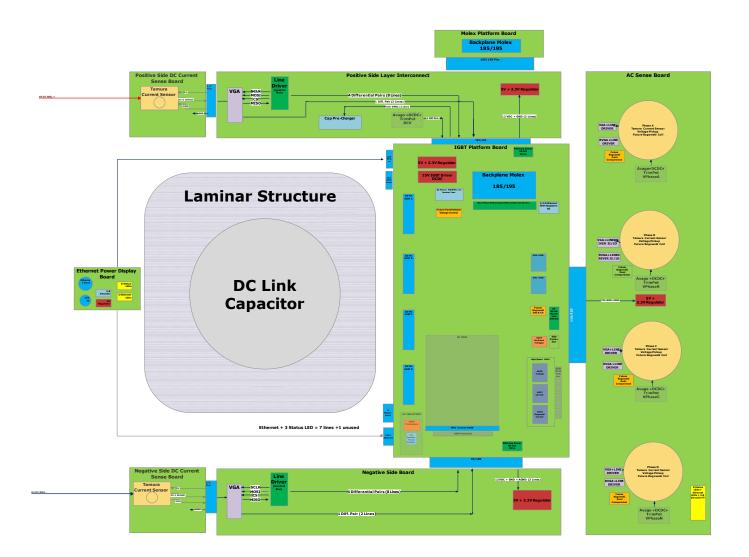

| 5.2  | Layout of Inverter                                                                             | 15 |

| 5.3  | Layout diagram of AC/DC sensing boards                                                         | 16 |

| 5.4  | Schematic of a single Voltage Sensing circuit                                                  | 17 |

| 5.5  | Voltage Divider Layout                                                                         | 17 |

| 5.6  | Potentiometer Layout                                                                           | 18 |

| 5.7  | Layout of AVAGO Opto-Isolator chip                                                             | 19 |

| 5.8  | Description of Pin Layout of AVAGO Opto-Isolator chip                                          | 19 |

| 5.9  | Voltage Regulator Connections                                                                  | 20 |

|      | Voltage Regulator Pin Layout                                                                   | 20 |

|      | DC/DC Converter Pin Layout                                                                     | 21 |

|      | DC/DC Converter Pin Descriptions                                                               | 21 |

|      | AVAGO Opto-Isolator Package details                                                            | 22 |

|      | Layout diagram of AC/DC Sense Boards                                                           | 24 |

|      | Schematic of Current Sensing Board                                                             | 25 |

| 5.16 | Diagram of Hall Effect Current Sensor source: http://archive.siliconchip.                      |    |

|      | <pre>com.au/static/images/articles/i305/30551_15lo.jpg</pre>                                   | 26 |

|      | Picture of TAMURA L31S***S05FS Current Sensor                                                  | 26 |

|      | Schematic of the TAMURA L31S***S05FS Current Sensor                                            | 27 |

|      | Saturation Curve of the TAMURA L31S***S05FS Current Sensor                                     | 28 |

|      | Frequency Curve of the TAMURA L31S***S05FS Current Sensor                                      | 29 |

|      | Picture of the TAMURA L06S***S05 Current Sensor                                                |    |

|      | Electrical Schematic of the TAMURA L06S***S05 Current Sensor                                   | 30 |

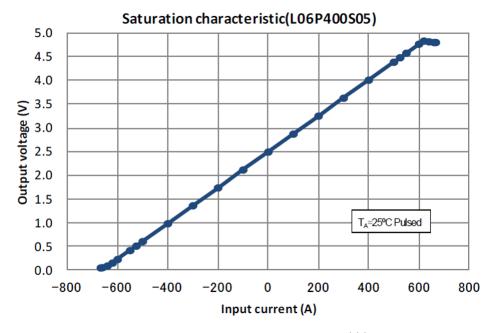

|      | Saturation Curve of the TAMURA L06S***S05 Current Sensor                                       | 31 |

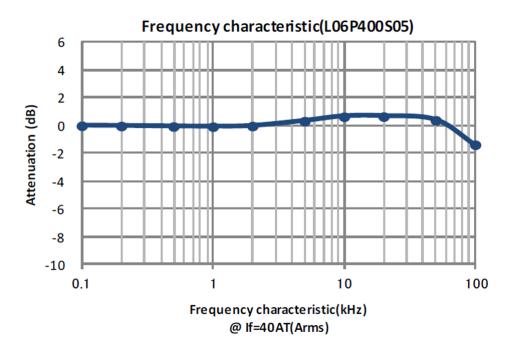

|      | Frequency Curve of the TAMURA L06S***S05 Current Sensor                                        | 32 |

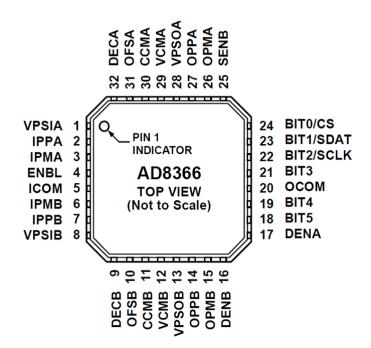

|      | Pin Layout of the Analog Devices AD8366 DVGA                                                   | 33 |

|      | Pin Descriptions of the Analog Devices AD8366 DVGA                                             | 33 |

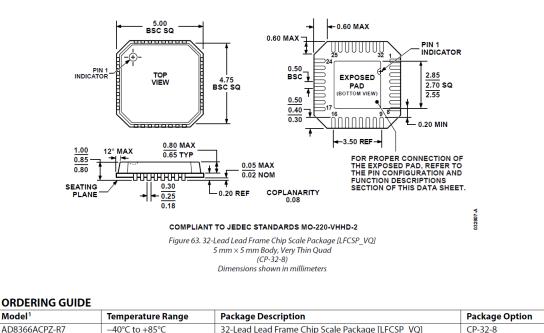

| 5.27 | Mechanical Specifications for the Analog Devices AD8366 DVGA                                   | 37 |

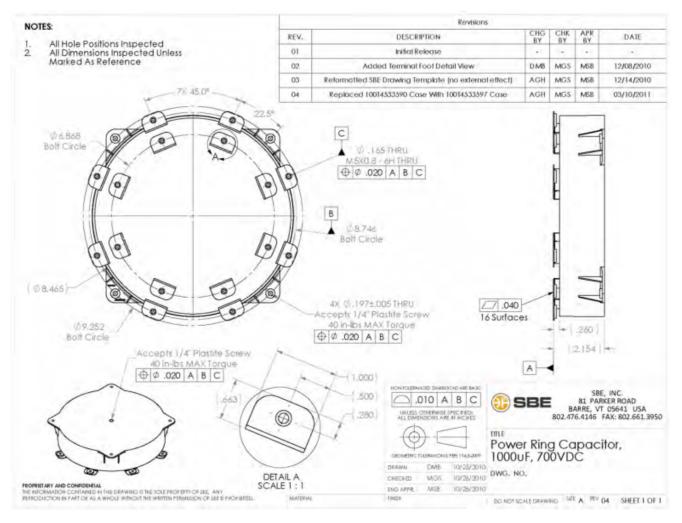

| 5.28 | DC Link Capacitor diagram                                                  | 40 |

|------|----------------------------------------------------------------------------|----|

| 5.29 | DC Link Capacitor Mechanical Layout                                        | 41 |

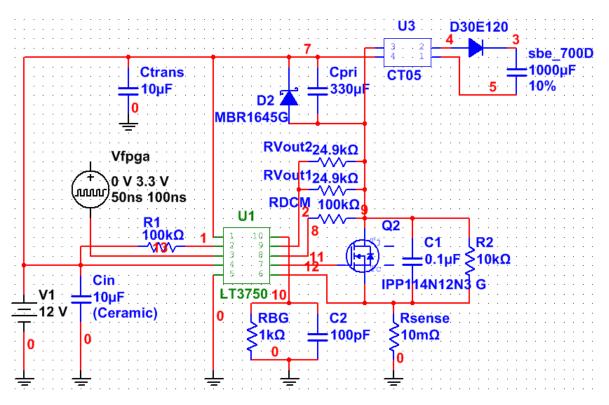

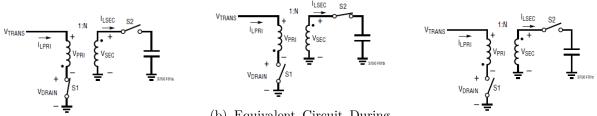

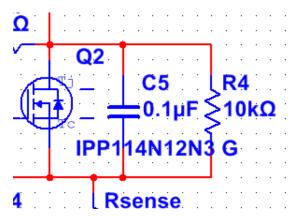

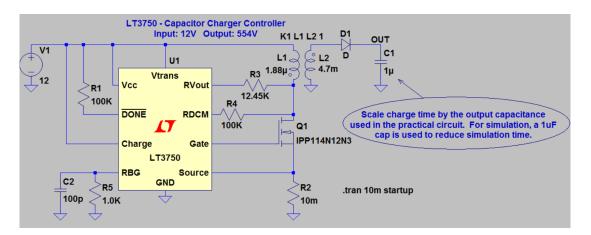

| 5.30 | Capacitor Pre-Charge Circuit                                               | 42 |

| 5.31 | States of Flyback Converter                                                | 43 |

| 5.32 | RC Snubber Circuit protecting MOSFET                                       | 47 |

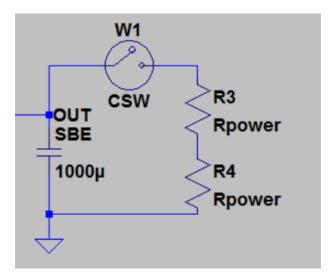

| 5.33 | Potential circuit for power 'bleeding' voltage divider                     | 47 |

| 5.34 | Example of differential pair signaling                                     | 48 |

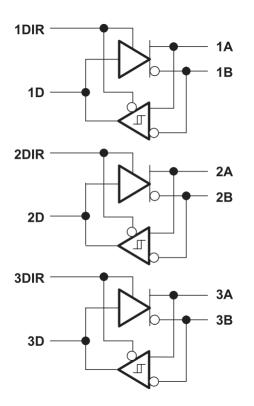

| 5.35 | Logic Diagram of the SN75LBC170                                            | 49 |

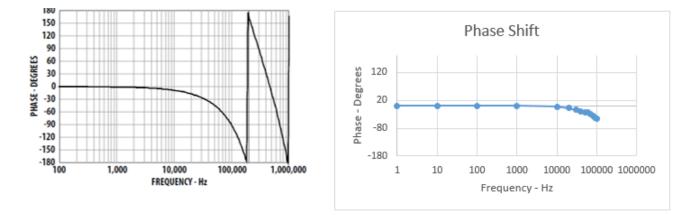

| 6.1  | Gain Response for the AVAGO Opto-Isolator compared to Experiment Results . | 52 |

| 6.2  | Phase Shift Response for the AVAGO Opto-Isolator compared to Experiment    |    |

|      | Results                                                                    | 53 |

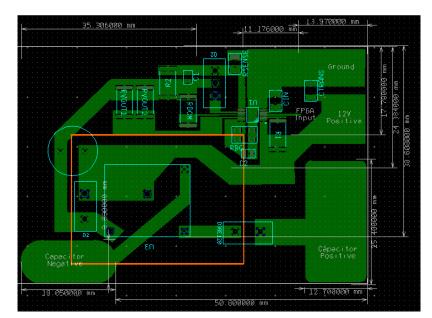

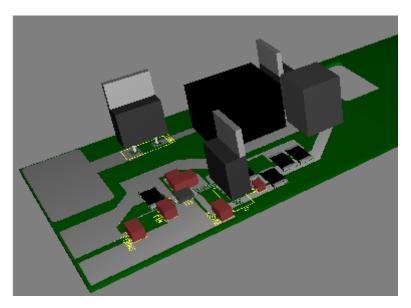

| 6.3  | PCB Layout for Pre-Charge Circuit                                          | 58 |

| 6.4  | 3D rendering of Pre-Charge Circuit                                         | 58 |

| 6.5  | Circuit used for Simulation with LTSPICEIV                                 | 59 |

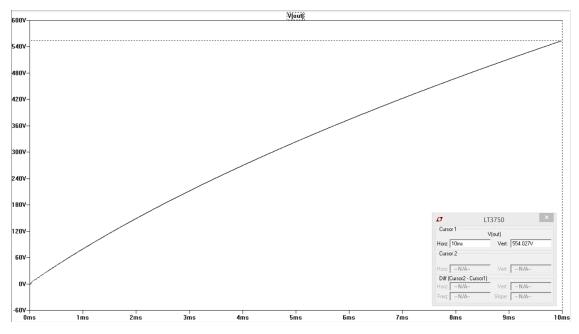

| 6.6  | Charging characteristic curve                                              | 60 |

| 6.7  | PCB as it arrived from Osh Park                                            | 60 |

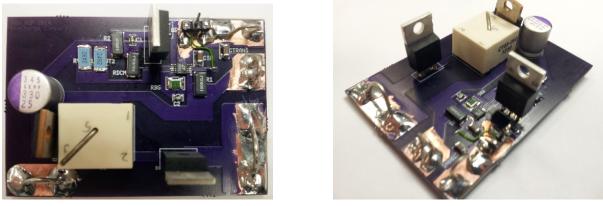

| 6.8  | 0                                                                          | 60 |

| 6.9  |                                                                            | 61 |

# List of Tables

| 5.1 | Resistance Values for Potentiometer                                              | 18 |

|-----|----------------------------------------------------------------------------------|----|

| 5.2 | Connections for TAMURA L31S***05FS Current Sensor                                | 27 |

| 5.3 | Connections for TAMURA L06P***S05 Current Sensor                                 | 30 |

| 5.4 | Detailed Pin Descriptions for AD8366 DVGA                                        | 36 |

| 5.5 | Amplifier values based on Parallel Programming                                   | 39 |

| 5.6 | Relationship between duty cycle, voltage gain and turns ratio to reach 700V with |    |

|     | 12V source                                                                       | 46 |

| 6.1 | Lab Results for Basic DC Functionality Testing                                   | 50 |

| 6.2 | Lab Results for Basic DC Functionality Testing                                   | 52 |

| 6.3 | Lab Results for Basic Single-Ended Functionality Testing                         | 55 |

| 6.4 | Lab Results for Basic Single-Ended Functionality Testing                         | 57 |

### Abstract

This project involved the collaboration and improvement of a novel inverter design with the primary aim of use in Alaskan fishing boats. A programmable power converter was designed such that diesel engines in generators could vary their rotational speed based on electrical load. This improves on the widely-adopted generator design, which requires that the engine spin at 1,800 RPM constantly in order to generate 60Hz power. The design that this project elaborates on has been tested and proven to work. The result of this project is a 30%-50% more efficient and expandable model for the inverter.

### Acknowledgments

We would like to thank Professor Bitar, our advisor, for his help and guidance with this project. We would also like to thank Father Joshua Resnick and Seraphim McGann, our sponsors, for their help and for allowing us to work on this project.

### Abbreviations

| <b>BJT</b> Bipolar Junction Transistor                              | <b>PCB</b> Printed Circuit Board                       |  |  |

|---------------------------------------------------------------------|--------------------------------------------------------|--|--|

| <b>CAD</b> Computer-Aided Design                                    | sbRIO Single-Board Reconfigurable In<br>ray put/Output |  |  |

| <b>FPGA</b> Field Programmable Gate Array                           |                                                        |  |  |

| <b>GPIC</b> General Purpose Inverter Controller                     | <b>TI</b> Texas Instruments                            |  |  |

| <b>IGBT</b> Insulated Gate Bipolar Transistor                       | <b>UMIC</b> Universal Modular Inverter Controller      |  |  |

| <b>KEV</b> Kodiak Electric Vessel                                   | <b>UPS</b> Uninterruptible Power supply                |  |  |

| <b>MOSFET</b> Metal Oxide Semiconductor Field-<br>Effect Transistor | VSI Voltage-Source Inverter                            |  |  |

| <b>NI</b> National Instruments                                      | <b>WPI</b> Worcester Polytechnic Institute             |  |  |

# Chapter 1

# Introduction

The state of Alaska relies heavily on the fishing industry as a source of income. It is estimated that the Alaskan economy generates \$5.8 billion annually from its fishing industries [3]. Alaska also supplies over half of the fish that the US consumes [2]. As such, any changes to the costs of catching fish in Alaska greatly affects the price of fish in the rest of the US.

All fisheries rely on special fishing and/or diving boats to catch fish. These boats use large diesel generators to power spot lights, bilge bumps, and other electrical systems on board. Diesel engines should be run at 60-75% of their maximum rated load otherwise the engine can be damaged. Common problems that occur from running diesel engines under a light load are carbon build up, internal glazing, and poor piston ring-sealing [6]. This means that the fishing boats often run extra electrical equipment in order to load down the diesel generators even if they don't need to use all of the equipment. Another source of wasted fuel is that in order to generate 60Hz AC, the motors are commonly fixed at 1800 or 3600 RPM. Depending on the current load of the system, the optimal speed of the diesel engine varies greatly.

Unfortunately, Alaska consistently has the highest diesel prices than any other west coast state [3]. The high fuel prices coupled with heavily loaded diesel generators means that extra money is spent on fuel. By using an inverter in line with the diesel generators, upwards of 30% could be saved on fuel costs. The generators produce 3-phase power which varies in frequency depending on the RPM the engine is set to. An inverter could convert this 3-phase power, regardless of frequency, into 60Hz AC power for the boats electrical systems.

The Kodiak Electric Vessel company (KeV LLC) is a small startup company in Kodiak, Alaska. The Universal Modular Inverter Controller (UMIC) is an inverter they started designing to increase the efficiency of diesel electric generator systems. A unique capability of the UMIC is that it is scalable. Multiple UMICs can be stacked to handle more power if necessary. This project focuses on improving the design of the controller by creating schematics, PCB layouts, and testing certain key components of the design. Where this project leaves off is where KeV plans to pick up and make it marketable to the fishing industry.

## Chapter 2

# Background

### 2.1 Kodiak Island and Alaska

### 2.1.1 Alaska

The Kodiak Electric Vessel (KEV) project is a unique project taking place in a unique location. The KEV project is being primarily researched and funded through our project sponsors, Joshua Resnick and Seraphim McGann, on Kodiak Island in Alaska. The project location greatly defines the specifications that must be met and adds great meaning to the inverter project. Due to the remoteness and weather in Alaska, technologies must be created and designed to be long lasting and efficient because of the lack of freely available resources, such as diesel fuel. The more efficient a technology, the more useful and reliable it can be for the user in Alaska. In this section, the unique location and characteristics of Alaska and Kodiak Island will be discussed.

The state of Alaska officially became part of the United States in January 1959, as the 49th state. The territory was purchased from the Russians in the 19th century, and has been a hub for Russian, American, and Native American cultures ever since [5]. The Alaskan economy is dominated by oil, natural gas and fishing. The state is the largest state in the United States by area, but the 4th least populous (ranking at 47th) and also the least densely populated in the United States. On average, there are about 1.26 people per square mile [9]. Below in Figure 2.1, Alaska is shown, note its remote location and size.

Because of its location, land area and population density, resources and costs of living are higher priced. In the more remote areas of Alaska, outside of main cities, residents must conserve what they have and be efficient in their daily lives. The purpose of the KEV inverter project is to enable more efficient usage of electric vehicle on-board generators for electricity as well as propulsion, in order to save money and resources. The primary application of this project will be used to complement on-board generators on commercial fishing vessels.

### 2.1.2 History of Alaska

Alaska has been part of the United States since 1959 but has been home to indigenous tribes for thousands of years before the arrival of Europeans [5]. The natural resources of Alaska have always been used as means for survival, and Alaska supplies many resources, such as oil, natural gas and seafood, to the rest of the United States. The first permanent European settlements were founded in the late 1700s, and Alaska has been a source of natural resources since [5].

Figure 2.1: Map of North America

#### 2.1.3 Alaskan Climate

The climate of Alaska differs greatly depending on the location of the state. Because it is such a large state, there are several different climate zones which effect lifestyles accordingly. This project is based on Kodiak Island, shown in Figure 2.2 below. This puts Kodiak Island in the "maritime" climate region, although commercial fishermen would be prone to the climate in nearly all of these regions.

In northern Alaska, the winters are very long and cold, with very short, cool summers. In July, the average low temperature is only 34 degrees Fahrenheit. In western Alaska, the "Transitional" region, there are extreme varieties in precipitation, ranging anywhere from 10 to 100 inches of precipitation each year. Finally, the interior of Alaska is subarctic. Both the highest and lowest recorded temperatures in Alaska have been recorded in the interior of the state. The summers sometimes reach as high as 90 degrees Fahrenheit, while the winters can fall below -60 degrees Fahrenheit [1].

The capital city, Anchorage, as well as Kodiak Island, are located in southern Alaska. The weather is very dependent on the coast in that region. It is a subarctic climate, with little rain, but large amounts of snow accumulation each year [1]. Projects in this environment, including the KEV project, will have to be able to adapt and incorporate these drastic climate ranges.

### 2.1.4 Kodiak Island

The Kodiak Electric Vessel project is based in Kodiak Island, Alaska (highlighted in Figure 2.3). Kodiak Island is an island off the south coast of the state. It is the second largest island

Figure 2.2: Climate Regions of Alaska

in the United States and is heavily forested and mountainous [8]. There are seven different communities that make up the Island, with the main city being Kodiak. To gain access to the island, one must take a boat or fly in to Kodiak's airport.

Since being purchased by the United States in 1867, Kodiak Island has become a center for commercial fishing. Kodiak Island is a boating community and many things revolve around this industry. Fishermen, boat mechanics, and many other fishing related professionals live on the island. The largest U.S. Coast Guard base in the United States also resides on Kodiak Island, further proving the need for such a KEV inverter project. The base is known as "Coast Guard Base Kodiak" and holds many other defense units, such as the "Integrated Support Command Kodiak", "Air Station Kodiak", "Communications Station Kodiak", and "Aids to Navigation Station Kodiak". There are about 400 combined officers and enlisted personnel who help operate the base. Their primary role is aerial search and rescue missions throughout Alaska [4].

Kodiak Island has long and cold winters and mild summers with heavy precipitation throughout the year. Throughout this report, we will see how all of the aspects and characteristics of Alaska and Kodiak Island go into the engineering decisions of the KEV inverter project.

Figure 2.3: Map of Alaska, with Kodiak Island

### 2.2 Power Devices

### 2.2.1 Inverters

An inverter is an electronic device or circuitry that changes direct current (DC) to alternating current (AC) [10]. The opposite of inverters are rectifiers which convert AC power to DC. Inverters are used in a wide variety of applications such as power generation (solar panel arrays), frequency control (induction heating), power grid applications (high voltage DC transmission and grid-tied inverters), uninterruptible power supply (UPS) systems, and electric motor speed control for any application with electric motors.

This project uses inverters for electric motor speed control. A standard generator must operate at a fixed RPM in order to output 60Hz power. However, the most efficient operating RPM varies according to the load on the generator. This load/RPM mismatch causes standard diesel generators to waste between 30% - 50% of their fuel due to operational inefficiency [12].

This problem is circumvented with the use of power inverters. A UMIC Controller (Universal Modular Inverter Controller) is placed between the generator and the load. Load matching and efficient operation can now occur as the inverter can output consistent 60Hz power while the generator runs in the most efficient region on its fuel consumption map for any given load. Decoupling the load from the generator means additional energy conversions via the UMIC and a slight loss of power in each conversion. However, these losses are completely offset the by

Figure 2.4: Diesel Efficiency Map

fuel savings associated with the motor operating at the most efficient speed and led to a total efficiency improvement by as much as 30% according to KeV, from the preliminary results of TRL-6.

#### 2.2.2 Genset

A genset is a diesel engine and an electric generator otherwise known as a diesel-electric generator. Gensets are used to provide power to marine vessels and other independent electrical networks. Drawbacks of typical gensets are that they are large, requiring lots of boat real estate, exposed to corrosion, prone to multiple types of failure, difficult to service/replace, and expensive. This project replaces the typical genset with a Power Dense Motor (PDM). Advantages of PDMs over typical diesel-electric generators are: there is no exciter stage and thus they are much smaller; it is a protected, sealed, and oil cooled unit; and they have no rotating winding or diodes and are less prone to these types of failures. Figure 2.5 shows the location of the PDM within the system.

#### 2.2.3 Storage Devices

Batteries have become an everyday part of life. We rely on them to power the numerous electrical devices we use every day. For this reason, when someone says the term 'energy storage', batteries are what most often comes to mind, but there are a variety of energy storage devices available each with their own advantages, applications and limitations, shown in Figures 2.6 and 2.7.

Figure 2.5: Control Flow Diagram

Figure 2.6: Tree Diagram of Energy Storage options

In many electronic applications, capacitors are becoming the energy storage avenue of choice. Particularly, capacitors outperform other storage methods in applications that require high power density without necessarily needing high energy density.

### 2.2.4 Insulated Gate Bipolar Transistor

An Insulated Gate Bipolar Transistor (IGBT) is a three terminal semiconductor power device. Introduced in the 1980s, it is mostly used in switching applications due to its high efficiency and fast switching speeds. An IGBT is a four layer device that combines the input characteristics typical of MOSFETs with the output characteristics of BJTs. This gives the IGBT a very high voltage rating with a low voltage drop per unit area. The circuit symbol and its equivalent are show in Figure 2.8 [11]. IGBTs have an I-V characteristic quite similar to those of the BJT. They differ in that the controlling parameter is the gate-source voltage for the IGBT while the BJT is controlled via the input current. These characteristics have made IGBTs the device of choice for most modern high-power switching applications.

Figure 2.7: Ragone Chart comparing storage devices

Figure 2.8: IGBT circuit symbol

Figure 2.9: IGBT I-V characteristic

## Chapter 3

# **Problem Statement**

As shown in the Background section of the paper, a large number of Alaskans depend on the fishing industry for their income and way of life. In addition, the largest United States Coast Guard bases are located in Alaska. Many Alaskans depend on boats and industrial fishing vessels which have been shown to be quite inefficient. With more efficient vessels, Alaskans will be able to save money on fuel, lower their operational costs, and decrease harmful fossil fuel emissions. This would allow for Alaskans to take home more income while reducing the chance of breakdown in generators.

The goal of this project is to create a scalable modular power inverter that is able to control any existing diesel generator system to supply any type of electrical load. This power inverter must maintain 60Hz power while varying the rotations per minute (RPM) of the generator to match the power load. Generators normally operate at a set RPM which may or may not be their most efficient operational point. The usage of this power inverter will allow the generator to operate at variable RPM while continuously storing/discharging energy to supply the load. The inverter cost must be low so the typical Alaskan would be able to afford it and be able to make their money back in a reasonable amount of time. Lastly, this inverter must be able to convert any combination of DC and AC.

This inverter uses multiple printed circuit boards within a sealed enclosure. In addition, the inverter will be expandable through multiple layers in order to handle larger amounts of power and larger, more complex electrical systems. This MQP project focuses on the design, development, and testing of several of the boards needed for the larger inverter project. These boards are as follows:

- IGBT Platform Board

- Voltage Sensing Board

- Current Sensing Board

- Pre-charge Circuit

These boards are discussed in the following sections of the paper. Through the time of our project, several new boards were created in order to fit new constraints. The following boards need to be developed further:

- Status Board

- IGBT Driver Board

In order to complete this inverter project, more design, development, and testing must be done. The remaining objectives for this project include developing the Status and IGBT Driver boards. After these boards are completed, the entire inverter must be tested as a single unit. Testing has been done for several of the boards individually, but all of the boards must operate together.

## Chapter 4

# Methodology

Since a part of this project was pre-existing, the report will detail the current implementation in Section 4.1 and the project's changes in Section 4.2.

### 4.1 Original Implementation

At the beginning of the project, the KeV inverter topology looked very different than it currently does. The original design used only one National Instruments Single-Board Reconfigurable Input/Output (sbRIO) 9606 board, which was meant to control all layers of the inverter. It also used NI's General Purpose Inverter Controller (GPIC), which was a large riser board for the sbRIO 9606 that provided a limited amount of I/O and other functionality that was unneeded by our inverter design.

### 4.2 **Proposed Implementation**

Over the course of the project, the group has made many changes to the proposed implementation of the new design. We recommend the replacement of the GPIC with a custom Printed Circuit Board (PCB) that would be more tailored to suit the needs of the design. We worked with the KEV team to design such a board. The design evolved into a system using several linked PCBs that are custom-fit to a sealed enclosure that will house the inverter. Due to the movement towards a sealed black-box system for each inverter layer, the design was changed so that each layer would have its own sbRIO. This introduced the complexity of allowing each layer to communicate and share high-speed data between the FPGAs on the sbRIO devices. To mitigate this need, we developed an isolated parallel data bus that could link the different layers together.

### 4.2.1 Sealed Enclosure

This system is designed to be operated in harsh marine environments. Since it contains many sensitive electronic components, there is a need for a dust- and water-proof enclosure to house the inverter. KeV has designed such an enclosure, to be milled out of steel. A CAD model of the enclosure is shown in Figure 4.1.

This enclosure represents one "layer" of the inverter. Layers can be stacked using the connectors shown on the top and bottom of each one. As mentioned in the next section, each layer is independently operable due to a distributed control topology.

Figure 4.1: CAD Model of Sealed Enclosure

### 4.2.2 Distributed Layout

Initially, the system was formed around a single FPGA. This required routing high-speed buses along PCB traces and placed a high computational load on the FPGA. The load has therefore been distributed across the layers. In addition to allowing more powerful computation on the FPGA, it allows for a much larger number of layers than were previously possible. This allows KeV to build more powerful and larger inverters. We put an sbRIO 9606 on each layer instead of one centralized unit. This also reduces the number of high-speed pins that must be run between the layers. It does, however, introduce additional complexity as a result of keeping many sbRIO devices in sync and allowing them to share data quickly and efficiently.

### 4.2.3 Direct-to-Digital Conversion

In the initial design, analog signal lines from the sensors were run back to the GPIC before they were converted into digital signals. In addition, not all of the sensors had a differential output so the signals would be subject to large amounts of interference without additional hardware. We suggested converting the signal to a digital one as physically close to the sensor as possible. This conversion, coupled with differential digital signaling, means we are able to run the signal lines near power without worrying about interference or signal degradation due on the trace path (to a certain extent).

For these conversions we chose the ADS85364 converter from Texas Instruments. The datasheet for this component can be found in Appendix B. This ADC features 6 differential inputs, and has a throughput of 4µs per channel. This allows it to sample at 250kSPS at 16-bit resolution. A high sampling rate is necessary to make precise adjustments to the regulation of the system to ensure peak efficiency.

### 4.2.4 AD/DC Sensor Boards

Since the start of the project, the AC/DC Sensor boards have remained largely the same. One of the only changes was with the "sensor mezzanine" boards The originally designed inverter included a separate location for "sensor mezzanines". These mezzanines were separate boards that were able to attach and detach from the board, allowing the customer to measure and keep track of several currents in the system, according to the needs of the customer. This board was to consist of a TAMURA current sensor, the necessary resistors for this current sensor (see data sheet in Appendix B), and connections to the Current Sensing Board. These current sensors were going to be directly attached to the mezzanine boards, which would then plug into the inverter.

## Chapter 5

# **Design Description**

The full scope of the Universal Modular Inverter Controller (UMIC) design is broken out into a block diagram in Appendix C. No block has been fully designed yet, but a lot of progress was made designing sub-components of all of the blocks. The DC current sensor, AC voltage sensor, capacitor pre-charger, backplane and general differential signal routing have all been completed. More work needs to be done designing the Ethernet power display board, Rogowski coil circuit, and IGBT driver link board.

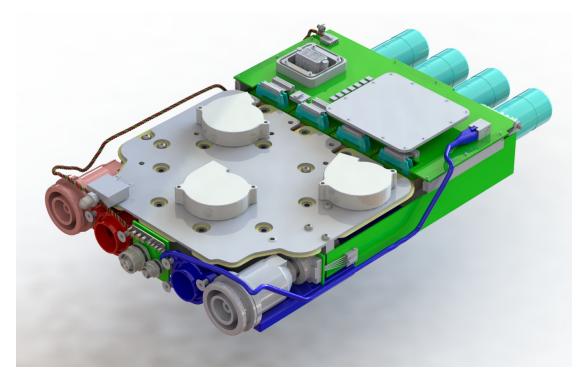

Figure 5.1: 3D rendering of the inverter without the enclosure

### 5.1 Voltage Sensing Board

As part of the inverter functionality, it is necessary to constantly monitor and adjust settings in order to continue the most efficient operation. In order to control a generator load and be a diverse, flexible inverter controller, the device must monitor several key characteristics of the system. According to the specifications of the project, the UMIC, will be placed between the generators (on a commercial fishing vessel) and the load. The UMIC will allow the generator to supply 60Hz of power, while varying the engine RPM in order to become more fuel efficient.

Figure 5.2: Layout of Inverter

In order to properly control the generators, the UMIC must know what is happening in the entire system. The two more important values that must be monitored in the system are voltage and current, thus the total power can also be calculated and measured. Each UMIC will be able to handle and constantly monitor up to 600kW of continuous three-phase power. With such high power levels, monitoring the system is of the utmost of importance. This section will describe the circuit board that will measure the voltage levels and pass that signal on to the rest of the board so it can be properly interpreted.

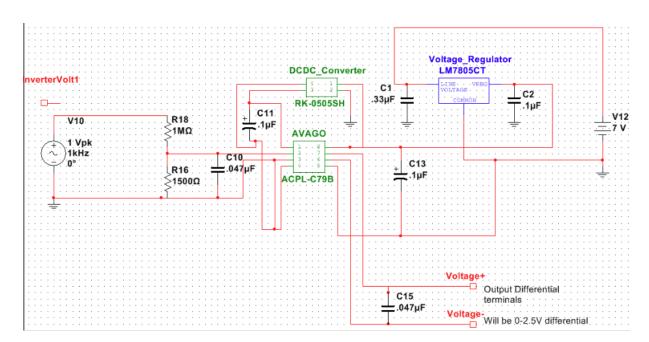

#### 5.1.1 Schematic of Voltage Sensing Board

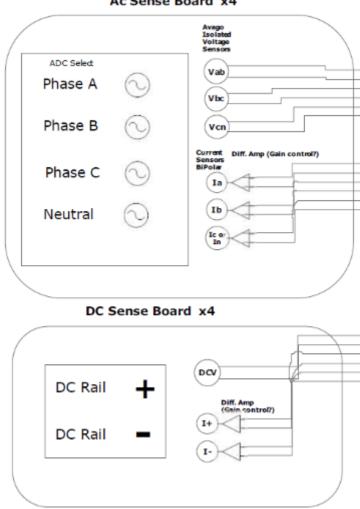

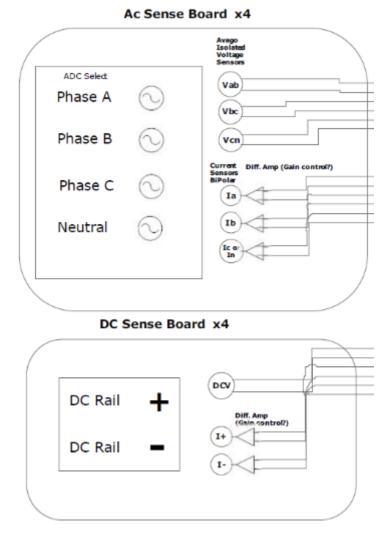

As previously discussed, this circuit board will be responsible for monitoring the voltage levels of the system. This board will be identically replicated four times. The same board will be used in order to monitor the voltage between phase A and B,  $V_{AB}$ , the voltage between phase B and C,  $V_{BC}$ , the voltage between phase C and neutral (N),  $V_{CN}$ , and the DC voltage. The layout of the sensing boards are shown below in Figure 5.3.

These sensing boards (the voltage sensing board and current sensing board) are responsible for isolating the appropriate signals, translating that signal into a scaled output, and passing that output to the interpreting board (FPGA). In the figure above, you can see the high speed differential Analog to Digital converters which will convert the analog signal provided by the sensor boards to a digital signal which the interpreting boards can then analyze. These sensing boards are labeled as "Powerstage" boards and at the lowest level of the inverter. The schematic of the circuit is shown below.

#### Input Voltages

The input voltages to the voltage sensing board will be taken directly from the generator and its conductors. Each phase of the AC components will have a sensing board associated with it so that each of the three phase-to-phase voltages can be measured and accounted for. These sensing boards will be responsible for measuring the voltage between phase A and B,  $V_{AB}$ , the voltage between phase B and C,  $V_{BC}$ , the voltage between phase C and neutral (N),  $V_{CN}$ , and the DC voltage. The AC voltages should be around 385  $V_{PP}$  while the DC voltages may occasionally reach up to 900V on the DC link capacitor. The voltage sensing boards must be able to deal with this range because the UMIC needs to be flexible and able to be used on many different systems with different electrical needs. One important aspect of this board is that the input voltage and the secondary voltages must remain isolated at all times for safety and reliability, which will be accomplished using the AVAGO Opto-Isolator. However, before

Ac Sense Board x4

Figure 5.3: Layout diagram of AC/DC sensing boards

this high voltages can be analyzed and electrically isolated, they must be scaled down using a voltage divider.

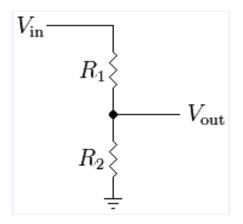

The voltage divider used in the circuit is a simple device which consists of two resistors. Because the voltage levels are rather high and based on the needs of the AVAGO Opto-Isolator, the voltages must be scaled down. The amount that the voltage is scaled down depends on the ratio of the resistors in series in the voltage divider. The schematic shows a 1M $\Omega$  resistor and a 1500 $\Omega$  resistor in series. In the designed circuit, these resistor values will certainly change. For example, in the prototype circuit, a resistor value of 51k $\Omega$  with the potentiometer was used. With this ratio, the voltage input to the AVAGO chip is roughly 10% of the input voltage. The resulting output voltage of a voltage divider can be mathematically expressed using the following Equation 5.1.

$$V_{out} = \frac{R_2}{R_1 + R_2} * V_{in} \tag{5.1}$$

Each of the above variables is explained in Figure 5.5

Based on the needs of the customer and their electrical system, these resistor value can be changed. The customer will need to know what voltage levels their system is operating at and use resistor values that can convert to the  $\pm 200$ mV recommended input for the AVAGO Opto-

Figure 5.4: Schematic of a single Voltage Sensing circuit

Figure 5.5: Voltage Divider Layout

Isolator chip. An important thing to note with the usage of the AVAGO Opto-Isolator chip is its input resistance between the input (pin 2) and grounds (pins 3 and 4). This resistance is shown in the data sheet (see below) and is typically 20 k $\Omega$ . This is important because it adds another resistance that is equivalent to a resistance in parallel with R2 (which will lower the actual resistance value). In the designed prototype, using the 5 k $\Omega$  potentiometer, it is the same as having an R2 value of 4 k $\Omega$ .

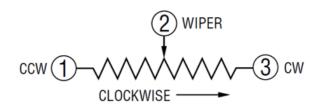

In order for the customer to easily change the resistor values on the device, based on their needs, the design has been created with R2 (in Figure 5.5) as a potentiometer. A potentiometer is a variable resistor. The resistor value can be altered (in this case) by using a small screw driver and turning an adjustable knob on the potentiometer. For our design, the Bourns 3214J – 5-Turn Trimpot Trimming Potentiometer will be used. This design is a surface mount device. The part number for this potentiometer is 3214J-1-502E. The initial value of the potentiometer is  $5,000\Omega$ . The device can be turned to change the resistance value from anywhere from  $5,000\Omega$  to  $0\Omega$ . Some arbitrary values are shown below.

The table shows the various turns of the potentiometer. By turning the knob on the po-

| Resistance      | Input resistance    | Proportion of   | Percentage of |

|-----------------|---------------------|-----------------|---------------|

| $Value(\Omega)$ | of AVAGO $(\Omega)$ | Voltage Divider | voltage into  |

|                 |                     |                 | AVAGO         |

| 5000            | 4000                | 4000/51000      | 7.8%          |

| 4000            | 3333.33             | 3333.33/51000   | 6.5%          |

| 3000            | 2608.70             | 2608.70/51000   | 5.1%          |

| 2000            | 1818.18             | 1818.18/51000   | 3.6%          |

| 1000            | 952.38              | 952.38/51000    | 1.9%          |

| 0               | Undefined           | 0/51000         | 0%            |

Table 5.1: Resistance Values for Potentiometer

tentiometer, the resistance value will therefore change. The values of the resistances based on the number of turns on the knob are shown below. Based on these values, and the fixed resistor (R1), the output voltage of the divider (which will become the input to the AVAGO Opto-Isolator chip) changes as a proportion based on the description of the voltage divider. These values are also shown in Table 5.1. Depending on the voltage levels of the customer, the potentiometer will have to be adjusted accordingly. The potentiometer limits the amount of voltage into the AVAGO chip, so that it can function correctly.

In order to correctly use the potentiometer, the leads must be attached correctly. There are three pins on the potentiometer, and are shown below in Figure 5.6.

Figure 5.6: Potentiometer Layout

In order to use the full 5,000  $\Omega$ , the leads must be connected across pins 1 and 3. In order to use a resistance value less than or equal to 5,000  $\Omega$ , the leads must be attached pins 1 and 2 and the screw must be turned to adjust to the necessary resistance value.

As for every component, the product dimensions are important to consider to ensure every part will fit on the board designed for the inverter. The Bourns Potentiometer layout and mechanical specifications can be found in the datasheet location in Appendix ??.

The usage of a potentiometer rather than a regular resistor allows for the inverter to be more flexible, and deal with a larger range of voltages, based on the customer needs.

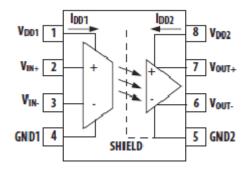

#### AVAGO Opto-Isolator

The AVAGO Opto-Isolator chip is what the entire voltage sensing board revolves around. In this design, we are going to be using the AVAGO Opto-Isolator chip (ACPL-C79B-000E). This isolation amplifier is designed for both current and voltage sensing needs. This chip is able to be used for current and voltage sensing circuits along with many other applications. The primary reason for choosing this chip rather than another is because the AVAGO chip is especially useful for isolating precision analog signals in a noisy environment. The voltage measurements need to be precise and accurate and cannot be improperly measured due to noise of the surrounding

circuit and electrical system. In addition, this chip is able to scale the voltage signal back up to a level that the FPGA can use and understand. The output voltage is approximately 8.2 times higher than the input voltage, which would give us an output voltage range of -1.6V to 1.6V.

As mentioned earlier, for safety and reliability reasons, the input voltage from the generator must be electrically isolated from the output voltage, which will be passed on to the upstream boards. Improper isolation could lead to damaged parts, inaccurate readings, and safety hazards. One feature of the AVAGO Opto-Isolator board is electrical isolation between pins 1-4 (input side) and pins 5-8 (output side). The usage of this electrical isolation is incredibly important for the function of this inverter, which is one of the reasons it was chosen.

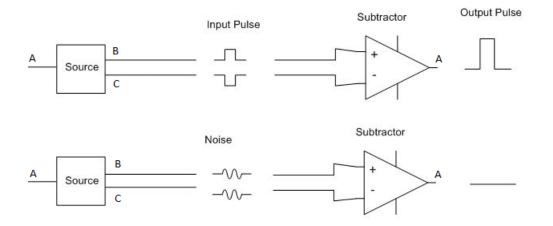

The last main feature that led to the usage of the AVAGO Opto-Isolator chip in this design was the fact that it provides differential outputs. This chip has the ability to take either single-ended or differential inputs and automatically provides a differential output. Referring back to the initial requirements and features of the chip, the differential output is useful for distinguishing the noise in the circuit and eliminating it. The positive and negative output voltages allow for two voltage signals which can eventually be subtracted from one another in order to remove the noise from the original signal. Based on the combination of these features with the AVAGO Opto-Isolator chip, it will be used in the design of the inverter.

Now that this chip has been selected, more information will be discussed on its operation and layout. There are eight pins on the AVAGO Opto-Isolator. The functional diagram of the chip is shown below followed by the description of each pin.

Figure 5.7: Layout of AVAGO Opto-Isolator chip

| Pin No. | Symbol            | Description                                                      |

|---------|-------------------|------------------------------------------------------------------|

| 1       | V <sub>DD1</sub>  | Supply voltage for input side (4.5 V to 5.5 V), relative to GND1 |

| 2       | V <sub>IN+</sub>  | Positive input (± 200 mV recommended)                            |

| 3       | V <sub>IN-</sub>  | Negative input (normally connected to GND1)                      |

| 4       | GND1              | Input side ground                                                |

| 5       | GND2              | Output side ground                                               |

| 6       | V <sub>OUT-</sub> | Negative output                                                  |

| 7       | V <sub>OUT+</sub> | Positive output                                                  |

| 8       | V <sub>DD2</sub>  | Supply voltage for output side (3 V to 5.5 V), relative to GND2  |

Figure 5.8: Description of Pin Layout of AVAGO Opto-Isolator chip

The eight pins of the AVAGO chip each has a unique purpose in the greater voltage sensing circuit. In order to power the chip, a supply voltage must be provided. Pin 1 is the supply voltage for the input side, and must remain relatively steady, at 4.5 to 5.5V, which is relative

to GND1 (pin 4). Because the chip is isolated between the input and output sides, an output supply voltage must also be provided. This supply voltage must be between 3 to 5.5V, which is relative to GND2 (pin 8). In order to provide these steady voltages, a DC-DC converter, voltage regulator, and voltage supply must also be included in the design.

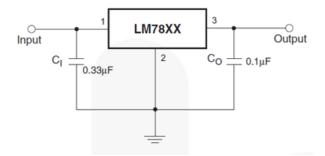

A voltage regulator is an electronic device that is designed to maintain a constant voltage level. This device in the circuit is used in conjunction with the DC/DC Converter in order to provide a constant 5V voltage supply to both the input and output voltage supply pins. In this design, the Fairchild Semiconductor 3-Terminal Positive Voltage Regulator (LM7805CT) has been chosen. Supplied by a customer provided 7V (or higher) source, the voltage regulator is placed to remove fluctuation and noise from the voltage supply. In order for the AVAGO Opto-Isolator chip to function correctly and consistently, it must receive a constant, steady voltage supply. Because of the voltage regulators drop-out voltage; the supply voltage must be higher than the output voltage. According to the data sheet, the input supply voltage must be 7V or higher, due to the 2V drop-out voltage (loss from input to output). In addition, in common practice, two capacitors must be added to the input and output sides of the regulator to ground similar to the Figure 5.9.

Figure 5.9: Voltage Regulator Connections

This voltage regulator will provide an output voltage anywhere from 4.75V to 5.25V, both of which are within the specifications of the AVAGO chip, and directly correlates to the voltage regulator's 4% output voltage tolerance.

In addition, the voltage regulator provides thermal overload and short-circuit protection in order to protect the circuit from the malfunctions of the voltage source. This further isolates the system and will protect it if something malfunctions. The pin layout and descriptions are shown in the Figure 5.10 below.

Figure 5.10: Voltage Regulator Pin Layout

According to these pin layouts and pin descriptions, the circuit schematic and design has been connected accordingly. The data sheet for this device can be found in the Appendix B. This device works in conjunction with the DC/DC Converter which will be described next.

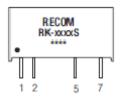

A DC-DC converter is an electronic device that converts a DC voltage from one voltage level to another. In this circuit, it is important to provide the AVAGO chip with the proper voltage so it can continue to function properly. The chosen DC-DC Converter for this project was the RECOM Econoline DC/DC Converter (Rk-0505S/H). The primary function of this device is to receive the regulated voltage (from the voltage regulator), provide further electrical isolation, and provide a steady 5V output.

This device has up to 4,000 VDC of isolation and can receive a wide range of input voltages. No matter the received voltage, it will provide a steady 5V source for the input voltage supply (pin 1) and continue to isolate it from the output side. The main purpose of this device is to ensure that both the input and output voltage supply pins receive the proper voltage source while keeping the circuit electrically isolated.

The layout of the RECOM 5V DC/DC Converter is shown below which is followed by the pin descriptions.

Figure 5.11: DC/DC Converter Pin Layout

| Pin Connections<br>RK-xxxxS |        |  |

|-----------------------------|--------|--|

| Pin #                       | Single |  |

| 1                           | +Vin   |  |

| 2                           | -Vin   |  |

| 5                           | -Vout  |  |

| 7                           | +Vout  |  |

Figure 5.12: DC/DC Converter Pin Descriptions

The circuit diagram discussed at the beginning of the voltage sensing circuit section shows the proper connections for this device to the rest of circuit. The data sheet for this device can be found in Appendix B.

In order for the AVAGO Opto-Isolator chip to work correctly, it also needs bypass capacitors connected between some of its pins. According to the data sheet, it is recommended that bypass capacitors are connected pins 1 and 4 and pins 5 and 8. These capacitors are 0.1µF and must not be electrolytic capacitors due to their nature of being polarized. This could lead to malfunctions and destruction of capacitors. These capacitors are required because of the high-speed digital nature of the signals inside the isolation amplifier. These capacitors should be placed as close to the AVAGO Opto-Isolator pins as possible. It is important to note that for testing purposes, across a large frequency range (BODE plots, etc.) it is necessary to remove these bypass capacitors, because they will block higher frequency AC signals (as a lowpass filter).

Bypass capacitors that are 47nF are also needed between pins 2 and 3 and pins 6 and 7. These capacitors are placed in between the positive and negative input voltage signals as well as the positive and negative output voltage signals. These capacitors are recommended due to the switched-capacitor nature of the input circuit. These capacitors are also used to prevent high-frequency noise from interfering with the input signal.

These capacitors are critical in ensuring that the AVAGO chip can function properly as well as translate an input voltage signal into an amplified output differential signal with as little noise and distortion as possible. With less noise and distortion, the readings will be much more accurate, and lead to greater efficiencies for the entire system.

The last component required by the AVAGO Opto-Isolating chip is a voltage supply. This voltage supply will be supplied by the customer, and the customer would have a range of choices. With the selected DC/DC Converter and Voltage Regulator, it is recommended that a 5V source is used. This voltage source is required in order to power the AVAGO chip. Using the voltage straight from this voltage source is risky, and could potentially be noisy or unreliable. Because of this possibility, the DC/DC Converter and Voltage Regulator is placed in between the voltage source and AVAGO chip.

Returning to the overall discussion of the AVAGO Opto-Isolator chip, the remaining pins must be explained. In order to analyze and isolate the voltage signal, the voltage signal must first be passed into the device. There are two inputs on the chip, the positive and negative inputs (pins 2 and 3 respectively). Typically, a single ended input would be used, so in this case, the output from the voltage divider would become the input to the AVAGO chip. Because a single-ended input is being used, the negative input (pin 3) is typically connected to GND1 (pin 4), and grounded (different ground than GND2 on output side).

The output of AVAGO chip is a differential output. The negative output voltage signal is pin 6, while the positive output voltage signal is pin 7. By using both of these pins as the output signal, the two signals are able to be compared, and the FPGA will be able to remove any noise before it analyzes the signal waveform. Lastly, because this chip is electrically isolated, there are two grounds, one for the input and one for the output side, so pin 5 is used as the GND2 for the output side.

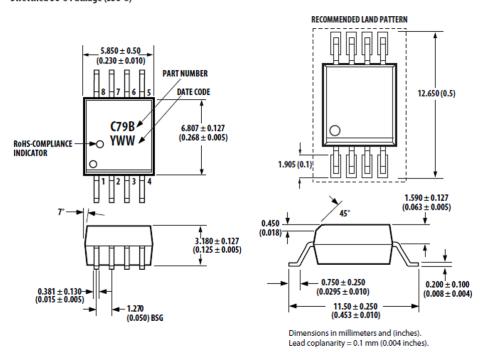

It is important to also consider the physical layout of the device. On the UMIC, there is limited space to work with, so all larger chips and components must be carefully considered. The typical package type for the AVAGO chip is a stretched SO-8 Package (SSO-8). The measurements of this package are shown in Figure 5.13.

Stretched SO-8 Package (SSO-8)

Figure 5.13: AVAGO Opto-Isolator Package details

As mentioned previously, the entire voltage sensing circuit board revolves around the usage of the AVAGO Opto-Isolator chip. All of these components must come together to support the correct functionality of the AVAGO chip and the entire voltage sensing circuit. If done correctly, two output voltage signals should be produced that will be an amplified version of the input voltage signals.

#### **Output Voltages**

The final outcome of the voltage sensing circuit is the output voltage signals. Coming directly from the AVAGO Opto-Isolator chip, a differential output will be seen. Pin 6 is the negative output voltage signal and Pin 7 is the positive output voltage signal. When these two signals are compared, another circuit is able to determine what noise there is in the system. Therefore, the noise can be eliminated, and a much cleaner signal can be used. The gain of the AVAGO chip is typically 8.2, which means the output voltage range will be anywhere from -1.6V to 1.6V. These two output voltage signals will then be passed to the high speed, differential analog-digital converters (on an adjacent board) for further signal processing. After the signal is passed on to the ADC, this marks the end of the requirements and design of the voltage sensing board.

### 5.2 Current Sensing Board

#### 5.2.1 Description of circuit

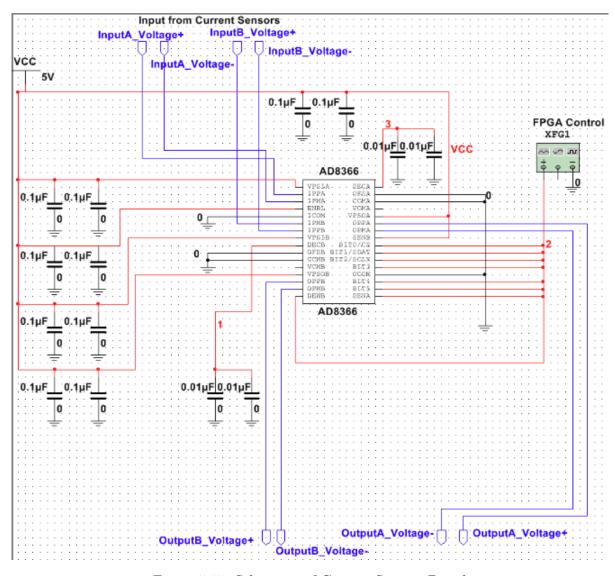

As described in the previous section about the voltage sensing circuit, it is necessary for the UMIC to constantly monitor and process voltage and current information, in order to create a constantly self-adjusting, negative feedback loop. The purpose of this circuit is to constantly monitor the AC and DC current in the system, rather than the voltage as previously discussed. For this design, it is necessary to have four identical current sensing boards in order to measure the three different phase inputs (A, B, C) and the DC currents. This section will describe how the current levels are captured using sensors, translated to a differential signal, and then output to an ADC to eventually be interpreted by the FPGA.

#### 5.2.2 Schematic of Circuit

The first portion of the board is the sensing portion, which extracts a proportional (based on the current flow) voltage that will be the inputs for the current sensing chip. The second portion of this board is the actual current sensing chip, which will take these proportional voltages and translate them into differential outputs, which will then be passed further down the chain to be interpreted. The layout of the current sensing boards are shown below (alongside the voltage sensing boards) in Figure 5.14.

These sensing boards (the voltage sensing board and current sensing board) are responsible for isolating the appropriate signals, translating that signal into a scaled output, and passing that output to the interpreting boards (FGPA). In the figure above, you can see the high speed differential Analog to Digital converters which will convert the analog signal provided by the sensor boards to a digital signal which the interpreting boards can then analyze. These sensing boards are labeled as "Powerstage" boards and at the lowest level of the inverter. The schematic of the actual Current Sensing circuit is shown in Figure 5.15.

Figure 5.14: Layout diagram of AC/DC Sense Boards

### **Input Currents**

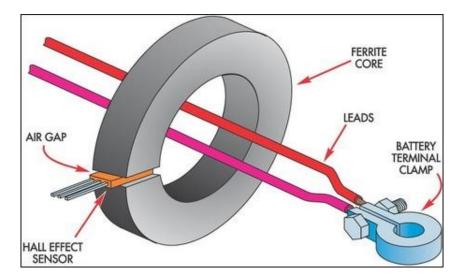

The input currents to the current sensing boards will be taken directly from the customer's electrical system. Each phase of the AC components, as well as the DC component will have cables between the generator and the load in order to deliver the necessary power. These cables will run directly through the current sensor (which is the shape of an O-ring). Because of the "Hall Effect", a voltage will then be induced based on current flowing and strength of the magnetic field. The current levels vary based on the user. The current sensing boards must be able to deal with this range in order to provide accurate readings at all times. These characteristics allow the designer several options in choosing the necessary parts. In order for the current to be accurately detected and measured, a proper current sensor must first be chosen. In Figure 5.16, the power cables (between the generator and load) running through the current sensor is shown. In the next section, the current sensors will be described in detail.

#### **TAMURA Hall Effect Current Sensors**

The current sensors just described above are used in a similar fashion as current transformers. Based on the "Hall Effect", the current of the device travels through the core of the current

Figure 5.15: Schematic of Current Sensing Board

sensor and induces a voltage based on the characteristics and amplitude of the current source. Based on these characteristics, a unique (to the current sensor design) voltage will be created, which will directly correlate to the current level in the wires. This information will be added to the coding and configuration of the FPGA which will then be able to interpret the current levels in the system by receiving a scaled down voltage. For this design, two different TAMURA Hall Effect Current Sensors have been selected. Part of the design will be based on the customer's needs and current levels. The two TAMURA Current Sensors that have been chosen are based on the average current levels that the user expects to see in their system. For lower currents, the TAMURA L31S\*\*\*S05FS Series was chosen. It is anticipated that this current sensor will be used for anywhere from 50A to 300A. For higher currents, the TAMURA L06P\*\*\*S05 Series was chosen. It is anticipated that this current sensor will be used anywhere from 400A to 800A.

For lower power applications, the L31S\*\*\*S05FS Series Current Sensor might be chosen. This particular sensor would be used on applications that have nominal primary current values from 50A to 300A. Although this particular sensor has models up to 600A, the TAMURA L06P\*\*\*S05 is typically a better choice at higher current levels. The design of this sensor differs slightly from the original picture above, but the same "Hall Effect" concept applies.

Figure 5.16: Diagram of Hall Effect Current Sensor source: http://archive.siliconchip. com.au/static/images/articles/i305/30551\_1510.jpg

Figure 5.17, is the exact current sensor used for this design is shown.

Figure 5.17: Picture of TAMURA L31S\*\*\*S05FS Current Sensor

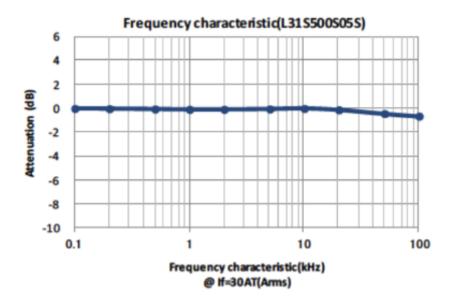

This specific current sensor was chosen based on its excellent accuracy and linear saturation characteristics. This allows for extremely accurate current readings to take place, and easier programming in regards to the FPGA. In addition, this design should be flexible and easy to adapt to the customer's needs. This current sensor is able to be used on a wide range of frequencies, with little adjustment from the user. Lastly, this current sensor has a high immunity to external interference, so for usage in a noisy, dirty, hot environment such as an engine room on a commercial shipping vessel, this current sensor will still be able to provide accurate readings and measurements.

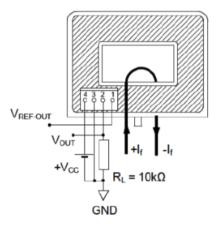

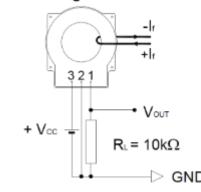

Similar to the overall schematic of the current sensing board previously described, the current sensor is one of the two main components on this board. The TAMURA Current Sensor has a rather simple electrical set up, and only has one main purpose. This simple device is shown below in Figure 5.18.

This current sensor accepts the primary conductor which carries a current,  $I_f$ , through normal usage. This current flows through the inverter as it is transferred from the generator to

Figure 5.18: Schematic of the TAMURA L31S\*\*\*S05FS Current Sensor

the load. The current sensor, how it is designed, extracts an induced voltage from the current running through it. There are four pins on the current sensor. According to the schematic of the circuit as well as the current sensing board, the circuit was set up according to the following Table 5.2.

| Pin | Description                              |

|-----|------------------------------------------|

| 1   | Voltage Reference                        |

| 2   | Output Voltage (connected with resistor) |

| 3   | Ground                                   |

| 4   | Supply Voltage (5V)                      |

Table 5.2: Connections for TAMURA L31S\*\*\*05FS Current Sensor

Like any electrical device, this connections must meet certain parameters in order to function correctly. Depending on the typical current levels of the customer, a current sensor can be chosen. As discussed earlier, this current sensor is best from 50A – 300A. This device also calls for a 5V supply among other things. The reference voltage can be set to whatever the user wants, and this value will be reflected in the rated output voltage as shown in the datasheet in the Appendix B. With the L31S\*\*\*05FS Current Sensors, it is possible to take advantage of the differential inputs of the AD8366. Because there is a Output Voltage (pin 2) and a Reference Voltage (pin 1), it is suggested that both pins connect to either of the differential inputs of the Analog Devices AD8366 for more effective noise cancellation. In the "Results" section, basic testing is done using the different inputs.

This TAMURA L31S<sup>\*\*\*</sup>05FS Current Sensor requires its own voltage supply in order to operate correctly. In this case, the current sensor requires a 5V supply,  $\pm 5\%$  ( $\pm 0.25$ V). In testing it is adequate to use a power supply, but in actual implementation it would connect to a common 5V rail, whose power source would be supplied by the customer.

Also shown in the schematic, the proper usage of this current sensor requires the use of a resistor (to limit current). This resistor is specified by the manufacturer to be 10,000  $\Omega$ . This resistor is placed between the output voltage and ground.

In order to meet the tight packaging requirements of the UMIC, each devices physical requirements must be considered, as well as the shape of the device. Although this is a relatively small device, it is perhaps the second largest electrical component in the entire inverter. The reason why these measurements are so important is that four of these current sensors must fit in the inverter. The exact dimensions can be found in the datasheet.

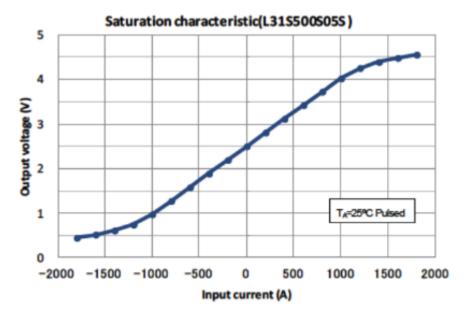

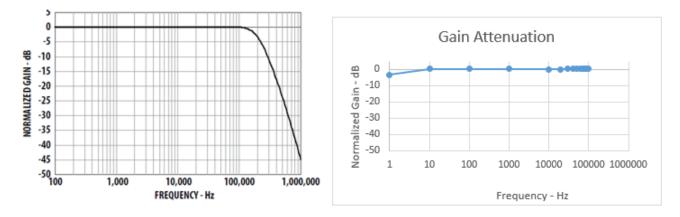

The last important characteristics to consider when using this current sensor is how the various primary nominal currents (at various current levels) proportionally affect the voltage levels, including at different frequencies. This first graph, Figure 5.19, shows the linear relationship between the input current (A) and output voltage (V).

Figure 5.19: Saturation Curve of the TAMURA L31S\*\*\*S05FS Current Sensor

This particular linear relationship makes it much easier to calculate the current flowing through the primary conductor when reading the output voltage. Although this graph is for the 500A version of the current sensor, all of the current sensors in this family have similar linear relationships between the input current and output voltage. For example, if the generator is providing power to the load, and there are 500A flowing through this particular conductor to the load to provide power, the output voltage would be roughly 0.6V (plus offset voltage), which would then be read by the FPGA, and interpreted as 500A. In this case, the offset voltage is 2.5V (shown at 0A input), which matches up with the rest of the graph. The output voltage (with no added offset voltage) Saturation Table will confirm these data in the datasheet.