# HIGH-PERFORMANCE DECODER ARCHITECTURES FOR LOW-DENSITY PARITY-CHECK CODES

by

Kai Zhang

A Dissertation Submitted to the faculty of the

#### WORCESTER POLYTECHNIC INSTITUTE

In partial fulfillment of the requirements for the Degree of Doctor of Philosophy

in

Electrical and Computer Engineering

by

August, 2011

APPROVED:

Prof. Xinming Huang Thesis Advisor Worcester Polytechnic Institute Prof. Berk Sunar Thesis Committee Worcester Polytechnic Institute

Prof. James Duckworth Thesis Committee Worcester Polytechnic Institute Dr. Zhongfeng Wang Thesis Committee Broadcom Corporation

#### Abstract

The Low-Density Parity-Check (LDPC) codes, which were invented by Gallager back in 1960s, have attracted considerable attentions recently. Compared with other error correction codes, LDPC codes are well suited for wireless, optical, and magnetic recording systems due to their near-Shannon-limit error-correcting capacity, high intrinsic parallelism and high-throughput potentials. With these remarkable characteristics, LDPC codes have been adopted in several recent communication standards such as 802.11n (Wi-Fi), 802.16e (WiMax), 802.15.3c (WPAN), DVB-S2 and CMMB.

This dissertation is devoted to exploring efficient VLSI architectures for high-performance LDPC decoders and LDPC-like detectors in sparse inter-symbol interference (ISI) channels. The performance of an LDPC decoder is mainly evaluated by area efficiency, error-correcting capability, throughput and rate flexibility. With this work we investigate tradeoffs between the four performance aspects and develop several decoder architectures to improve one or several performance aspects while maintaining acceptable values for other aspects.

Firstly, we present a high-throughput decoder design for the Quasi-Cyclic (QC) LDPC codes. Two new techniques are proposed for the first time, including parallel layered decoding architecture (PLDA) and critical path splitting. Parallel layered decoding architecture enables parallel processing for all layers by establishing dedicated message passing paths among them. The decoder avoids crossbar-based large interconnect network. Critical path splitting technique is based on articulate adjustment of the starting point of each layer to maximize the time intervals between adjacent layers, such that the critical path delay can be split into pipeline stages.

Furthermore, min-sum and loosely coupled algorithms are employed for area efficiency. As a case study, a rate-1/2 2304-bit irregular LDPC decoder is implemented using ASIC design in 90 nm CMOS process. The decoder can achieve an input throughput of 1.1 Gbps, that is, 3 or 4 times improvement over state-of-art LDPC decoders, while maintaining a comparable chip size of 2.9 mm<sup>2</sup>.

Secondly, we present a high-throughput decoder architecture for rate-compatible (RC) LDPC codes which supports arbitrary code rates between the rate of mother code and 1. While the original PLDA is lack of rate flexibility, the problem is solved gracefully by incorporating the puncturing scheme. Simulation results show that our selected puncturing scheme only introduces the BER performance degradation of less than 0.2dB, compared with the dedicated codes for different rates specified in the IEEE 802.16e (WiMax) standard. Subsequently, PLDA is employed for high throughput decoder design. As a case study, a RC-LDPC decoder based on the rate-1/2 WiMax LDPC code is implemented in CMOS 90 nm process. The decoder can achieve an input throughput of 975 Mbps and supports any rate between 1/2 and 1.

Thirdly, we develop a low-complexity VLSI architecture and implementation for LDPC decoder used in China Multimedia Mobile Broadcasting (CMMB) systems. An area-efficient layered decoding architecture based on min-sum algorithm is incorporated in the design. A novel split-memory architecture is developed to efficiently handle the weight-2 submatrices that are rarely seen in conventional LDPC decoders. In addition, the check-node processing unit is highly optimized to minimize complexity and computing latency while facilitating a reconfigurable decoding core.

Finally, we propose an LDPC-decoder-like channel detector for sparse ISI channels using belief propagation (BP). The BP-based detection computationally depends on the number of nonzero interferers only and are thus more suited for sparse

ISI channels which are characterized by long delay but a small fraction of nonzero interferers. Layered decoding algorithm, which is popular in LDPC decoding, is also adopted in this paper. Simulation results show that the layered decoding doubles the convergence speed of the iterative belief propagation process. Exploring the special structure of the connections between the check nodes and the variable nodes on the factor graph, we propose an effective detector architecture for generic sparse ISI channels to facilitate the practical application of the proposed detection algorithm. The proposed architecture is also reconfigurable in order to switch flexible connections on the factor graph in the time-varying ISI channels.

#### Acknowledgements

First of all, I wish to thank my advisor, Professor Xinming Huang, for his guidance and support through all stages of my studies and research at the Worcester Polytechnic Institute. I am very grateful for his recognition, his inspiration, and the exposure and opportunities that I have received during the course of my study.

I am also indebted to to Professor Berk Sunar, Professor James Duckworth, and Dr. Zhongfeng Wang for their valuable supports as members of my thesis committee.

I am grateful to my fellow graduate students in the Embedded Computing Lab, Cao Liang, Wenxuan Guo, Yanjie Peng, Chen Shen and Wei Wang for their friend-ship and support.

I would also like to thank all the staff in ECE department, including Robert Brown, Catherine Emmerton, Colleen Sweeney, Brenda McDonald and Stacie Murray for their kind assistance and coordinations.

This thesis is dedicated to my wonderful family. I am forever grateful to my parents Shanfeng Zhang and Qingfang Zhao, my wife Wanning Jiang, for their love, support, and encouragement. I shall not try to put my appreciation and love for them into words.

# Contents

| Intr | oducti                                                      | on                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | Backg                                                       | round                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2  | Relate                                                      | ed Works                                                                                                         | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.3  | Summ                                                        | ary of Motivations and Contributions                                                                             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 1.3.1                                                       | Ultra-High-Throughput LDPC Decoder Architecture Design .                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 1.3.2                                                       | Flexible-Rate High-Throughput LDPC Decoder Architecture                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |                                                             | Design                                                                                                           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 1.3.3                                                       | Efficient Decoder Architecture Design for LDPC Codes with                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |                                                             | Special Structure                                                                                                | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 1.3.4                                                       | Efficient Architecture Design in LDPC-Like BP-Based Cir-                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |                                                             | cumstances                                                                                                       | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.4  | Outlin                                                      | ne                                                                                                               | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LDI  | PC Co                                                       | des and Decoding Algorithms                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1  | Introd                                                      | uction of LDPC Codes                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2  | Quasi-                                                      | Cyclic LDPC Codes                                                                                                | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.3  | Belief                                                      | Propagation Algorithm                                                                                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.4  | Min-S                                                       | um Algorithm                                                                                                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.5  | Loosel                                                      | y Coupled Algorithm                                                                                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 1.1<br>1.2<br>1.3<br>1.4<br>LDI<br>2.1<br>2.2<br>2.3<br>2.4 | 1.1 Backg 1.2 Relate 1.3 Summ 1.3.1 1.3.2  1.3.3  1.4 Outlin  LDPC Co 2.1 Introd 2.2 Quasi- 2.3 Belief 2.4 Min-S | 1.2 Related Works  1.3 Summary of Motivations and Contributions  1.3.1 Ultra-High-Throughput LDPC Decoder Architecture Design  1.3.2 Flexible-Rate High-Throughput LDPC Decoder Architecture Design  1.3.3 Efficient Decoder Architecture Design for LDPC Codes with Special Structure  1.3.4 Efficient Architecture Design in LDPC-Like BP-Based Circumstances  1.4 Outline  LDPC Codes and Decoding Algorithms  2.1 Introduction of LDPC Codes  2.2 Quasi-Cyclic LDPC Codes  2.3 Belief Propagation Algorithm  2.4 Min-Sum Algorithm |

|   | 2.6  | Early Termination Strategy                                        | 16 |

|---|------|-------------------------------------------------------------------|----|

|   | 2.7  | Layered Decoding Algorithm                                        | 18 |

| 3 | Hig  | h-Throughput LDPC Decoder Architecture with Parallel Lay-         |    |

|   | erec | l Decoding                                                        | 22 |

|   | 3.1  | High Throughput Strategies                                        | 22 |

|   | 3.2  | Parallel Layered Decoding Architecture                            | 25 |

|   | 3.3  | Critical Path Splitting                                           | 29 |

|   | 3.4  | Proposed Decoder Architecture                                     | 30 |

|   |      | 3.4.1 Overall Decoder Architecture                                | 31 |

|   |      | 3.4.2 Pipelined Architecture for CNU                              | 33 |

|   |      | 3.4.3 Decision Units                                              | 35 |

|   | 3.5  | Implementation Results                                            | 36 |

|   | 3.6  | Summary                                                           | 39 |

| 4 | Hig  | h-Throughput Rate-Compatible LDPC Decoder Architecture            | 40 |

|   | 4.1  | Introduction                                                      | 40 |

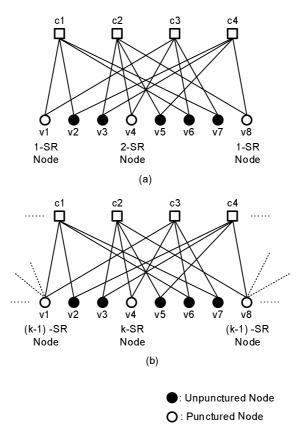

|   | 4.2  | Puncturing Schemes for Rate-Compatible LDPC Codes                 | 42 |

|   |      | 4.2.1 Quasi-Cyclic LDPC Codes with Dual-Diagonal Parity Structure | 42 |

|   |      | 4.2.2 Rate-Compatible LDPC Codes                                  | 43 |

|   |      | 4.2.3 Selected Puncturing Scheme                                  | 45 |

|   | 4.3  | High-Throughput Rate-Compatible LDPC Decoder Architecture         | 50 |

|   |      | 4.3.1 Summary of the Parallel Layered Decoding Architecture       | 50 |

|   |      | 4.3.2 RC LDPC Decoder Design                                      | 54 |

|   | 4.4  | Experimental Results                                              | 57 |

|   |      | 4.4.1 Simulation Results for Punctured WiMax Codes                | 57 |

|   |      | 4.4.2 Hardware Implementation Results                             | 58 |

|   | 4.5  | Summ   | ary                                                           | 61 |

|---|------|--------|---------------------------------------------------------------|----|

| 5 | Low  | -Comp  | plexity LDPC Decoder Architecture for CMMB Systems            | 62 |

|   | 5.1  | Introd | uction                                                        | 62 |

|   | 5.2  | QC-LI  | OPC Codes in CMMB Standard                                    | 64 |

|   | 5.3  | Dual-r | rate Decoder Design                                           | 65 |

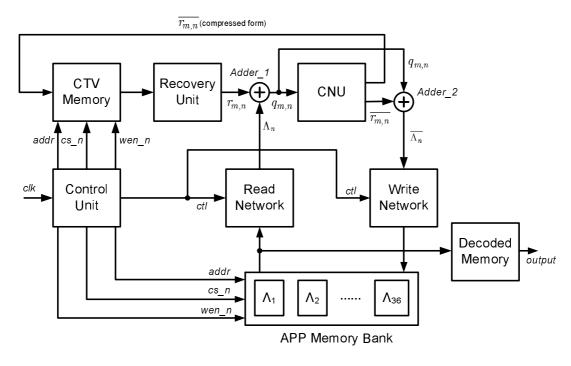

|   |      | 5.3.1  | Overall Architecture                                          | 66 |

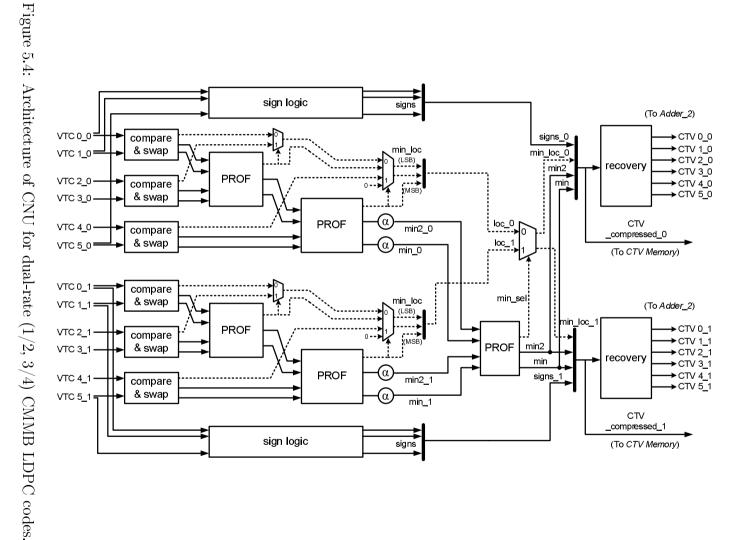

|   |      | 5.3.2  | Dual-Rate CNU Design                                          | 67 |

|   |      | 5.3.3  | Memory Access for Partially Parallel Layered Decoding         | 71 |

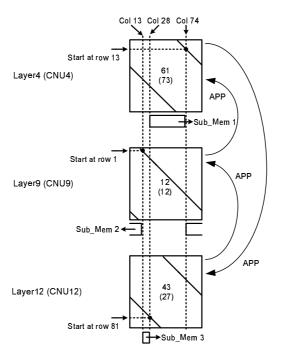

|   |      | 5.3.4  | Split-Memory Architecture for Weight-2 Sub-matrices           | 72 |

|   |      | 5.3.5  | Number of Pipeline Stages                                     | 74 |

|   | 5.4  | Area-I | Efficient Design Techniques                                   | 76 |

|   |      | 5.4.1  | Memory Reduction                                              | 76 |

|   |      | 5.4.2  | $Read/Write\ Networks  . \ . \ . \ . \ . \ . \ . \ . \ . \ .$ | 76 |

|   | 5.5  | Impler | mentation results                                             | 79 |

|   | 5.6  | Summ   | ary                                                           | 81 |

| 6 | Des  | ign of | Belief-Propagation Based Detectors for Sparse ISI Chan-       |    |

|   | nels | i      |                                                               | 82 |

|   | 6.1  | Introd | uction                                                        | 82 |

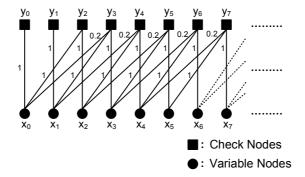

|   | 6.2  | Chann  | ael Model and Decoding Algorithms                             | 84 |

|   |      | 6.2.1  | Channel Model and Factor Graph Representation                 | 84 |

|   |      | 6.2.2  | Belief-Propagation Algorithm                                  | 85 |

|   |      | 6.2.3  | Layered Decoding Algorithm                                    | 87 |

|   | 6.3  | Simula | ation Results                                                 | 87 |

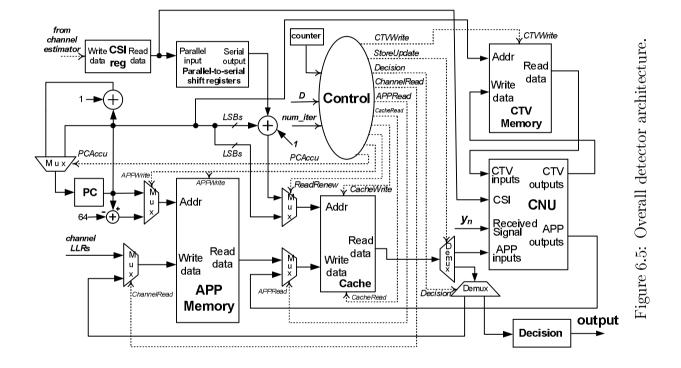

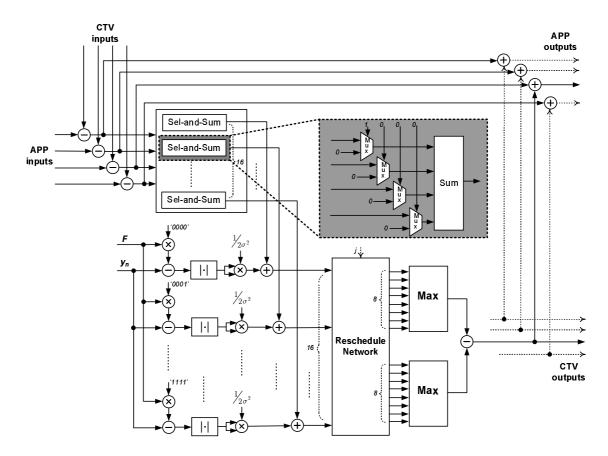

|   | 6.4  | Detect | for Architecture Design                                       | 90 |

|   |      | 6.4.1  | Overall Architecture                                          | 90 |

| 7 | Con | clusio | ıs                      | 97 |

|---|-----|--------|-------------------------|----|

|   | 6.6 | Summ   | ary                     | 96 |

|   | 6.5 | Impler | mentation Results       | 95 |

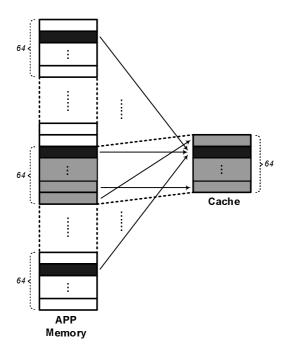

|   |     | 6.4.3  | Cache-Like Architecture | 94 |

|   |     | 6.4.2  | Architecture of CNU     | 93 |

|   |     |        |                         |    |

# List of Figures

| 2.1 | Regular (8,4) LDPC codes: (a) Parity-check matrix (b) Tanner graph           | 11 |

|-----|------------------------------------------------------------------------------|----|

| 2.2 | Implementation of early termination strategy                                 | 18 |

| 2.3 | Parity-check matrix for the selected rate- $1/2$ LDPC code in $802.16e$      |    |

|     | standard.                                                                    | 19 |

| 2.4 | Message passing flow in horizontal layered decoding                          | 19 |

| 2.5 | Architecture of horizontal layered decoding with loosely coupled al-         |    |

|     | gorithm                                                                      | 20 |

| 3.1 | Processing status at four different clock cycles                             | 26 |

| 3.2 | Variable summations passing directions of the ${\bf H}$ base matrix: (a) for |    |

|     | column 1 (b) for column 6                                                    | 28 |

| 3.3 | Offset-modified parity-check matrix for rate-1/2 LDPC code in 802.16e.       | 29 |

| 3.4 | Timing diagram for parallel layered decoding architecture                    | 29 |

| 3.5 | BER performance comparison of different decoding algorithms                  | 31 |

| 3.6 | Overall parallel layered decoding architecture for QC-LDPC codes             | 32 |

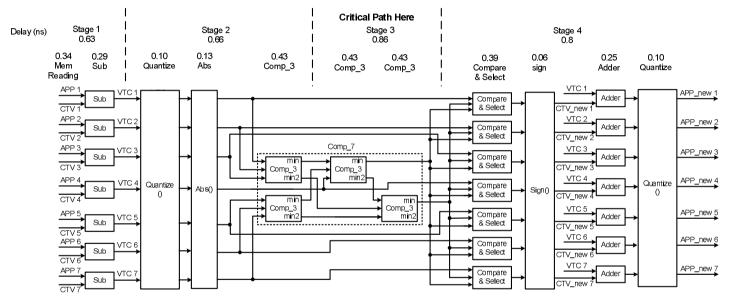

| 3.7 | CNU architecture with critical path splitting into 4 pipelined stages        | 34 |

| 3.8 | Register allocation in each section of the hard decisions                    | 35 |

| 3.9 | Layout of the decoder core area                                              | 37 |

| 4.1 | Description of 1-SR node and $k$ -SR node                                    | 44 |

| 4.2 | Parity-check matrix for the selected rate-1/2 LDPC code in WiMax                 | 46 |

|-----|----------------------------------------------------------------------------------|----|

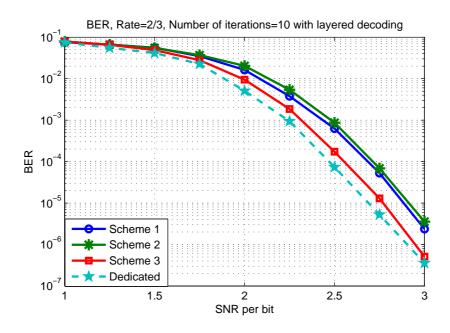

| 4.3 | BERs of the three punctured codes and the dedicated code at rate                 |    |

|     | 2/3 over AWGN channels                                                           | 47 |

| 4.4 | Overall architecture of a rate-compatible LDPC decoder                           | 53 |

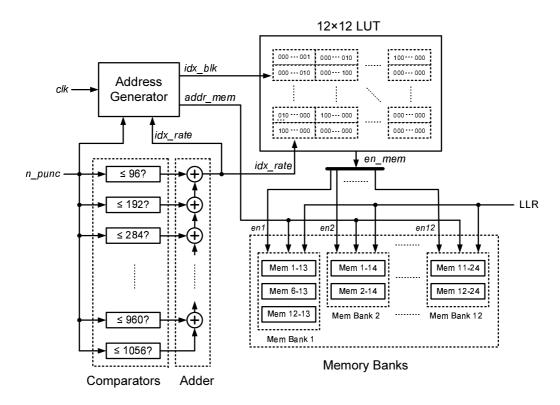

| 4.5 | Architecture of LLR Initialization Block                                         | 55 |

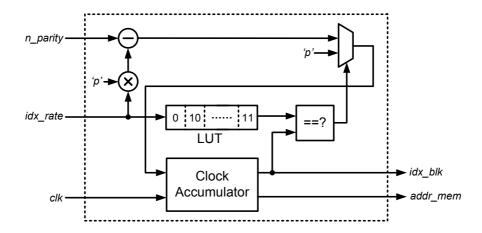

| 4.6 | Architecture of the Address Generator                                            | 56 |

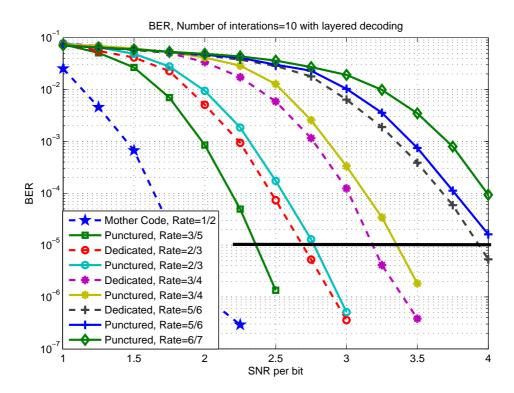

| 4.7 | BERs of the punctured LDPC codes over AWGN channels                              | 58 |

| 4.8 | Layout of the proposed decoder chip                                              | 59 |

| 5.1 | Structure of the parity check matrix for LDPC codes in CMMB stan-                |    |

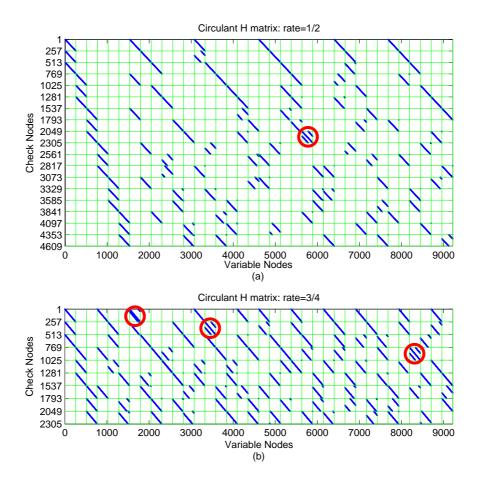

|     | dard: (a) rate-1/2; (b) rate-3/4                                                 | 64 |

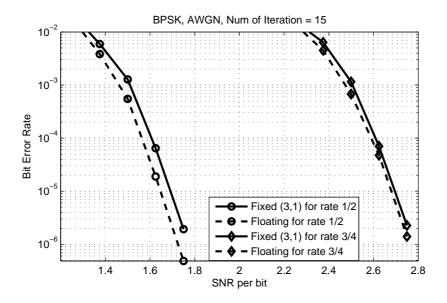

| 5.2 | BER performance for different rates and quantization schemes                     | 66 |

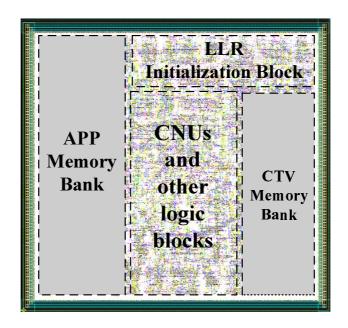

| 5.3 | Overall architecture of the CMMB LDPC decoder                                    | 67 |

| 5.4 | Architecture of CNU for dual-rate $(1/2,3/4)$ CMMB LDPC codes                    | 68 |

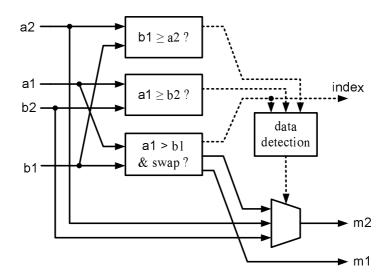

| 5.5 | The design of an PROF-based comparator                                           | 69 |

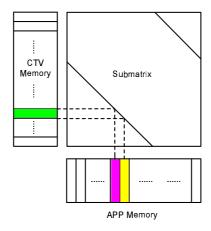

| 5.6 | Element correspondence relations between CTV memory and APP                      |    |

|     | memory                                                                           | 71 |

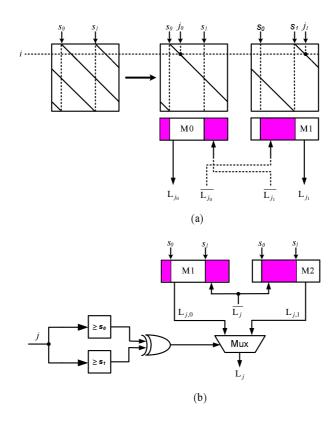

| 5.7 | Split-memory design for handling the weight-2 sub-matrices                       | 73 |

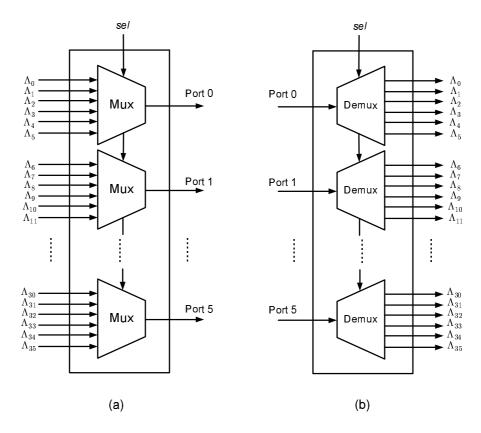

| 5.8 | For rate-1/2 codes (a) Architecture of read network; (b) Architecture            |    |

|     | of write network                                                                 | 77 |

| 6.1 | Factor graph of an ISI channel.                                                  | 85 |

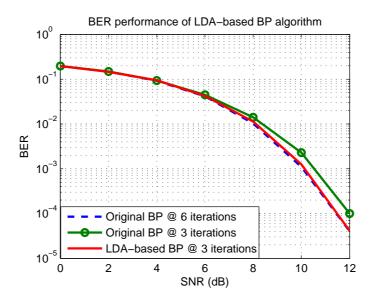

| 6.2 | BER comparison between original BP algorithm and LDA-based BP                    |    |

|     | algorithm.                                                                       | 87 |

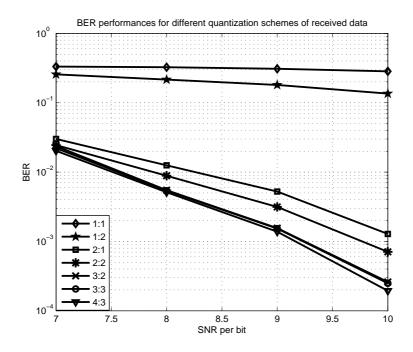

| 6.3 | $\ensuremath{BER}$ performance for various quantization schemes of received data | 88 |

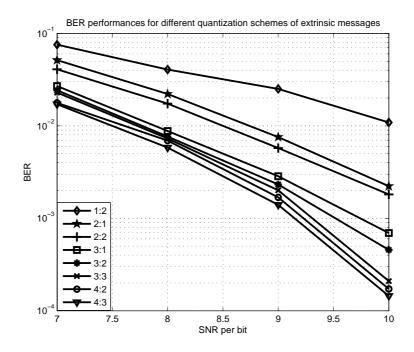

| 6.4 | BER performance for various quantization schemes of extrinsic mes-               |    |

|     | sages                                                                            | 89 |

| 6.5 | Overall detector architecture    | 91 |

|-----|----------------------------------|----|

| 6.6 | Architecture of the CNU          | 93 |

| 6.7 | Direct-mapped Cache Architecture | 94 |

# List of Tables

| 3.1 | Overall comparison between proposed decoder and other existing           |    |

|-----|--------------------------------------------------------------------------|----|

|     | LDPC decoders                                                            | 38 |

| 4.1 | Three puncturing schemes for achieving rate $2/3$ from rate $1/2$ mother |    |

|     | code                                                                     | 47 |

| 4.2 | Index of punctured blocks at different desired rates                     | 48 |

| 4.3 | Overall comparison between proposed decoder and other existing           |    |

|     | WiMax LDPC decoders                                                      | 60 |

| 5.1 | Connections of input and output ports in the read network for the        |    |

|     | rate-1/2 codes                                                           | 77 |

| 5.2 | Connections of input and output ports in the read network for the        |    |

|     | rate-3/4 codes                                                           | 78 |

| 5.3 | Overall comparison between proposed decoder and other existing ir-       |    |

|     | regular decoders                                                         | 80 |

# Chapter 1

# Introduction

This chapter first introduces the history of error correction codes and LDPC codes and then describes the motivation, related works, contributions and outline of this dissertation.

#### 1.1 Background

A major concern in designing reliable data transmission and storage systems is the control of data errors induced by a noisy channel or storage medium. In 1948, Shannon demonstrated that if the information rate is less than the channel capacity, introduced errors can be corrected by proper encoding and decoding of the information [63]. From then on, various types of error correction codes were designed by adding some redundancies to the original data (known as encoding), which the receiver can use to check consistency of the delivered message, and to recover data determined to be erroneous (known as decoding). Classical and widely used error correction codes include Hamming Code (1950), BCH Code (1959) [34, 8], Reed-Solomon Code (1960) [59], Convolutional Code (1955) [20, 74], Turbo Code (1993) [6] and LDPC Code (1962) [24].

Firstly discovered by Gallager in 1962 [24], LDPC codes were a class of Shannon-limit-approaching codes in which two innovative ideas were exploited: iterative decoding and constrained random code construction. However, LDPC codes were mostly neglected by code theorists for more than 30 years due to the tremendous computational efforts in implementing their encoder and decoder and the introduction of Reed-Solomon codes [59]. Shortly after the debut of another Shannon-limit-approaching code, Turbo code [6], in which both the above ideas are explored, LDPC codes were rediscovered by MacKay and Neal in 1996 [50]. LDPC codes have several advantages over Turbo codes: no error floors at high SNRs, more inherent decoding parallelism, higher throughput potentials, lower hardware complexity due to the elimination of long interleavers.

LDPC codes are specified by sparse parity check matrices **H** and can be fully represented by bipartite graphs (known as Tanner graph) with two sets of nodes, called the check nodes and the variable nodes. LDPC codes can be effectively decoded using the standard BP algorithm, also called sum-product algorithm (SPA). Two phases of messages, the check-to-variable (CTV) messages and the variable-to-check (VTC) messages, are transmitted along the edges of the Tanner graph [69] to update each other iteratively.

Good LDPC codes that have been found are largely long, random and computer generated codes with BP-based iterative decoding and can achieve an error performance as close as 0.0045 dB away from the theoretical Shannon limit [50, 49, 60, 61, 14]. In despite of excellent error performance, these codes are impractical for hardware implementation due to the following reasons: (1) they are very long (up to 100,000 bits) and thus a large memory is required to store the iterative messages, as well as the configuration of the **H** matrix; (2) their encoding circuitry would be very large in order to fulfill the complex matrix and vector

multiplications; (3) their large latency and lack of parallelism when decoding on a random Tanner graph; (4) randomly constructed LDPC codes also require a complex routing network, which not only consumes a large amount of chip area, but also significantly increases the computation delay.

In order to make LDPC codes hardware-friendly, structured LDPC codes that have elegant regularity in the structure of their **H** matrices and can provide comparable or even better error performance were introduced in by algebraic construction [40, 39, 75, 35, 73, 53, 19, 57]. It has been demonstrated in [48] that structured, algebraic-constructed codes can outperform random ones for medium length LDPC codes (up to a few thousand bits). Besides, their encoding can be simply implemented by linear shift registers. That is why LDPC codes are widely adopted by several recent communication standards such as 802.11n (Wi-Fi), 802.15.3c (WPAN) 802.16e (WiMax), DVB-S2, CMMB, 802.3an (10G-BaseT) and etc. Quasi-Cyclic (QC) LDPC codes, a special class of structured LDPC codes, decompose the large **H** matrix into small sub-matrices which are either identity matrix or its permutation [22, 43, 11]. Therefore, QC LDPC codes are best suited for hardware implementation since the regular structures of their **H** matrices make simple message switching and memory accessing possible.

#### 1.2 Related Works

This dissertation is devoted to high-performance VLSI architecture design and implementation for LDPC codes. Generally, state-of-art LDPC decoder architectures can be divided into three categories: fully parallel method, serial method and partly parallel method.

Blanksby et al. [7] directly mapped the BP algorithm into hardware and imple-

mented a fully parallel irregular LDPC decoder. This method, through with high throughput, requires huge amount of interconnections to complete the messages passing within a random Tanner graph, leading to the average net length of 3nm and the total chip area of 52.5 mm<sup>2</sup>. On the other side, Yeo et al. [80] designed a serial decoder by sharing the computation units and updating messages in sequential. Serial method results in very simple hardware architecture but low decoding throughput, which is usually unacceptable by real-world applications, due to the large latency of ten-thousand cycles needed for decoding a codeword.

Since structured LDPC codes are architecture-aware, their decoders can be implemented by partly parallel method to explore potential parallelism and improve the throughput [85, 12, 51, 86, 37, 87, 77, 36]. Compared with random LDPC codes, the **H** matrix of structured LDPC can be easily stored by storing only permutation values of each small sub-matrix instead of the entire **H** matrix. Also, regularity in the **H** matrix of structured LDPC codes enables easy control over the read/write operations of VTC and CTV messages when decoding by employing a simple bitwise counter, thus avoiding the huge interconnection network in [7]. QC LDPC decoders proposed in [77, 79, 78, 17, 66, 28, 45, 70, 9, 25, 27, 67] also belong to the partly parallel category.

# 1.3 Summary of Motivations and Contributions

This research is motivated by desires to explore high-performance LDPC decoder architectures in terms of area efficiency, error-correcting capability, throughput and rate flexibility. Although LDPC decoder has been an extensive research topic for almost a decade, there are still many unresolved problems. With this dissertation, we have considered existing VLSI design issues and developed various decoder ar-

chitectures to improve throughput, enhance flexibility and reduce complexity of an LDPC decoder.

The specific motivations for the work and the corresponding contributions will be summarized as follows.

# 1.3.1 Ultra-High-Throughput LDPC Decoder Architecture Design

Motivation: With the increasing demand for high-data-rate wireless applications, many recent communication systems employ ultra-high throughput channel codes to match the data-rate requirements. For example, 802.15.3c standard is targeted for the data rate of multi-giga bits per second (Gbps). However, conventional high-throughput LDPC decoders proposed in [7, 46, 54] were implemented by employing more hardware resources to operate at a higher parallelism, which consumed a large amount of chip area. For example, the decoder in [46] achieves an equivalent input throughput of 1 Gbps with a clock rate of only 200 MHz, an undoubtedly high parallelism of 512 and a large chip area of 14.5 mm<sup>2</sup> under 90 nm process. Thus it is desirable to investigate other methods to improve throughput.

Contribution: We proposed a parallel layered decoding architecture to achieve ultra high throughput. Parallel layered decoding architecture not only keeps the advantage of conventional layered decoding algorithm that can reduce the convergence required number of iterations by half and thus double the throughput, but also avoids the serial operations existing in conventional layered decoding algorithm which limits overall throughput. Two other techniques were also applied: critical path splitting and fixed message passing. The former optimizes the decoder's critical path and divides it into several pipelined stages. The latter avoids crossbar-based large interconnect network, which usually bottlenecks an LDPC decoder to achieve

high clock rate. Both techniques improve the clock rate and thus the throughput of an LDPC decoder without increasing parallelism and hardware resources. As a case study, a rate-1/2 2304-bit irregular LDPC decoder was implemented using ASIC design in 90 nm CMOS process. The decoder can achieve an input throughput of 1.1 Gbps, that is, 3 or 4 times improvement over state-of-art LDPC decoders, while maintaining a comparable chip size of 2.9 mm<sup>2</sup>.

# 1.3.2 Flexible-Rate High-Throughput LDPC Decoder Architecture Design

Motivation: In wireless communication systems, it is desirable to adjust ECC code rate according to the channel state information (CSI) to meet various service requirements and channel conditions. For example, WiMax standard provides 6 different LDPC code patterns in 4 different rates (1/2,2/3A,2/3B,3/4A,3/4B,5/6) [4]. Although there have been some research works on the design of flexible rate LDPC decoders [68, 84, 52, 46, 66], none of them can provide arbitrary code rate. Moreover, these decoders usually employ complicated interconnection network to switch between different code patterns [84, 46, 66], such as Benes networks used in [52], which leads to signal congestion problem, large delay and low throughput. How to design a flexible rate LDPC decoder with high throughput remains challenging. Contribution: With the dissertation we proposed a rate-compatible (RC) LDPC decoder architecture that can provide arbitrary code rate between the rate of the mother code and 1. Codes with flexible rates were generated by puncturing the parity bits of the mother code with negligible error performance degradation. Parallel layered decoding architecture was also adopted to achieve high throughput where complicated interconnect network was replaced by fixed wires. The proposed RC LDPC decoder also helps solve the rate inflexibility problem existing in previous parallel layered decoding architecture. As a case study, a RC-LDPC decoder based on the rate-1/2 WiMax LDPC code is implemented in CMOS 90 nm process. The decoder can achieve an input throughput of 975 Mbps and supports any rate between 1/2 and 1.

# 1.3.3 Efficient Decoder Architecture Design for LDPC Codes with Special Structure

Motivation: Although current LDPC decoders can handle QC LPDC codes effectively and efficiently, it is still a problem when dealing with some specially constructed codes, such as the LDPC codes in CMMB standard whose sub-matrices are weigh-2 superimposed matrices instead of identity matrices. The design of an area-efficient LDPC decoder that supports multiple code patterns is essential for wireless applications such as CMMB.

Contribution: We proposed a low-complexity LDPC decoder for CMMB systems. An area-efficient layered decoding architecture based on min-sum algorithm is incorporated in the design. A reconfigurable architecture, which can support dual rate LDPC codes specified in the CMMB standard, is constructed with minimal overhead. A novel split-memory architecture is developed to efficiently handle the weight-2 submatrices that are rarely seen in conventional LDPC decoders. In addition, the check-node processing unit is highly optimized to minimize complexity and computing latency while facilitating a reconfigurable decoding core.

# 1.3.4 Efficient Architecture Design in LDPC-Like BP-Based Circumstances

Motivation: Besides LDPC decoding, a large variety of algorithms in communication and signal processing can be viewed as instances of BP algorithm, which operates by iterative message passing on a bipartite graph [47]. For example, recent research has focused on the application of the BP algorithm to detecting over a known ISI channel [15, 62, 5]. The computational complexity of the BP-based detection increases exponentially only with the number of the nonzero interferers, with respect to the optimal maximum a posterior (MAP) algorithms or maximum-likelihood (ML) algorithms whose computational complexity are exponential in channel length. BP-based channel detector is needed especially in the sparse ISI channel with long delay spreads and only a few nonzero interferers, such as the underwater acoustic (UWA) channels [62]. Thus it is desirable to investigate LDPC-like VLSI architectures for applications under these circumstances.

Contribution: In this dissertation, we provided a feasible solution of detector architecture for random sparse ISI channels. A reconfigurable architecture was developed in order to switch flexible connections on the factor graph in the time-varying ISI channels. Layered decoding and task rescheduling once used in LDPC decoding were also incorporated to accelerate the iterative process. All of the tasks are managed by the control unit implemented as a finite state machine (FSM). The proposed detector is implemented using ASIC design in 90 nm CMOS process and also prototyped on an FPGA.

#### 1.4 Outline

This dissertation is outlined as follows.

Chapter 2 reviews the fundamentals of LDPC codes and their decoding algorithms that are used throughout this dissertation. Besides standard BP, other decoding algorithms such as loosely coupled algorithm, min-sum algorithm and layered decoding algorithm are also presented.

Chapter 3 develops a ultra-high-throughput LDPC decoder architecture implementation with parallel layered decoding. We first explain how parallel layered decoding works and then presents how it can help split the critical path and eliminate the interconnect network.

In Chapter 4, a puncturing-based RC LDPC decoder architecture that supports any code rate 1/2 to 1 is designed and implemented. First we investigate various puncturing schemes and pick up the optimal one in term of error performance. Then we modify the parallel layered decoding architecture developed in Chapter 3 by adding a control block to carry out puncturing.

Chapter 5 presents a low-complexity LDPC decoder for CMMB systems. Split-memory architecture is proposed to efficiently handle the weight-2 sub-matrices. A reconfigurable architecture, which can support dual rate LDPC codes specified in the CMMB standard, is then constructed with minimal overhead;

Chapter 6 presents VLSI implementation of a BP-based detector for sparse ISI channels, such as underwater acoustic channel. Cache-like architecture is developed by storing only the messages that current node interferes with.

Chapter 7 draws the conclusion.

# Chapter 2

# LDPC Codes and Decoding

# Algorithms

In this Chapter, we reviews some fundamentals of LDPC codes, QC LDPC codes and their decoding algorithms, including standard BP algorithm, min-sum algorithm, loosely coupled algorithm and layered decoding algorithm.

# 2.1 Introduction of LDPC Codes

The LDPC codes can be described by a  $M \times N$  sparse parity check matrix  $\mathbf{H}$ , in which most of the elements are 0's and only a few are 1's. M denotes the number of parity check equations, that is, number of the check nodes, while N is the block length, that is, the number of variable nodes. Fig. 2.1(a) shows a rate-1/2 4×8 parity check matrix of a regular (8,4) LDPC code. In the decoding aspect, a parity check matrix can be mapped into a bipartite graph, called the Tanner graph, with all of the variable nodes on one side and check nodes on another. Locations of the non-zero elements in the  $\mathbf{H}$  matrix indicate the straight connections between variable

$$\mathbf{H} = \begin{bmatrix} 1 & 1 & 0 & 0 & 0 & 1 & 1 & 0 \\ 0 & 0 & 1 & 1 & 1 & 0 & 0 & 1 \\ 1 & 0 & 0 & 1 & 0 & 1 & 1 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 & 1 \end{bmatrix}$$

(a)

Check Nodes

VTC Message

Variable Nodes

v1 v2 v3 v4 v5 v6 v7 v8

(b)

Figure 2.1: Regular (8,4) LDPC codes: (a) Parity-check matrix (b) Tanner graph nodes and check nodes, as illustrated in Fig. 2.1 (b). These connections can be also considered as the messages (CTV messages and VTC messages) transmitting paths when decoding using the iterative BP algorithm.

# 2.2 Quasi-Cyclic LDPC Codes

QC LDPC codes are a special class of the LDPC codes with structured  $\mathbf{H}$  matrix which can be generated from an  $m_b \times n_b$  base matrix  $\mathbf{H}_b$ .

$$H_{b} = \begin{bmatrix} \mathbf{P_{0,0}} & \mathbf{P_{0,1}} & \cdots & \mathbf{P_{0,n_{b}-1}} \\ \mathbf{P_{1,0}} & \mathbf{P_{1,1}} & \cdots & \mathbf{P_{1,n_{b}-1}} \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{P_{m_{b}-1,0}} & \mathbf{P_{m_{b}-1,1}} & \cdots & \mathbf{P_{m_{b}-1,n_{b}-1}} \end{bmatrix}$$

(2.1)

Each nonzero element  $\mathbf{P_{i,j}}$  in the base matrix is a  $z \times z$  submatrix that can be expanded by circularly right-shifting an identity matrix with the shift value defined by  $\mathbf{P_{i,j}}$ . The structure of the parity check matrix makes it convenient to

determine the locations of the nonzero elements. Random connections between CNUs and VNUs now become well-regulated and easy to handle. Therefore, QC-LDPC codes are welcomed by several advanced communication standards, such as 802.11n, 802.15.3c and 802.16e.

### 2.3 Belief Propagation Algorithm

The BP algorithm provides an efficient and powerful method to decoding LDPC codes. Standard BP algorithm in [24] is usually transformed into logarithmic domain where additions can be used instead of the complex multiplication. Before presenting the BP algorithm, we first make some definitions as follows: Let  $c_n$  denote the n-th bit of a codeword and  $y_n$  denote the corresponding received value from the channel. Let  $r_{mn}[k]$  ( $q_{mn}[k]$ ) be the CTV (VTC) message from check node m to variable node n at the k-th iteration. Let N(m) denote the set of variables that participate in check m and M(n) denote the set of checks that participate in variable n. The set N(m) without variable n is denoted as  $N(m) \setminus n$  and the set M(n) without check m is denoted as  $M(n) \setminus m$ .

#### 1. Initialization:

Under the assumption of equal priori probability, compute the channel probability  $p_n$  (intrinsic information) of the variable node n, by:

$$p_n = \log \frac{P(y_n \mid c_n = 0)}{P(y_n \mid c_n = 1)}$$

(2.2)

The CTV message  $r_{mn}$  is set to be zero.

#### 2. Iterative Decoding:

At the k-th iteration, for the variable node n, calculate VTC message  $q_{mn}[k]$

by

$$q_{mn}[k] = p_n + \sum_{m' \in \{M(n) \setminus m\}} r_{m'n}[k-1]$$

(2.3)

Meanwhile, the decoder can make a hard decision by calculating the APP (a-posterior probability) by

$$\Lambda_n[k] = p_n + \sum_{m' \in M(n)} r_{m'n}[k-1]$$

(2.4)

Decide the *n*-th bit of the decoded codeword  $x_n = 0$  if  $\Lambda_n > 0$  and  $x_n = 1$  otherwise. The decoding process terminates when the entire codeword  $x = [x_1, x_2, \dots, x_N]$  satisfy all of the M parity check equations:  $\mathbf{H}x = 0$ , or the preset maximum number of iteration is consumed.

If the decoding process does not stop, then, calculate the CTV message  $r_{mn}$  for the check node m, by

$$r_{mn}[k] = \prod_{n' \in \{N(m) \setminus n\}} sign(q_{mn'}[k])$$

$$\times \Psi^{-1}\left(\sum_{n' \in \{N(m) \setminus n\}} \Psi(|q_{mn'}[k]|)\right)$$

$$(2.5)$$

$$\Psi(x) = \Psi^{-1}(x) = \log \frac{1 + e^{-x}}{1 - e^{-x}}$$

(2.6)

#### 2.4 Min-Sum Algorithm

The nonlinear log - tanh function in the check node updating step is usually implemented by Look-Up Table (LUT), which seriously increases the complexity and operating latency of the CNU. In paper [78], the author proposed a method to balance the path latency of CNU and BNU by transferring one of the two log-tanh

functions from CNU to BNU. Another effective method is to use the min-sum algorithm to lower the CNU complexity by approximating the CTV message with a minimum operation, as shown in (2.7).

$$r_{mn}[k] = \prod_{n' \in \{N(m) \setminus n\}} sign(q_{mn'}[k]) \times \left(\min_{n' \in \{N(m) \setminus n\}} \{|q_{mn'}[k]|\} \times \alpha\right)$$

$$(2.7)$$

Here, a normalized factor  $\alpha$  is introduced to compensate for the performance loss exiting in the min-sum algorithm without compensation compared to BP algorithm [23, 26, 10]. In this dissertation,  $\alpha$  is set to be 0.75.

Using the min-sum algorithm, the look-up tables (LUTs) which implement the intricate non-linear function in standard BP algorithm are now replaced by rather simple comparators, resulting in simpler computation complexity of CNU. Besides, storage resources can also be reduced, as only the minimum and second minimum value of all of the VTC messages within a check node need to be stored.

## 2.5 Loosely Coupled Algorithm

In the BP algorithm, messages are transmitted between check nodes and variable nodes iteratively to update each other. VTC messages are renewed by channel probabilities and CTV messages from the check nodes. Then, these renewed messages need to be passed again to update the VTC messages. Every VTC and CTV message should be transmitted immediately after they are renewed along the edges on the Tanner graph. This large amount of transmitted messages causes an interconnection problem. Large chip area is occupied by interconnections and an area-efficient decoder becomes a challenge.

Loosely coupled algorithm [36] was introduced to solve the complex interconnection problem. The decoder does not exchange the CTV and VTC messages between the check nodes and variable nodes. Instead, it delivers only the check and variable summation  $\Delta_m$  and  $\Lambda_n$ . At a variable node, given the check summation values  $\Delta_m$ , a VNU would first recover individual CTV message  $r_{mn}$  and then calculate the next variable summation  $\Lambda_n$  which will be transmitted to CNUs. As a result, (2.3) and (2.4) can now be modified as:

$$r_{mn}[k-1] = (sign(\Delta_m[k-1]) \times sign(q_{mn}[k-1]))$$

$\times \Psi^{-1}(\Psi(|\Delta_m[k-1]|) - \Psi(|q_{mn}[k-1]|))$  (2.8)

$$\Lambda_n[k] = p_n + \sum_{m' \in M(n)} r_{m'n}[k-1]$$

(2.9)

$$q_{mn}[k] = p_n + \sum_{m' \in \{M(n) \setminus m\}} r_{m'n}[k-1]$$

(2.10)

Similarly, at a check node, given the variable summation values  $\Lambda_n$ , a CNU would first recover individual VTC message  $q_{mn}$  and then calculate the next check summation  $\Delta_m$  which will be transmitted to VNUs. As a result, (2.5) can now be modified as:

$$q_{mn}[k] = \Lambda_n[k] - r_{mn}[k-1]$$

(2.11)

$$\Delta_{m} [k] = \prod_{n' \in N(m)} sign (q_{mn'} [k])$$

$$\times \Psi^{-1} \left( \sum_{n' \in N(m)} \Psi (|q_{mn'} [k]|) \right)$$

$$(2.12)$$

$$r_{mn}[k] = \prod_{n' \in \{N(m) \setminus n\}} sign(q_{mn'}[k])$$

$$\times \Psi^{-1}\left(\sum_{n' \in \{N(m) \setminus n\}} \Psi(|q_{mn'}[k]|)\right)$$

(2.13)

If the min-sum algorithm is also applied, then we only need to transmit the variable summation  $\Lambda_n$ , leading to further simplification in interconnection complexity [70].

## 2.6 Early Termination Strategy

As presented in the BP algorithm, the decoding process can be terminated by two general conditions: one is the parity check equations  $\mathbf{H}x=0$ , another is the actual number of iterations exceeds the predefined maximum number. For regular LDPC code decoding in paper [85], parity check equations become easy to verify, because every clock cycles the decoded bits from the VNUs are within a same check and parity check can be completed immediately after the decoded bits are decided. However, for irregular codes such parity check method would lead to larger hardware resource, longer decoding latency and lower decoding throughput, because extra storage resources and clock cycles are required to save the hard decision bits and to verify to see if the parity check equations are satisfied.

Another conventional termination method is to only set the maximum number of iterations and stop at the preset number without considering if the parity check equations are satisfied. The method will have little hurt to the error-correction performance of the LDPC codes if the maximum number if sufficiently large. In circuit level design, a simple counter will be fine to fully implement this termination method. Thus, less hardware complexity is employed, compared with the parity check equation method. However, the method cannot arbitrarily adjust the num-

ber of iterations and will cause a waste in high SNR channels such as wire-line environments where fewer errors occur.

In order to address the drawbacks of the two existing termination criteria, we propose a more convenient and robust "early termination" strategy [66] to balance the throughput requirements and hardware usage. The early termination strategy can not only dynamically adjust the number of iterations when dealing with communication channels of different SNRs, but also be sufficient for the low-cost and low-power hardware implementation.

The pivot of the early termination strategy lies in that hard decisions from previous iteration are stored and compared with newly generated hard decisions. If all of the decoded bits at current iteration are identical with those of the previous iteration, then the decoder indicates a successful decoding of current codeword and jumps out of the iterative process. Otherwise, the decoding process would continue until two successive hard decisions become the same or the maximum number of iterations is satisfied. As indicated in [66], for the LDPC code used in this paper, we only need to check 1152 information bits instead of 2304 bits, because it is a rate-1/2 systematic linear block code.

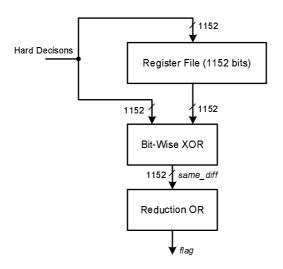

Fig. 2.2 shows the hardware architecture of the early termination strategy. It mainly consists of XOR gates, OR gates and registers which are used to save the hard decisions. At every iteration cycle, hard decisions of previous iteration are retrieved from registers and XORed with current decisions to generate an array of intermediate signals  $same\_diff$ . Then each bits of the  $same\_diff$  signal are ORed to generate the flag signal. A high-level flag signal indicates difference of hard decisions between the two successive iterations and then the decoding process will continue if the predefined number of iteration is not satisfied. Otherwise, a low-level flag signal tells identity of the two successive hard decisions and the process

Figure 2.2: Implementation of early termination strategy

will stop.

## 2.7 Layered Decoding Algorithm

In BP algorithm [24], the two-phase mutual messages, namely VTC messages  $q_{mn}$  and CTV messages  $r_{mn}$ , are updated by separate processing units and passed to each other iteratively.  $q_{mn}$  updates will not start until all of the  $r_{mn}$  are prepared and vice versa. In horizontal layered decoding, the CTV message from the current layer will be passed vertically to all other unprocessed layers that belong to the same variable node. In each iteration, the horizontal layers are processed sequentially from the top to the bottom layer.

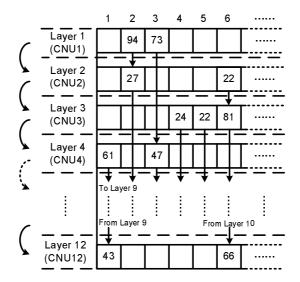

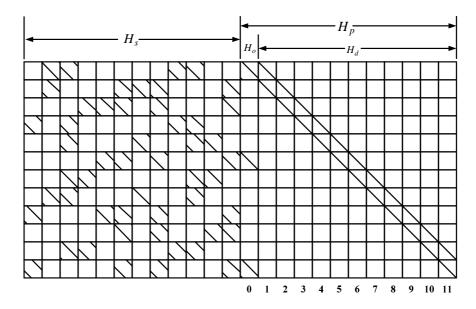

As an example, the **H** matrix of rate-1/2 LDPC code from 802.16e standard is quasi-cyclic, which consists of sub-matrices that are generated by circularly shifting an identity matrix, as shown in Fig. 2.3. Such structure is well suited for horizontal layered decoding as each sub-matrix has the column weight of one and we can treat each row of the base matrix as a layer. Message passing flow of layered decoding for the selected **H** matrix is illustrated in Fig. 2.4.

|    | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 1  |    | 94 | 73 |    |    |    |    |    | 55 | 83 |    |    | 7  | 0  |    |    |    |    |    |    |    |    |    |    |

| 2  |    | 27 |    |    |    | 22 | 79 | 9  |    |    |    | 12 |    | 0  | 0  |    |    |    |    |    |    |    |    |    |

| 3  |    |    |    | 24 | 22 | 81 |    | 33 |    |    |    | 0  |    |    | 0  | 0  |    |    |    |    |    |    |    |    |

| 4  | 61 |    | 47 |    |    |    |    |    | 65 | 25 |    |    |    |    |    | 0  | 0  |    |    |    |    |    |    |    |

| 5  |    |    | 39 |    |    |    | 84 |    |    | 41 | 72 |    |    |    |    |    | 0  | 0  |    |    |    |    |    |    |

| 6  |    |    |    |    | 46 | 40 |    | 82 |    |    |    | 79 | 0  |    |    |    |    | 0  | 0  |    |    |    |    |    |

| 7  |    |    | 95 | 53 |    |    |    |    |    | 14 | 18 |    |    |    |    |    |    |    | 0  | 0  |    |    |    |    |

| 8  |    | 11 | 73 |    |    |    | 2  |    |    | 47 |    |    |    |    |    |    |    |    |    | 0  | 0  |    |    |    |

| 9  | 12 |    |    |    | 83 | 24 |    | 43 |    |    |    | 51 |    |    |    |    |    |    |    |    | 0  | 0  |    |    |

| 10 |    |    |    |    |    | 94 |    | 59 |    |    | 70 | 72 |    |    |    |    |    |    |    |    |    | 0  | 0  |    |

| 11 |    |    | 7  | 65 |    |    |    |    | 39 | 49 |    |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  |

| 12 | 43 |    |    |    |    | 66 |    | 41 |    |    |    | 26 | 7  |    |    |    |    |    |    |    |    |    |    | 0  |

Figure 2.3: Parity-check matrix for the selected rate-1/2 LDPC code in 802.16e standard.

Figure 2.4: Message passing flow in horizontal layered decoding.

Figure 2.5: Architecture of horizontal layered decoding with loosely coupled algorithm.

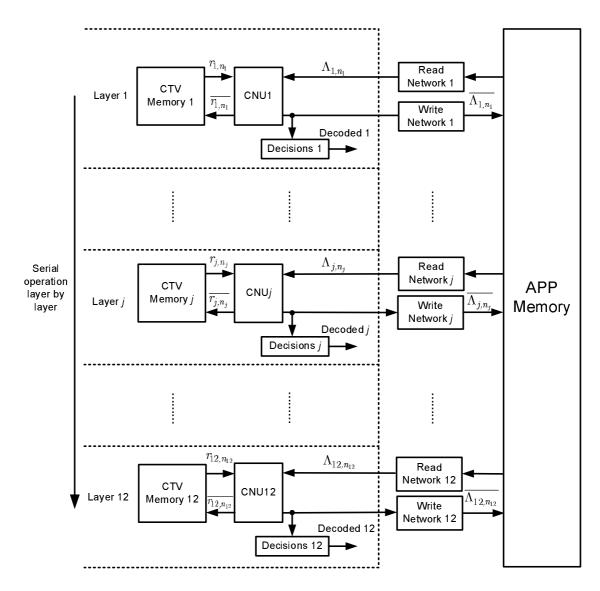

Loosely coupled algorithm is also adopted in this work to reduce the interconnection complexity. As illustrated in Fig. 2.5, at the j-th layer, the VTC messages are first recovered from the variable summations  $\Lambda_n$  and the CTV message from memories, as in (6). At the output of CNUj, the updated CTV messages  $\{r_{j,n_j} \mid n_j \in N(j)\}$  in (7) are stored back to the CTV memories. Variable summation  $\{\Lambda_{n_j} \mid n_j \in N(j)\}$  are renewed as in (8) and sent back to the APP memory. The entire flow can be expressed as follows:

$$q_{j,n_j} = \Lambda_{n_j} - r_{j,n_j} \tag{2.14}$$

$$\overline{r_{j,n_{j}}} = \left( \prod_{n'_{j} \in \{N(j) \setminus n_{j}\}} sign\left(q_{j,n'_{j}}\right) \right) \times \left( \min_{n'_{j} \in \{N(j) \setminus n_{j}\}} \left\{ \left| q_{j,n_{j}} \right| \right\} \times \alpha \right)$$

(2.15)

$$\overline{\Lambda_{n_j}} = q_{j,n_j} + \overline{r_{j,n_j}} \tag{2.16}$$

Compared with conventional layered decoding algorithm, it can be observed that loosely coupled algorithm does not require variable node operations. In other words, VNUs can be eliminated since their main function of updating the variable summations  $\Lambda_n$  can be done by CNUs using VTC messages  $r_{j,n_j}[k]$  from previous layers, as indicated in (2.16).

# Chapter 3

# High-Throughput LDPC Decoder Architecture with Parallel Layered Decoding

## 3.1 High Throughput Strategies

With the increasing demand for high-data-rate wireless applications, many recent communication systems employ ultra-high throughput channel codes to match the data-rate requirements. For example, 802.15.3c standard is targeted for the data rate of multi-giga bits per second (Gbps), thus LDPC codes are preferred compared with convolutional codes and Turbo codes. However, it is a great challenge to design a high-through LDPC decoder due to the complexity of decoding algorithm. Since QC-LDPC codes are increasingly popular in emerging communication standards, we focus on the design and architecture of QC-LDPC decoder in this paper.

The throughput of an LDPC decoder can be calculated as

$$Throughput = \frac{Freq \times Block \, Length}{Cycles \, per \, Iter \times Num \, of \, Iter} \tag{3.1}$$

Therefore, three strategies can be attempted in order to improve the throughput: reducing the number of iterations required for convergence, reducing the decoding latency per iteration and improving the operating frequency. Correspondingly, three architecture-aware schemes are studied in this paper, including layered decoding algorithm, parallel layered decoding architecture, and critical path splitting technique.

First, layered decoding algorithm is adopted to reduce the required number of iterations by a factor of two for any given SNR, compared with the standard BP algorithm. Hence, the decoding throughput is supposed to be doubled without any bit error performance loss. Generally, there are two layered decoding methods: horizontal layered decoding [51, 33, 45, 9, 25, 28] and vertical layered decoding [82]. It has been proved these two methods are theoretically equivalent and both can converge twice as fast as the BP algorithm [65]. In this paper, we employ the horizontal layered decoding strategy because it is favorable for the min-sum algorithm.

Secondly, we propose a novel scheme namely parallel layered decoding architecture that enables concurrent processing among all layers. In traditional layered decoding architecture, the layers are processed sequentially which leads to longer decoding latency per iteration [33]. In parallel layered decoding architecture, precisely scheduled message passing among different layers guarantees that all updated messages are passed to their designated locations in connected layers. The parity-check matrix optimization procedure adds specific offsets to each layer (row) in the base

parity check matrix, making the idle time intervals between connected layers sufficiently large for message passing. Moreover, parallel layered decoding architecture supports the decoding architecture in which check node updates unit (CNU) and variable node updates unit (VNU) are combined into a single functional unit. Thus, no extra clock cycles are needed to complete the variable node update as they have been merged into the CNU. As a result, the number of clock cycles per iteration in parallel layered decoding architecture can be reduced by 75% compared with the existing architectures.

Finally, the technique of reducing critical path delay is proposed to improve the operating frequency at circuit-level. The combination of CNU and VNU results a long critical path in the decoder implementation [66], which limits the maximum clock speed. Fortunately, there are idle time intervals among different layers which allows the iterative messages to be processed and passed to the next layer within several clock cycles. Therefore, we can insert registers to split the CNU (including the VNU) into several pipelined stages. Consequently, the critical path is split into multiple stages and the clock speed can be improved dramatically, on condition that the number of stages does not exceed the idle time intervals. In practice, this critical path splitting method can increase the maximum frequency of the decoder by a factor of 3 or higher.

To demonstrate the aforementioned three techniques, a rate-1/2 2304-bit QC-LDPC code is selected from 802.16e standard as a case study. In addition, existing techniques such as min-sum algorithm and loosely coupled algorithm are also employed to simplify decoding complexity and to reduce the chip area of the decoder design.

### 3.2 Parallel Layered Decoding Architecture

As discussed above, the essential reason that layered decoding algorithm can reduce the number of iterations is that the latest extrinsic messages are passed to and employed by the subsequent layers within the current iteration. Therefore, layered decoding requires layers to be processed sequentially, which results a large decoding latency per iteration. A method of increasing parallelism inside a layer is proposed in [51, 45], but all layers are still processed in series. Although decoding throughput can be improved, this method introduces crossbar-based interconnection networks that increase the hardware complexity.

Motivated by the partly parallel mechanism mentioned in [85], we propose the parallel layered decoding architecture that allows all layers to be processed concurrently. Each layer generates and sends updated messages and at the same time it also receives the updated messages from other layers. Unlike the method proposed in [51, 45], parallel layered decoding architecture uses parallel processing among all layers and serial processing within each layer. Detailed message processing flow at the j-th layer (CNU) can be summarized as

- 1. Fetch the corresponding variable summations  $\{\Lambda_{n_j} \mid n_j \in N(j)\}$  from the APP memory and CTV messages  $\{r_{j,n_j} \mid n_j \in N(j)\}$  from local CTV memory.

- 2. Calculate the VTC messages  $\{q_{j,n_{j}} \mid n_{j} \in N(j)\}$  in the same row using (2.14).

- 3. Calculate horizontally to obtain new CTV messages  $\{\overline{r_{j,n_j}} \mid n_j \in N(j)\}$ , as in (2.15).

- 4. Immediately update the variable summations  $\{\overline{\Lambda_{n_{j}}} \mid n_{j} \in N(j)\}$  using (2.16).

- 5. Deliver the new variable summation  $\overline{\Lambda_{n_j}}$  to the same location at another layer.

Hereby, we explain how to pass  $\overline{\Lambda_{n_j}}$  messages in parallel layered decoding architecture. Instead of passing  $\overline{\Lambda_{n_j}}$  to all unprocessed layers as in conventional layered decoding, parallel layered decoding architecture only sends  $\overline{\Lambda_{n_j}}$  to the layer that will use it next. Let us take the first column of the **H** base matrix as an example. None-zero entries are at the 4th, 9th and 12th layer whose permutation numbers are 61, 12 and 43, respectively. Now we suppose that at cycle 0 each of these three corresponding CNUs starts to process from the first row of the sub-matrix, corresponding to the 62th, 13th and 44th column indices. In general, corresponding row and column indices of the entry being processed at cycle l can be calculated as

$$r_{index} = l (3.2)$$

$$c_{index} = mod (l + 1 + s (i, j), 96)$$

(3.3)

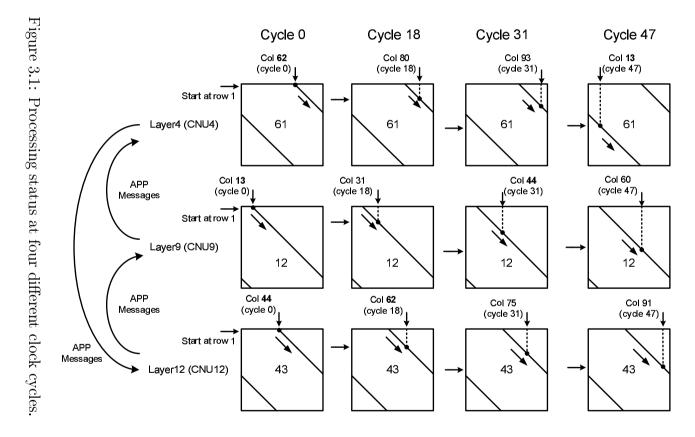

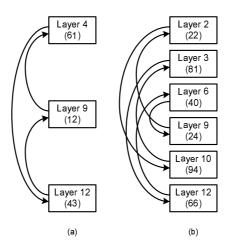

In Fig. 3.1, it illustrates the message passing routes in parallel layered decoding architecture using the the first column of the parity check matrix in Fig. 1 as an example. The operation sequence in time of these three layers is described as the following:

- 1. At cycle 0, CNUs at layers 4, 9 and 12 start to process simultaneously from row 1 of each sub-matrix, corresponding to column 62, column 13 and column 44 according to (3.3).

- 2. At cycle 18, all three layers are processing at row 19, corresponding to column 80 (in layer 4), column 31 (in layer 9) and column 62 (in layer 12). Layer 12 calls for the latest summation message of column 62 which has already been updated by layer 4. Therefore, the updated variable summations at layer 4 should be sent to layer 12 (Layer 4 →Layer 12).

Figure 3.2: Variable summations passing directions of the **H** base matrix: (a) for column 1 (b) for column 6.

- 3. At cycle 31, all three layers are processing at row 32, corresponding to column 93 (in layer 4), column 44 (in layer 9) and column 75(in layer 12). Layer 9 calls for the latest summation message of column 44 which has already been updated by layer 12. Therefore, the updated variable summations at layer 12 should be sent to layer 9 (Layer 12 →Layer 9).

- 4. Similarly, at cycle 47, all three layers are processing row 48, corresponding to column 13 (in layer 4), column 60 (in layer 9) and column 91 (in layer 12). Layer 4 calls for latest summation message of column 13 which has already been updated by layer 9. Therefore, the updated variable summations at layer 9 should be sent to layer 4 (Layer 9 →Layer 4).

Based on the description above, message passing routes for column 1 of base matrix is shown in Fig. 3.2(a). An additional example is illustrated in Fig. 3.2(b) for column 6 of the base matrix. In general, we can determine the message passing routes among layers based on the their permutation values. For each column, we can sort the permutation values of all layers in descending order. Each layer then passes messages to the next layer with a smaller permutation value. Moreover, the

| Layer | Offset | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

|-------|--------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 1     | +0     |    | 94 | 73 |    |    |    |    |    | 55 | 83 |    |    | 7  | 0  |    |    |    |    |    |    |    |    |    |    |

| 2     | +8     |    | 35 |    |    |    | 30 | 87 | 17 |    |    |    | 20 |    | 8  | 8  |    |    |    |    |    |    |    |    |    |

| 3     | +0     |    |    |    | 24 | 22 | 81 |    | 33 |    |    |    | 0  |    |    | 0  | 0  |    |    |    |    |    |    |    |    |

| 4     | +12    | 73 |    | 59 |    |    |    |    |    | 77 | 37 |    |    |    |    |    | 12 | 12 |    |    |    |    |    |    |    |

| 5     | +84    |    |    | 27 |    |    |    | 72 |    |    | 29 | 60 |    |    |    |    |    | 84 | 84 |    |    |    |    |    |    |

| 6     | +0     |    |    |    |    | 46 | 40 |    | 82 |    |    |    | 79 | 0  |    |    |    |    | 0  | 0  |    |    |    |    |    |

| 7     | +88    |    |    | 87 | 45 |    |    |    |    |    | 6  | 10 |    |    |    |    |    |    |    | 88 | 88 |    |    |    |    |

| 8     | +8     |    | 27 | 81 |    |    |    | 10 |    |    | 55 |    |    |    |    |    |    |    |    |    | 8  | 8  |    |    |    |

| 9     | +0     | 12 |    |    |    | 83 | 24 |    | 43 |    |    |    | 51 |    |    |    |    |    |    |    |    | 0  | 0  |    |    |

| 10    | +16    |    |    |    |    |    | 14 |    | 75 |    |    | 86 | 88 |    |    |    |    |    |    |    |    |    | 16 | 16 |    |

| 11    | +0     |    |    | 7  | 65 |    |    |    |    | 39 | 49 |    |    |    |    |    |    |    |    |    |    |    |    | 0  | 0  |

| 12    | +80    | 27 |    |    |    |    | 50 |    | 25 |    |    |    | 10 | 87 |    |    |    |    |    |    |    |    |    |    | 80 |

Figure 3.3: Offset-modified parity-check matrix for rate-1/2 LDPC code in 802.16e.

Figure 3.4: Timing diagram for parallel layered decoding architecture.

layer with the smallest permutation value loops back and connects to the layer with the largest value. This message passing scheme guarantees the updated messages among all layered are processed progressively within each iteration.

### 3.3 Critical Path Splitting

According to the message passing mechanism explained above, we suppose CNUs in all layers start at row 1 of each sub-matrix. Actually, the CNUs can start to operate from different rows, which is equivalent to adding an offset to the permutation value of each layer. For example, Fig. ?? shows a modified **H** base matrix with a set of offset values added for different layers. The offset values are carefully selected, such that the difference of modified permutation values between any two layers is

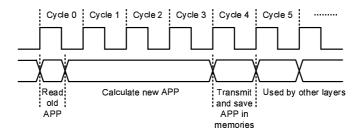

at least 5. It means each layer needs to read, update, store and pass the message to the next connected layer with 5 clock cycles. The detail steps for the processing in a layer are shown in Fig. 3.4. In other words, each CNU has a period of 4 cycles to complete the task of reading old message and update new message, as indicated in (2.14) to (2.16). The message passing rule remains the same, except that the updated permutation values should be used to determine the connections in PLDA.

From Fig. 3.3, we can see that the row weight of each layer is either 6 or 7, which requires 6 or 7 messages to be compared in the CNU. Combined with other necessary functions such as adding, rounding and memory read/write, CNU becomes the critical path that limits the maximum operating frequency of the decoder. Taking advantage of the 4-cycle time intervals, we can split the critical path of CNU into 4 pipelined stages by inserting 3 levels of registers. An optimal splitting yields balanced delays among the pipeline stages. The implementation of critical path splitting will be given in Section 3.4.2.

### 3.4 Proposed Decoder Architecture

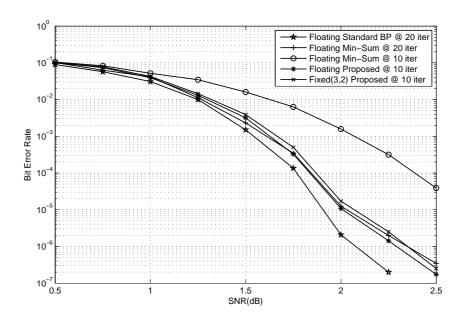

In order to prove the concept of our proposed parallel layered decoding architecture and high-throughput strategies, a rate-1/2 2304-bit QC-LDPC code selected from 802.16e standard is designed based on the offset-modified **H** matrix. The size of each sub-matrix is chosen to be 96 × 96. Before constructing the functional units of the decoder, we first perform fixed-point analysis to quantize the word-length of messages. In fact, word-length quantization is a tradeoff between memory resources and bit-error-rate performance. Fig. 3.5 shows the BER performance of the selected rate-1/2 LDPC code using message word-length (3,2). As demonstrated in [?], 5 bits (3 bits for the integer part and 2 bits for the fractional part) are adequate

Figure 3.5: BER performance comparison of different decoding algorithms.

for representing the absolute values of the extrinsic messages. Considering one additional sign bit, we choose 6 bits fixed-point representation for messages in this implementation.

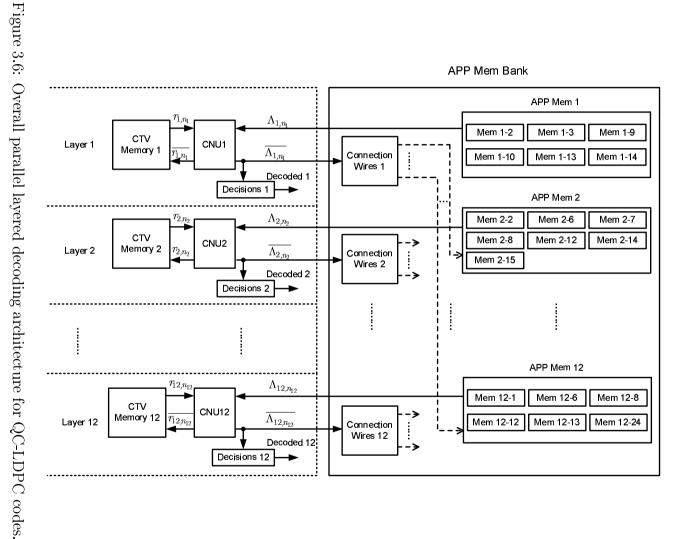

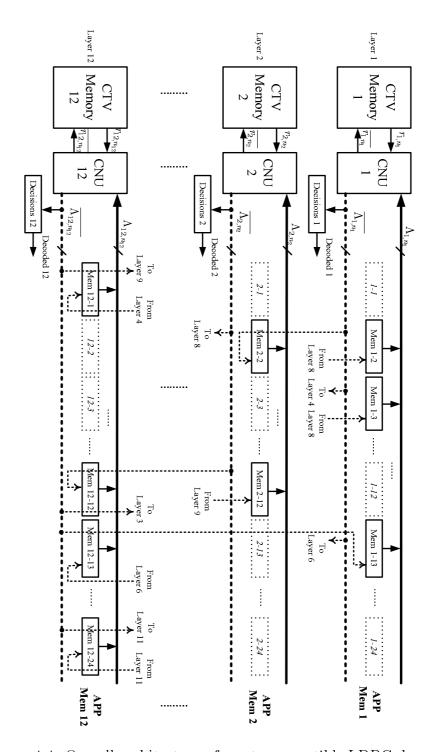

#### 3.4.1 Overall Decoder Architecture

The overall architecture of the QC-LDPC decoder is shown in Fig. 3.6. It consists of check node processing units (CNUs), APP memory banks, CTV memory banks and hard-decision units. The entire **H** matrix is divided into 12 layers and each layer employs a dedicated CNU. APP memory banks and CTV memory banks are used to store variable summations and CTV messages. Each non-zero submatrix corresponds to one APP memory unit and one CTV memory unit. In layered decoding, each APP memory exports a summation message to the CNU and imports a new summation message from the CNU of another layer. Similarly, each CTV memory exports a CTV message to the CNU and imports a new CTV message from the same CNU for each layer. As a result, single-port memories that support

concurrent read and write operations are used in the design. Since there are 76 submatrices in total, the APP memory bank and the CTV memory bank each consists of 76 small single-port memory units.

Each layer in the parallel layered decoding architecture corresponds to 6 or 7 APP memory units, which means that the updated variable summations of the j-th layer  $\overline{\Lambda_{j,n_j}}$  will be delivered to APP memory units in other layers based on the message passing scheme described in Section ?? and Fig. 3.2. Therefore, these variable summations are passed to their destinations through fixed connection wires instead of crossbar-based networks.

### 3.4.2 Pipelined Architecture for CNU