# FROM THEORY TO PRACTICE: EVALUATING SPARSENING FILTER DESIGNS ON A SOFTWARE-DEFINED RADIO PLATFORMS

by

Raquel Guerreiro Machado

A Dissertation

Submitted to the Faculty

of the

#### WORCESTER POLYTECHNIC INSTITUTE

in partial fulfillment of the requirements for the

Degree of Doctor of Philosophy

in

Electrical and Computer Engineering

November 2014

APPROVED:

Professor Andrew G. Klein, Engineering and Design Department,

Western Washington University (WSU), Primary Advisor

Professor Alexander M. Wyglinski, ECE Department, WPI

Professor George T. Heineman, Computer Science Department, WPI

# FROM THEORY TO PRACTICE: EVALUATING SPARSENING FILTER DESIGNS ON A SOFTWARE-DEFINED RADIO PLATFORM

Raquel Guerreiro Machado, Ph.D.

Worcester Polytechnic Institute 2014

A comprehensive analysis of a novel detection scheme for SISO wireless transmission scenarios is presented in this dissertation. The scheme, which is based on Belief-Propagation (BP) detectors, is evaluated in both a computer simulation environment and a custom-built software-defined radio test-bed. In this dissertation, we address the design aspects of BP-based receivers, including several approaches to minimize the bit error rate of MAP detectors. We also present the development of an interface framework for a software defined radio platform that aims to implement complex communication transceivers capable of prototyping the hybrid structure with a pre-filter filter and BP detector.

Numerical simulations compared the proposed schemes with an existing approaches and showed significant performance gains without requiring great computational cost at the receiver. Furthermore, experiments using GNU Radio Companion and the FMCOMMS software defined radio hardware platform confirm the correct functionality of the proposed interface, and stress tests are conducted to assess the functionality of the interface and how it deteriorates across a range of operating conditions. Finally, we present several experiments using the FMCOMMS software defined radio platform that implement the proposed BP-based receiver scheme and discuss its capabilities and limitations.

#### ACKNOWLEDGEMENTS

First and foremost, all thanks go to God, lamp to my feet and light for my path.

I would like to thank the members of my PhD committee for all their guidance and support. Thank you Prof. Klein for believing in me and allowing me to come to WPI and have an amazing learning experience. You advised me during the first and most difficult years of my PhD studies; I will be forever grateful. Thank you Prof. Wyglinski for all the opportunities, the help and support during this last year; working with you was great. Thank you Prof. Heineman for all your great advice regarding the more software-related portion of my thesis. You all inspire me to be a better person and researcher.

I would also like to thank my colleagues at WPI for every discussion, every interesting conversation, every shared frustration, every pep-talk and every moment we spent together. Quingxiong, Min, Josh, Radu, Bengi, Zoe, Matt, Kalil, Aleksi, Di and Le: you will be always in my heart. Special thanks to Travis; thank you for your patience and help with GNU Radio. Very special thanks to Jen and Paulo for the amazing help toward the completion of my dissertation; I have no words to express my gratitude. And thanks to my friends in Boston for the great time, particularly Flavio and Christin.

Finally, I'm extremely grateful for my family and all their love and support during all these years. Thanks for cheering me up all the way from Brazil; I feel privileged to be your daughter and sister. And thanks to my love, my best friend and (now) husband, Andre, for being there with me in the United States and walking together the path of a PhD degree. You were essential to this success.

## TABLE OF CONTENTS

|          | Ack        | nowledgements                                                                              |

|----------|------------|--------------------------------------------------------------------------------------------|

|          | Tabl       | e of Contents                                                                              |

|          | List       | of Abbreviations                                                                           |

|          | List       | of Symbols                                                                                 |

|          |            |                                                                                            |

| 1        | Intr       | oduction 1                                                                                 |

|          | 1.1        | Motivation                                                                                 |

|          | 1.2        | Problem Statement                                                                          |

|          | 1.3        | Proposed Solutions                                                                         |

|          | 1.4        | Contributions                                                                              |

|          | 1.5        | Dissertation Organization 10                                                               |

| •        | <b>-</b> / |                                                                                            |

| <b>2</b> |            | r-Symbol Interference Mitigation and Software Defined Radio                                |

|          |            | nnology 12                                                                                 |

|          | 2.1        | Wireless Transmission: Impairments and Mitigation                                          |

|          |            | 2.1.1 Optimal ISI Mitigation                                                               |

|          |            | 2.1.2 Sub-Optimal ISI mitigation                                                           |

|          |            | 2.1.3 Multicarrier Modulation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 21$ |

|          | 2.2        | Software Defined Radio Technology                                                          |

|          |            | 2.2.1 A Brief History                                                                      |

|          |            | 2.2.2 Anatomy of a Software-Defined Radio                                                  |

|          |            | 2.2.3 Sampling                                                                             |

|          |            | 2.2.4 Current SDR Challenges                                                               |

|          |            | 2.2.5 GNU Radio                                                                            |

|          | 2.3        | Chapter Summary 42                                                                         |

| 0        | т.         |                                                                                            |

| 3        |            | ear Sparsening Filter Design 43                                                            |

|          | 3.1        | Background                                                                                 |

|          |            | 3.1.1 BP detector in a Hybrid Structure                                                    |

|          | 3.2        | System Model                                                                               |

|          |            | 3.2.1 Receiver Structure                                                                   |

|          |            | 3.2.2 Sparsening Filter Design                                                             |

|          | 3.3        | Noise Coloration                                                                           |

|          | 3.4        | BER and SSSNR 55                                                                           |

|          | 3.5        | Numeric Simulations                                                                        |

|          | 3.6        | Chapter Summary                                                                            |

| 4        | Dec        | ision-Feedback Sparsening Filter Design 69                                                 |

| -        | 4.1        | Decision-Feedback vs Linear Equalizer                                                      |

|          | 4.1        | System Model                                                                               |

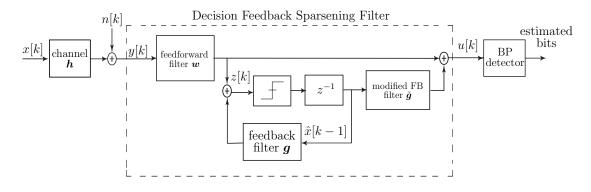

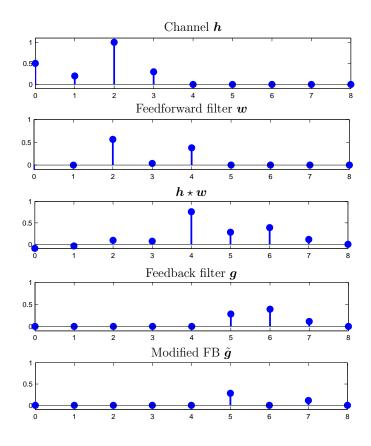

|          | 4.2<br>4.3 | Decision Feedback Sparsening Filter                                                        |

|          | 4.3<br>4.4 | Numerical Results   77                                                                     |

|          |            |                                                                                            |

|          | 4.5        | Chapter Summary 80                                                                         |

| <b>5</b> | Inte  | erface Architecture for Software Defined Radio Systems 81                                                                              |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------|

|          | 5.1   | Background                                                                                                                             |

|          |       | 5.1.1 FMCOMMS 1 RF Front End                                                                                                           |

|          |       | 5.1.2 FMCOMMS 2 RF Front End                                                                                                           |

|          |       | 5.1.3 ZedBoard and the SDR Platform                                                                                                    |

|          |       | 5.1.4 Interface with GNU Radio                                                                                                         |

|          | 5.2   | Interface Development                                                                                                                  |

|          |       | 5.2.1 Source Block $\dots \dots \dots$ |

|          |       | 5.2.2 Sink Block $\ldots$ 99                                                                                                           |

|          |       | 5.2.3 Complete Interface Experimentation                                                                                               |

|          | 5.3   | Chapter Summary                                                                                                                        |

| 6        | Spa   | rsening Filter Experimentation in SDR Platform 107                                                                                     |

|          | 6.1   | Experimentation in Baseband                                                                                                            |

|          |       | 6.1.1 Experiment Set-Up                                                                                                                |

|          |       | 6.1.2 Numerical Simulations                                                                                                            |

|          | 6.2   | Experimentation in RF Frequencies                                                                                                      |

|          |       | 6.2.1 Proposed Experiment with Channel Emulators                                                                                       |

|          |       | 6.2.2 Experiment with Simulated Channel                                                                                                |

|          |       | 6.2.3 Numerical Simulations                                                                                                            |

|          | 6.3   | Chapter Summary                                                                                                                        |

| 7        | Con   | clusions and Future Work 121                                                                                                           |

|          | 7.1   | Concluding Remarks                                                                                                                     |

|          | 7.2   | Future Work                                                                                                                            |

|          | 7.3   | Peer Review Publications                                                                                                               |

| Bi       | bliog | graphy 124                                                                                                                             |

## LIST OF FIGURES

| 1.1 | The evolution of data requirements in cellular networks. Adapted                              |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | from [1]                                                                                      | 2  |

| 1.2 | Intersymbol interference phenomenon forming the channel delay                                 |    |

|     | profile                                                                                       | 5  |

| 2.1 | High level digital transmission schematic with the equalizer filter                           | 13 |

| 2.2 | The $h = \begin{bmatrix} 1 & 0 & -1 \end{bmatrix}$ channel represented as a factor graph. The |    |

|     | graph is formed by bit nodes, which are the channel inputs $(x[.])$                           |    |

|     | and the check nodes, which are the channel outputs $(y[\cdot])$ . The                         |    |

|     | connections between bit nodes and check nodes represent the de-                               |    |

|     | pendencies between the received and transmitted symbols                                       | 17 |

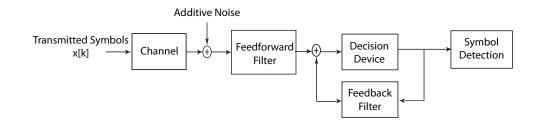

| 2.3 | Decision-feedback equalizer structure with feedforward and feed-                              |    |

|     | back filters and decision device                                                              | 20 |

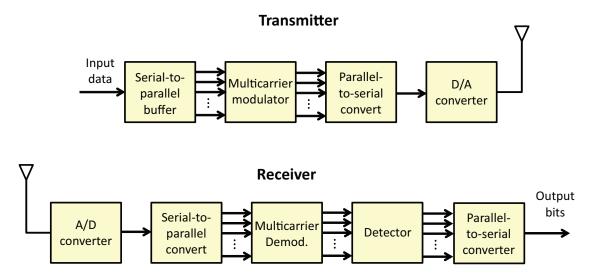

| 2.4 | Block diagram representing a multicarrier transmission system. For                            |    |

|     | the transmission, the information is first parallelized to be modu-                           |    |

|     | lated and in the receiver, the information is also parallelized to be                         |    |

|     | demodulated and detected.                                                                     | 22 |

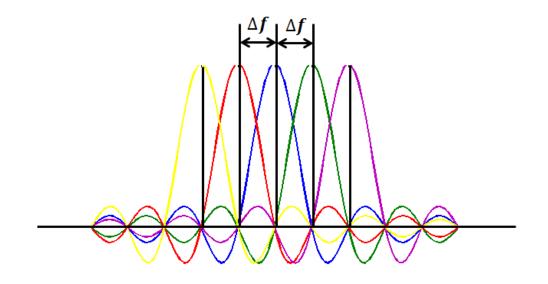

| 2.5 | Orthogonal subcarriers in a OFDM scheme. The subcarriers are                                  |    |

|     | separated by a $\Delta f$ frequency spacing.                                                  | 23 |

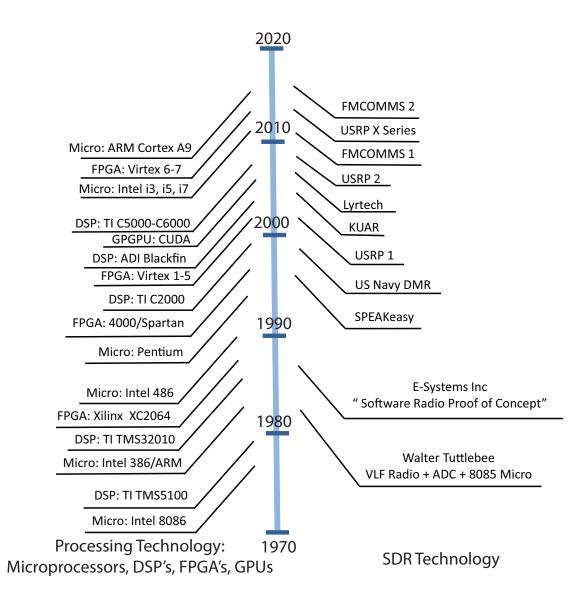

| 2.6 | Processing technology vs. SDR technology. The timeline of the past                            |    |

|     | decades shows how the evolution of different types of processors had                          |    |

|     | a great impact in the development of SDR platforms                                            | 27 |

| 2.7 | The Universal Software Radio Peripheral 2 (USRP2). The software                               |    |

|     | defined radio platform developed by Ettus Research                                            | 29 |

| 2.8  | The KUAR radio. Source: $[2]$                                                   | 30 |

|------|---------------------------------------------------------------------------------|----|

| 2.9  | Block Diagram showing the Digital and Analog divide in a Software-              |    |

|      | Defined Radio Platform. The digital signal processing is performed              |    |

|      | in the digital domain in baseband, while the analog portion of the              |    |

|      | system performs the RF operations. Based on [3], Figure 5                       | 33 |

| 2.10 | Block diagram of a typical RF Front-End. In the transmitter path,               |    |

|      | the the analog signal is modulated and transmitted in RF frequen-               |    |

|      | cies. In the receiver path, the analog high-frequency signal is con-            |    |

|      | verted to baseband before being processed by the ADC. The local                 |    |

|      | oscillator (LO) drives both transmitter and receiver circuits. $\ . \ .$        | 36 |

| 2.11 | The GNU Radio Companion (GRC) tool. It allows design of com-                    |    |

|      | munication systems using pre-made and custom blocks. $\ldots$ . $\ldots$        | 41 |

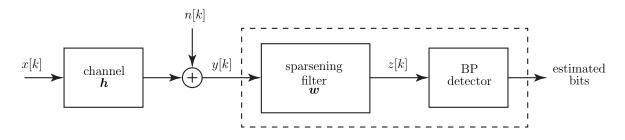

| 3.1  | System Model                                                                    | 47 |

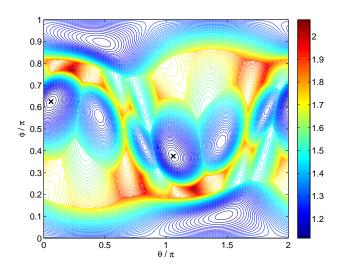

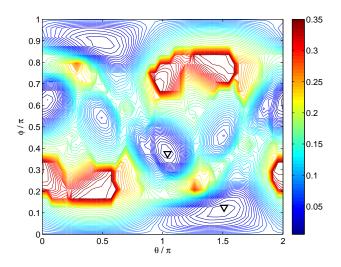

| 3.2  | Contours of Sparse Shortening SNR (SSSNR) for a three-tap unit                  |    |

|      | norm filter, parameterized by two angles in spherical coordinates.              |    |

|      | The $\times$ indicates the filter with the highest SSSNR                        | 56 |

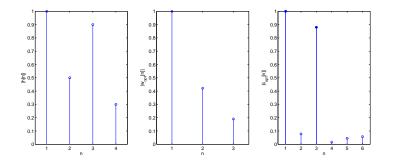

| 3.3  | Channel, filter, and effective channel tap magnitudes, using the                |    |

|      | SSSNR-optimal 3-tap filter                                                      | 56 |

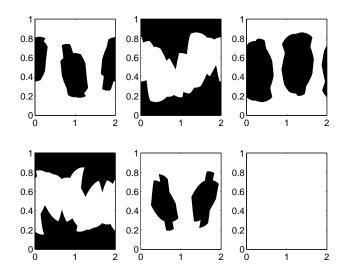

| 3.4  | Usage maps of the 6 taps of the effective channel $\mathbf{c}$ . Axes are       |    |

|      | identical to Fig. 3.2. Dark areas indicate that the given tap is one            |    |

|      | of the $\mu$ largest taps in <b>c</b>                                           | 57 |

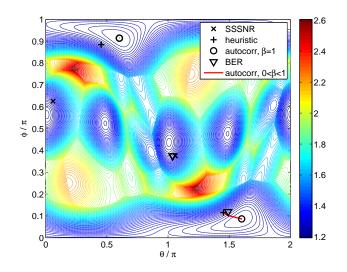

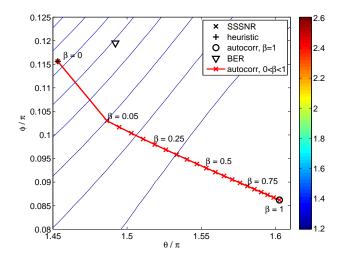

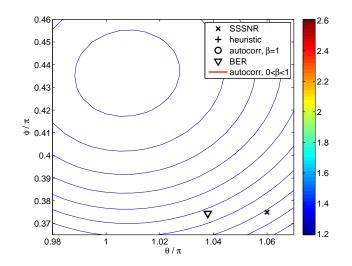

| 3.5  | Contours of bit error rate (BER) for a three-tap unit norm filter,              |    |

|      | parameterized by two angles in spherical coordinates. The $\triangledown$ indi- |    |

|      | cates the filters with the lowest BER.                                          | 58 |

| 58<br>59<br>59 |

|----------------|

|                |

| 59             |

| 00             |

| 60             |

| 61             |

|                |

| 63             |

|                |

| 65             |

|                |

|                |

| 66             |

| 66             |

| 71             |

| 76             |

| 78             |

| 79             |

|                |

|                |

|                |

| 83             |

|                |

| 85             |

|                |

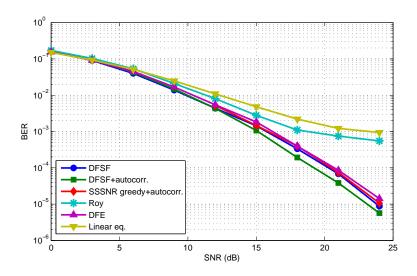

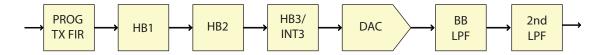

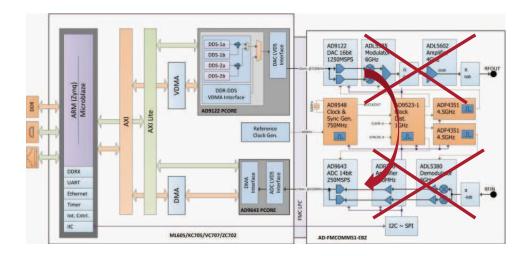

| 5 | .3  | Signal paths in the FMMCOMMS2 software-defined radio platform.              |    |

|---|-----|-----------------------------------------------------------------------------|----|

|   |     | Inside the AD9361, both TX and RX sections are composed by two              |    |

|   |     | signal paths, one for each channel (I and Q). $\ldots \ldots \ldots \ldots$ | 87 |

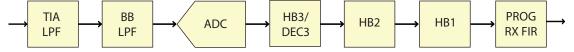

| 5 | .4  | Functional Schematics of the hardware of the SDR Platform. On               |    |

|   |     | left, we have the ZedBoard and on right we have the FMCOMMS1                |    |

|   |     | RF Front-End. The figure illustrates the transmit and receive chain         |    |

|   |     | as well as the functional blocks that are in radio transmission using       |    |

|   |     | this platform. Source: [4], used with permission                            | 89 |

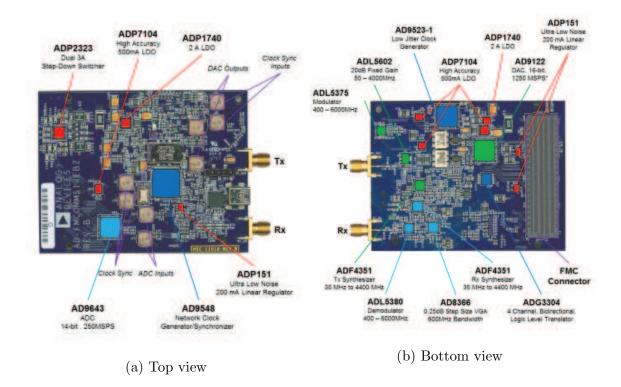

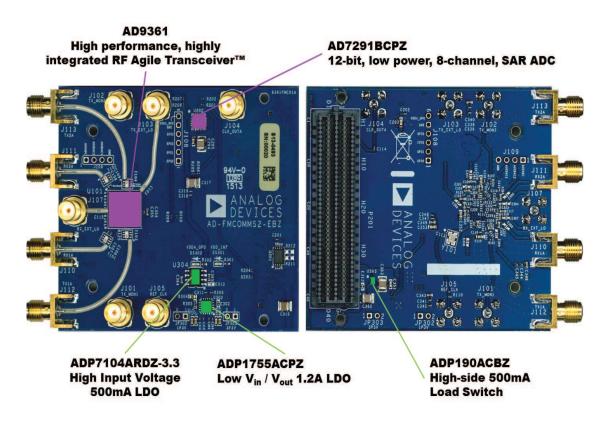

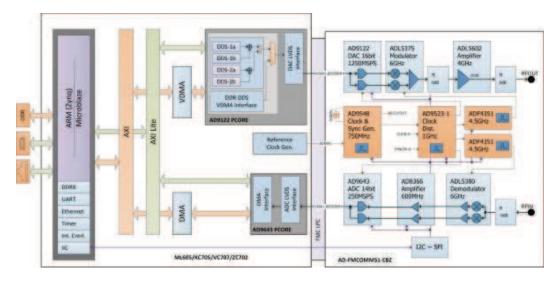

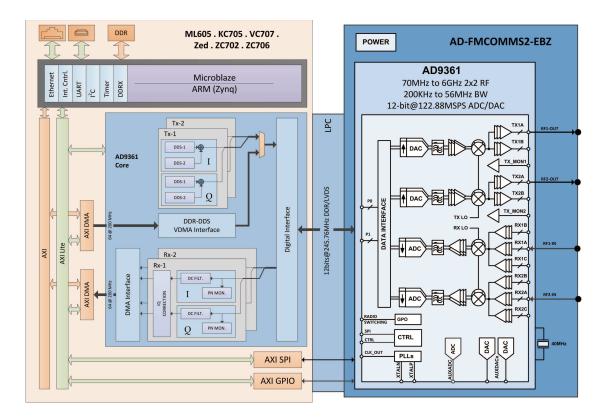

| 5 | .5  | Schematic of the software-defined radio hardware. On left, we               |    |

|   |     | have the FPGA development board and on right we have the FM-                |    |

|   |     | COMMS2 RF Front-End. The figure illustrates the transmit and                |    |

|   |     | receive chain. Source: [5], used with permission                            | 90 |

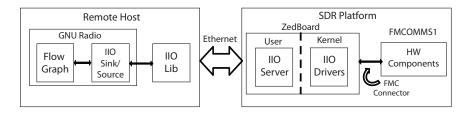

| 5 | .6  | High level illustration of the transmitting/receiving processes using       |    |

|   |     | the Ethernet connection in the ZedBoard. The sink/source blocks             |    |

|   |     | in GNU Radio communicate with the IIO drivers in the Zedboard.              | 93 |

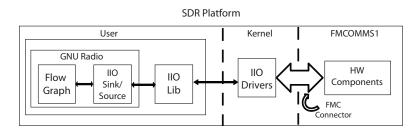

| 5 | .7  | High level illustration of the onboard transmitting/receiving pro-          |    |

|   |     | cesses. The sink/source blocks in GNU Radio communicate with                |    |

|   |     | the IIO drivers inside the same platform                                    | 94 |

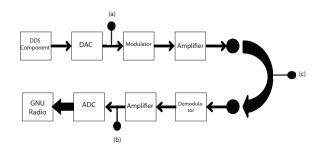

| 5 | .8  | Experiment Set-Up. The points (a), (b) and (c) show the probing             |    |

|   |     | positions for the obtained measured signals in the Results subsection       | 95 |

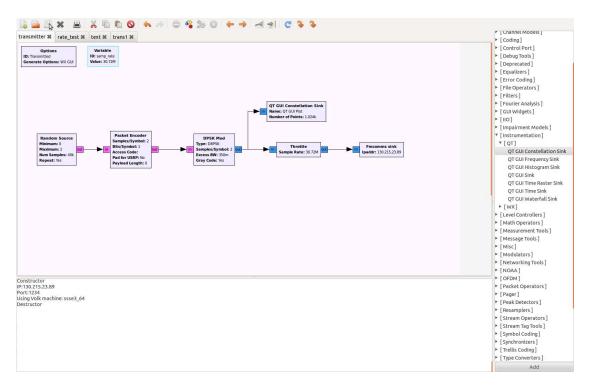

| 5 | .9  | GNU Radio Flow Graph                                                        | 96 |

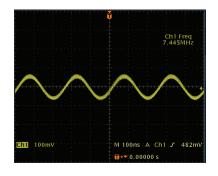

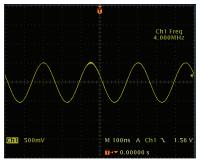

| 5 | .10 | Plots obtained by probing the FMCOMMS1 board as indicated in                |    |

|   |     | Figure 5.8. The transmitted/received signal is shown at different           |    |

|   |     | stages of the radio transmission.                                           | 97 |

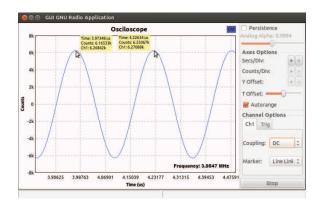

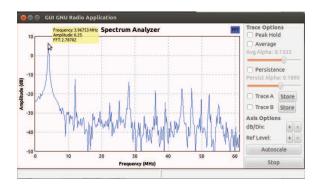

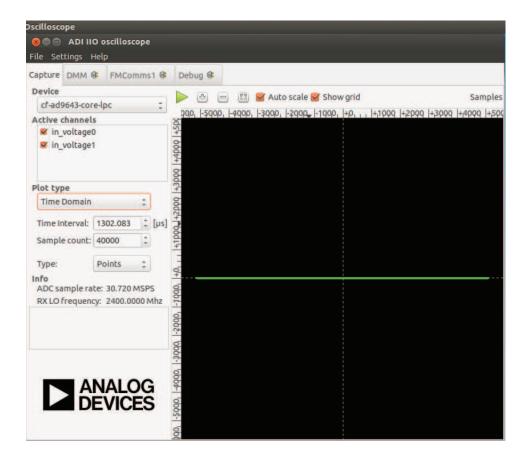

| 5.11 | View of the oscilloscope application in GNU Radio. The GUI shows               |

|------|--------------------------------------------------------------------------------|

|      | the signal sampled from the ADC and processed to be compatible                 |

|      | with the GNU Radio environment. In this figure, we see a time                  |

|      | domain plot of the signal with a measured frequency of $3.9447 \text{ MHz}$ 99 |

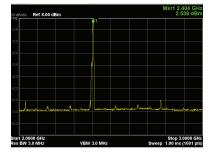

| 5.12 | View of the spectrum analyzer application in GNU Radio. The                    |

|      | GUI shows the signal sampled from the ADC and processed to be                  |

|      | compatible with the GNU Radio environment. In this picture we                  |

|      | see a frequency domain plot of the signal with a measured frequency            |

|      | of 3.96753MHz MHz                                                              |

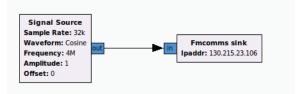

| 5.13 | GNU Radio environment for test of the sink block                               |

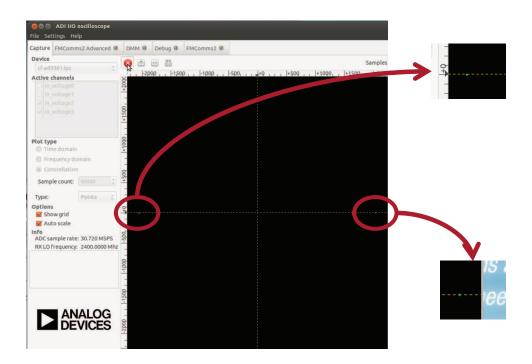

| 5.14 | Test set-up for the sink block. The signal is generated in GNU                 |

|      | Radio, passed through the RF front-end board and then analyzed                 |

|      | using ADI IIO oscilloscope tool                                                |

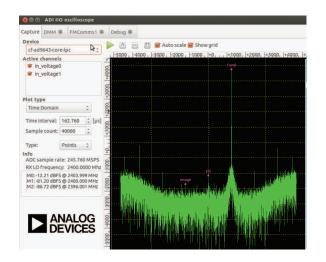

| 5.15 | ADI IIO Oscilloscope measurement                                               |

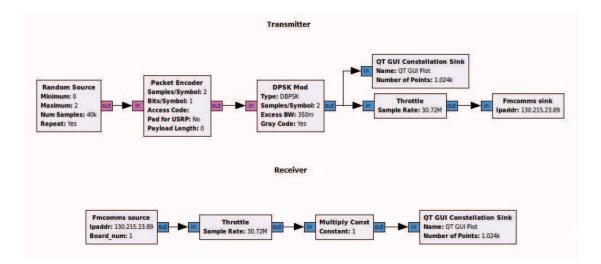

| 5.16 | Transmitter and Receiver configurations in GNU Radio. The signal               |

|      | is generated and modulated in DBPSK symbols before being sent                  |

|      | to the "Fmcomms sink". The signal goes through the transmitting                |

|      | and receiving paths in the hardware platform and the received $\mathrm{I/Q}$   |

|      | are delivered back to GNU Radio through the "Fmcomms source"                   |

|      | block                                                                          |

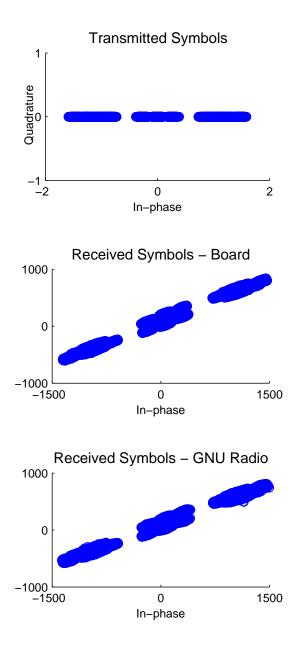

| 5.17 | Transmitted and received DBPSK symbols sent through the plat-      |

|------|--------------------------------------------------------------------|

|      | form. The transmitted symbols are generated and modulated in       |

|      | GNU Radio and sent through the transmit chain. The symbols         |

|      | are then fed back to the receive chain and can be visualized using |

|      | the ADI IIO oscilloscope tool in the ZedBoard and inside the GNU   |

|      | Radio environment                                                  |

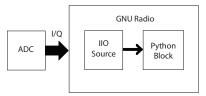

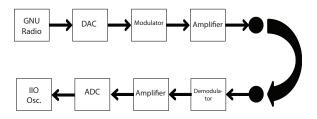

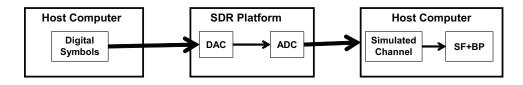

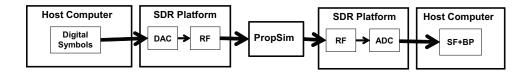

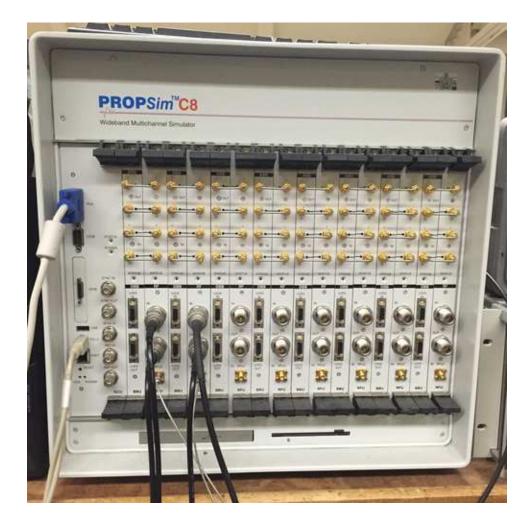

- 6.1 Experiment using the SDR platform with simulated wireless channel108

- 6.3 FMCOMMS1 board in baseband configuration. The output of the DAC is connected to the input of the ADC using SMB cables. . . . 109

- 6.4 The baseband signal received at the ADC. The BPSK symbols are scattered along the X axis making the detection operation unfeasible.110

- 6.5 The baseband signal received at the ADC. The BPSK symbols are showed as expected and the constellation can be easily identified. . 111

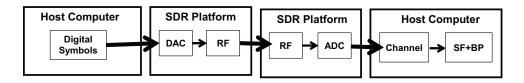

- 6.10 Experiment using the SDR platform with simulated channel. . . . 117

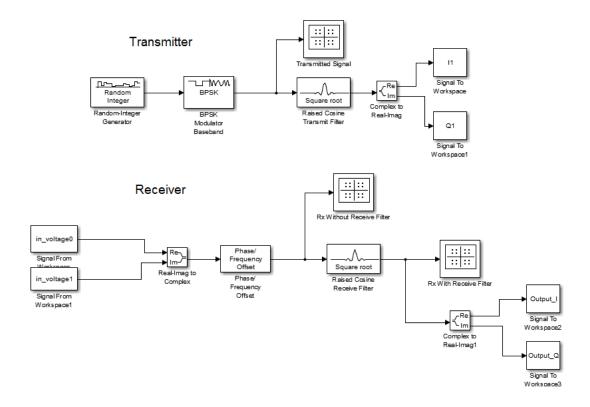

| 6.11 | Pre-processing required for experiment. At the top we have the       |

|------|----------------------------------------------------------------------|

|      | pre-processing that occurs in the transmission. At the bottom we     |

|      | have the pre-processing in the reception                             |

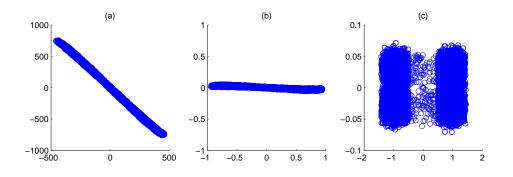

| 6.12 | The received BPSK symbols. In (a) the received constellation col-    |

|      | lected from the ADC's buffer. In (b) we have the constellation after |

|      | the phase compesantion and in (c) after the square root raised co-   |

|      | sine filter                                                          |

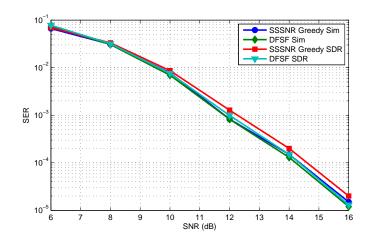

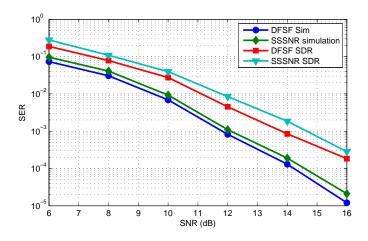

| 6.13 | Symbol error rates for multipath channel                             |

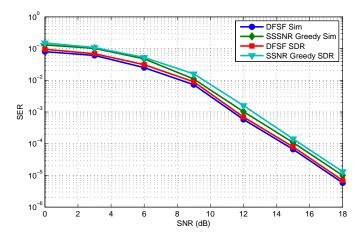

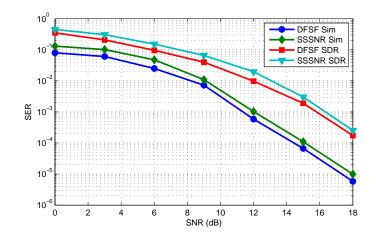

| 6.14 | Symbol error rates for vehicular channel                             |

## LIST OF TABLES

| 2.1 | Summary of optimal algorithms for ISI compensation.                          | 17  |

|-----|------------------------------------------------------------------------------|-----|

| 2.2 | Summary of sub-optimal algorithms for single carrier ISI compen-             |     |

|     | sation                                                                       | 21  |

| 2.3 | Summary of SDR platforms.                                                    | 32  |

| 2.4 | Sampling Capabilities of different SDR platforms                             | 38  |

| 3.1 | Computational Complexity, Taps Selected, and SSSNR Achieved                  |     |

|     | at 8 dB SNR                                                                  | 62  |

| 5.1 | Listing of the FMCOMMS1 module hardware components present                   |     |

|     | in both transmit and receive paths, with respective specifications.          |     |

|     | We show the part numbers for each component and the descriptions             |     |

|     | and specifications. Source: [4]                                              | 84  |

| 5.2 | Listing of the FMCOMMS2 key features [5]                                     | 86  |

| 5.3 | Percentage of samples lost during the transmission of $10^7 \ \rm samples$ . | 105 |

# LIST OF ABBREVIATIONS

| Abbreviation          | Meaning                                    |

|-----------------------|--------------------------------------------|

| ADC                   | analog to digital converter                |

| AWGB                  | additive white Gaussian noise              |

| BER                   | bit-error rate                             |

| BP                    | belief propagation                         |

| BPSK                  | binary phase-shift keying                  |

| $\operatorname{CSF}$  | channel sparsening filter                  |

| DAC                   | digital to analog converter                |

| DBPSK                 | differential BPSK                          |

| DFE                   | decision-feedback equalization             |

| DFSF                  | decision-feedback sparsening filter        |

| DMA                   | digital memory access                      |

| DSP                   | digital signal processor                   |

| FPGA                  | field-programmable gate array              |

| $\operatorname{FB}$   | feedback                                   |

| $\operatorname{FF}$   | feedforward                                |

| FMCOMMS               | RF front-end developed by Analog Devices   |

| $\operatorname{FIR}$  | finite impulse response                    |

| IIO                   | industrial input/output                    |

| IIR                   | infinite impulse filter                    |

| ISI                   | intersymbol interference                   |

| LMMSE                 | linear minimum mean squared error          |

| LMS                   | least mean square                          |

| LTE                   | linear transversal equalizer               |

| MAP                   | maximum a posteriori                       |

| MLSE                  | maximum-likelihood sequential estimation   |

| MMSE                  | minimum mean square error                  |

| MSE                   | mean square error                          |

| OFDM                  | orthogonal frequency-division multiplexing |

| $\operatorname{RFFE}$ | RF front end                               |

| $\operatorname{RLS}$  | recursive least-squares                    |

| SER                   | symbol error rates                         |

| SISO                  | soft-input soft-output                     |

| SDR                   | software defined radio                     |

| SSSNR                 | sparse shortening SNR                      |

| SNR                   | signal-to-noise ratio                      |

| TIR                   | target input response                      |

| USRP                  | Universal Software Radio Peripheral        |

|                       |                                            |

# LIST OF SYMBOLS

| Symbol                 | Meaning                                       |

|------------------------|-----------------------------------------------|

| *                      | convolution operation                         |

| $0_{m	imes n}$         | $m \times n$ matrix of all 0's                |

| $1_{m \times n}$       | $m \times n$ matrix of all 1's                |

| $oldsymbol{I}_n$       | $n \times n$ identity matrix                  |

| $ \cdot ^2$            | absolute value squared                        |

| $(\cdot)^{	op}$        | matrix transpose                              |

| $(\cdot)^H$            | matrix conjugate transpose                    |

| $[oldsymbol{S}]_i$     | <i>i</i> th column of matrix $\boldsymbol{S}$ |

| $[oldsymbol{S}]_{i,j}$ | $i, j$ th entry of matrix $\boldsymbol{S}$    |

| $  m{x}  _p$           | $\ell_p \text{ norm}$                         |

| $E[\cdot]$             | Expectation                                   |

# Chapter 1

# Introduction

The pursuit of instantaneous unlimited access to information has fueled research into designing communication systems capable of achieving high data rate transmissions, great mobility and good spectral efficiency. At present, the advancement of wireless networks is partly focused on increasing data rates in order to guarantee the required quality of service (QoS) for activities such as real-time video streaming and online gaming [6,7]. The challenge of transmitting reliable and high-rate data over a wireless channel is significant, since a practical communication system has to compensate for phenomena that may prevent the correct detection of transmitted information [8,9].

A significant amount of wireless communications research is focused on the development of optimal algorithms for mitigating phenomena that hinder wireless communications. However, many of these algorithms rely on theoretical assumptions concerning the properties of the transmitted data or implementations that do not necessarily translate to a real-world system. It is therefore of great importance to be able to combine theoretical development with practical experimentation. The ability to design and test novel theoretical schemes using practical hardware facilitates wireless communications research. Thus, the development of test platforms is important for the study of theoretical schemes applied to wireless communications systems.

#### 1.1 Motivation

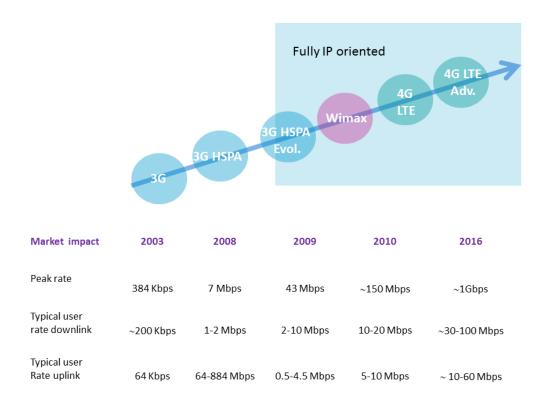

The evolution of mobile communications shows the increasing importance of data transmission in the requirements of the services provided to the users. Figure 1 illustrates achievable data rates provided by recent cellular technologies as well as the increasing data rates requirements. According to Qualcomm [10], in 2017 two-thirds of mobile traffic is going to be related to video content. This will require higher data rates in order to satisfy the quality of service requirements for such applications.

Figure 1.1: The evolution of data requirements in cellular networks. Adapted from [1]

As already mentioned, transmitting wireless information reliably is challeng-

ing due to the phenomena that interfere with the transmission and hinder correct reception. The phenomena that prevent the correct detection of transmitted information are refereed to as impairments. Three major types impairments are path loss, shadowing and inter-symbol interference (ISI) [8]. Path loss occurs due to the dissipation of a portion of the power of the signal when it is traveling through space, while shadowing is a form of power attenuation that occurs from objects that block the signal between the transmitter and the receiver. These two problems can be mitigated using power control [8] and intelligent cell-planning [11]. ISI is a phenomenon in which one symbol interferes with subsequent symbols, making the receiver unable to identify which symbol was transmitted. However, ISI is an intricate problem to solve and a large body of research has investigated different methods to overcome this impairment. Moreover, solving the ISI problem is of great importance to enable the higher data rates required by modern mobile communications.

The ISI phenomenon constitutes a significant challenge for wireless systems that aim at exchanging information at very high data rates. It is usually caused by multipath fading or the transmission of a signal through bandlimited channels. Multipath fading is caused by the multiple reflections that may occur in the signal path between the transmitter and receiver [8]. Bandlimited channels have a variable frequency profile which may distort the transmission of information and prevent the receiver of recognizing what was transmitted.

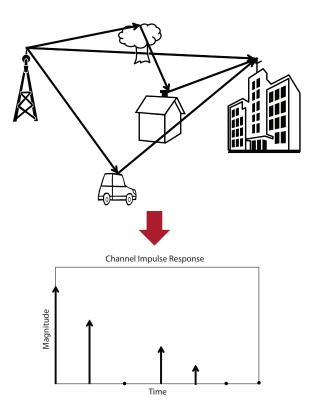

As shown in Figure 1.2, trees, buildings, and the ground can serve as reflectors. The reflected components superpose constructively and destructively at the receiver will yield a collection of copies of the signal arriving with different strengths and at different time instants. As the objects between the transmitter and receiver may also change location, the profile of signal copies can change with time. Additionally, due to different propagation times, the differences in arrival time of the responses from the longest and shortest path (related to as delay spread [12]), may take over multiple symbol durations. When the delay spread of the wireless channel is longer than the duration of the symbol being transmitted, the signal suffers from inter-symbol interference. This impairment is considerable in systems with a very high data rate, where as the rate of transmission increases, the time duration of the symbol decreases and the ISI phenomenon becomes more severe. Consequently, the frequency response of a channel with ISI present within the signal passband varies significantly. In this situation, the received signal suffers from frequency selective fading, and the wireless channel can be modeled as a finite impulse response (FIR) filter in discrete time, in which each coefficient is modeled as a random variable [12].

To transmit over a bandlimited channel, it is necessary to shape the digital signal with an analog pulse using a bandwidth that is limited to that of the channel in order to not loose frequency components that are cutoff by the channel. This process is referred to as pulse shaping [13]. If the analog pulse width is larger than the symbol period, the adjacent symbols might overlap causing the ISI effect. To mitigate the ISI phenomenon on bandlimited channels, pulse shaping must be implemented with Nyquist pulses [12] that contain only values from the desired input symbol at the sampling instants, and no interference from other symbols.

The issue of compensating for ISI has been studied extensively over the past five decades, and a wide range of strategies are available for use by communication

Figure 1.2: Intersymbol interference phenomenon forming the channel delay profile

system designers [14]. The seminal paper that discusses the signaling of transmissions over bandlimited channels was written by Nyquist [15]. Other papers discussed the mitigation of ISI, using pulse shaping [16] and joint transmitter and receiver designs for pulse amplitude modulation [17, 18]. For multipath channels, linear equalizers were proposed in [19,20] and [21] to combat the resulting ISI, and a decision-feedback structure was proposed in [22]. Even though these techniques are not computationally complex, the achieved ISI compensation is sub-optimal and limited.

Finally, the maximum a posteriori (MAP) [23] and maximum-likelihood (ML) sequence estimator [24] can be employed to mitigate ISI with optimal performance. However, one problem with these optimal approaches lies in their complexity: they are exponentially complex in the number of channel coefficients and thus cannot be used to combat ISI in channels with a long delay spread, *i.e.* a large number of channel coefficients. Examples of environments that produce channels with long delay spread include underwater acoustic communication and terrestrial communication over hilly terrain.

#### **1.2** Problem Statement

In 2005, a MAP detector employing Belief-Propagation (BP) was proposed in [25] for ISI compensation in sparse channels, which are mainly characterized as having only a small fraction of nonzero coefficients. The proposed scheme is attractive because it permits near-optimal performance with complexity that depends only on the number of nonzero coefficients. A hybrid version of this detector was proposed in [26], and it uses a linear pre-filter in the receiver just before the BP-based MAP detector. In this thesis, the prefilter that precedes the BP detector is referred to as a sparsening filter. Furthermore, in [27] a low-complexity high-throughput architecture of this hybrid structure was presented using a digital signal processor (DSP) and a field-programmable gate array (FPGA).

The idea presented in [26] is very interesting, since by designing the prefilter such that the combined response of the sparse channel and prefilter has a reduced, limited number of nonzero coefficients, the complexity of the receiver can be controlled. However, in this work relatively little attention is paid to the interaction of the sparsening filter and the BP-based detector and only a simplistic method for designing the sparsening filter is provided. For example, the sparsening filter is arbitrarily designed such that the channel coefficients, or taps, of the combined response of the sparse channel and sparsening filter coincide with the dominant taps in the original channel. Also, most analyzes performed for BP-based structures has been provided in light of numerical simulations and only a few hardware implementations have been attempted [27, 28].

Given the level of reconfigurability required by the prefilter design, coupled with the inherent complexity of the belief propagation algorithms, a software-defined radio (SDR) solution presents itself as a reasonable candidate for rapid testing and prototyping. Several software defined radio (SDR) architectures have been developed and are commercially available in order to enhance the prototyping phase of new wireless technologies as well as advance the current state-of-the-art in wireless and networking communications systems. While there exists several well-known SDR platforms that are commercially available [2, 29–34], many of these systems are designed primarily for conducting fundamental research and experimentation, and not for development of actual commercial products and prototypes. In this sense, the existence of SDR prototyping platforms and their accompanying software interfaces is the key for enabling continued advances in the wireless sector. In addition, it is of utmost importance better understand both the capabilities and limitations of SDR technology when used in real-life communications systems.

#### **1.3** Proposed Solutions

In this thesis, we propose several novel design approaches for implementing belief propagation (BP)-based detectors. The main idea is to design a prefilter so that the combined response of the sparse channel and prefilter has a reduced, limited number of nonzero coefficients, thus controlling the complexity of the receiver. In this work, the prefilter that precedes the BP detector has been termed a sparsening filter. We present two different techniques for the design of sparsening filters. The first one relies on a linear structure for the sparsening filter and uses a new metric also proposed in this work to design it. The second technique proposes a decision feedback structure as a sparsening filter.

Once these theoretical designs and numerical simulations have been explored, the next step is to conduct hardware experiments in a real-world environment. Thus, one of the contributions of this work includes the development of a custombuilt interface framework for a software defined radio platform that aims to provide a design and testing environment for complex communication transceivers capable of prototyping receivers such as the hybrid structure with a sparsening filter and BP detector.

### 1.4 Contributions

The main contributions of this dissertation are as follows.

• Linear Sparsening Filter Design:

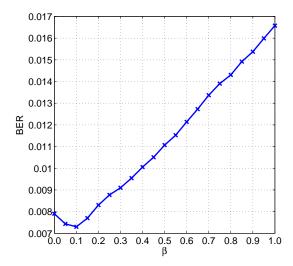

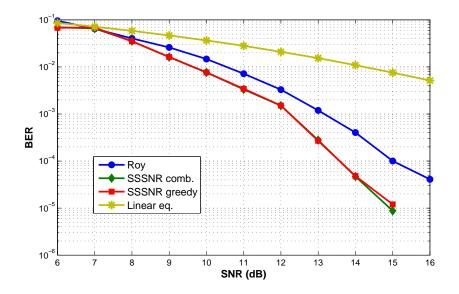

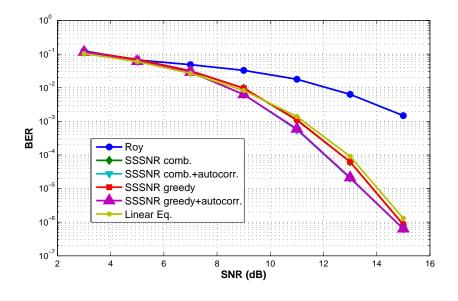

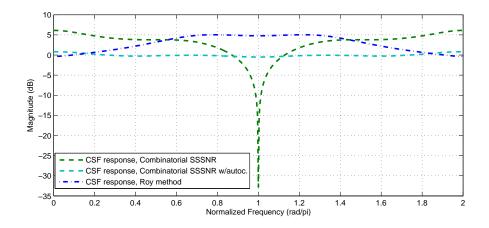

We propose a filter design metric called the Sparse Shortening SNR, and showed that maximizing this quantity serves as a good proxy for minimizing BER. We also develop a greedy algorithm for tap selection, which provides near-optimal performance with reduced complexity. Finally, we take into consideration the issue of noise coloration introduced by the sparsening filter to design the desired prefilter.

• Decision-Feedback Sparsening Filter Design:

We propose a filter design metric based on classical DFE design, which improved in both performance and complexity when compared with the Linear Sparsening Filter Design. Once again the interaction of the sparsening filter and BP detector is considered in the filter design generating better error performance.

• Interface Architecture for Software Defined Radio Systems:

We present an interface architecture that enables software connectivity and support for the FMCOMMS boards, a family of RF front-ends developed by Analog Devices (ADI), and GNU Radio, a software environment for the design systems that involve digital signal processing. We also provide experiments using GNU Radio Companion and the FMCOMMS hardware platform that attest the correct functionality of the proposed interface. Finally, we characterize the proposed interface in terms of supported sampling frequency and data throughput.

• Sparsening Filter experimentation in a SDR platform:

We provide different experimentation environments and results for the implementation of the designed BP-based receptors in the FMCOMMS SDR platform.

#### **1.5** Dissertation Organization

This dissertation is organized as follows.

Chapter 2 presents a literature survey and tutorial of several topics covered in this dissertation with the purpose of contextualize the subsequent Chapters and their focus of discussion. The chapters explains the different types of impairments that hinder wireless communications transmissions, with focus on inter-symbol interference (ISI). It also discuss several ISI mitigation schemes already existent in the literature. Finally, a tutorial on software defined radio is provided contextualizing the usage of the technology over the years and its importance on experiments design and prototyping.

Chapter 3 focuses on the design of linear *sparsening* prefilters for use with softinput soft-output MAP detectors of the form considered in [25, 26]. While [25, 26] primarily focused on the case where the original channel is sparse, it is noted that even nonsparse channels can be sparsened with a simple linear, finite impulse response (FIR) filter. Consequently, this work can be applied in general situations, even where the original channel is not sparse. The issue of sparsening filter design is addressed with the goal of minimizing a metric designed to be a proxy for the detector bit error rate BER. The interaction of the sparsening filter and BP detector has been considered to develop a practically-implementable sparsening filter design method.

Chapter 4 focuses on the design of decision feedback *sparsening* filters for use with soft-input soft-output MAP detectors of the form considered in [25, 26]. In particular, the hybrid structure proposed by [26] is extended so that the linear sparsening filter which performs partial equalization is replaced by a non-linear decision feedback sparsening filter.

Chapter 5 details the development of an interface framework between an radio platform and the GNU Radio SDR development environment in order to enable software support for the FMCOMMS family of RF front ends. This work expands the initial prototype interface framework started at ADI by enhancing the functionality of the work in order to facilitate seamless connection between a FM-COMMS SDR platform and GNU Radio. In addition to discussing the hardware platform and the proposed software interface framework, we provide experiments that attest the correct functionality of the SDR platform and that test the interface performance limits.

Finally, Chapter 6 includes the description of the experiments using the FM-COMMS SDR platforms on the implementation of the proposed linear and decisionfeedback sparsening filters, presented in Chapters 3 and 4.

In Chapter 7, the research achievements of this work are summarized and topics for future work are presented.

# Chapter 2

# Inter-Symbol Interference Mitigation and Software Defined Radio Technology

In this chapter, we present a literature survey and tutorial of several topics covered in this dissertation. In the first section, we discuss the wireless transmissions impairments and the different techniques used in the literature for inter-symbol interference (ISI) compensation; these concepts are important and aid in the better understanding of Chapters 3 and 4 of this thesis. In addition, we provide a tutorial on software defined radio technology to complement the Chapters on software interface implementation and experimentation.

#### 2.1 Wireless Transmission: Impairments and Mitigation

As already mentioned in Section 1.1, transmitting reliable and high-rate data over a wireless channel is challenging due to physical phenomena that make the reception and recognition of the transmitted information a difficult task. In this sense, one of the chief impairments faced by modern, high data-rate communication receivers is called inter-symbol interference (ISI) [11].

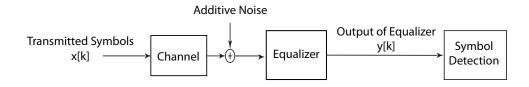

In order to be able to correctly detect the symbols that were transmitted, it is necessary to compensate for the ISI introduced by the channel. The role of equalization in a digital transmission is to mitigate the inter-symbol interference phenomenon by attempting to undo the scattering provided by the wireless channel

Figure 2.1: High level digital transmission schematic with the equalizer filter.

to the received symbols [35]. By doing so, the recovery of transmitted symbols becomes feasible and the receiver is able to detected and recognized the symbols correctly. Figure 2.1 shows a high-level digital transmission schematic with the equalizer filter.

The issue of compensating for ISI has been studied at length over the past five decades, and a wide range of strategies are available for use by communication system designers. In the following, we present several techniques for ISI compensation and discuss their properties.

## 2.1.1 Optimal ISI Mitigation

Given that the ISI channel can be modeled as a FIR filter, it can also be modeled as a finite-state machine, which can be represented by a trellis structure. In this case, the sequence of symbols can be represented by a path through the trellis and the problem of correctly deciding the symbol that was transmitted reduces to the finding the correct path in this trellis. Maximum a posteriori (MAP) or maximumlikelihood (ML) sequence estimators are algorithms that provide optimal detection performance and are discussed next.

The maximum likelihood sequence estimation (MLSE) algorithm finds the most

likely sequence corresponding to the received symbols [12]. In other words, the algorithm searches through the trellis that is equivalent to the ISI channel and finds the most probable path though the trellis. To calculate the likelihood of a determined path, the MLSE calculates the distance between the sequences; if the demodulator performs hard decisions, the Hamming distance metric is used, but if the demodulator performs soft decisions, the Euclidean distance metric is implemented.

The Viterbi algorithm [36] was developed by Andrew J. Viterbi and was originally designed to decode information coded using convolutional codes, but it was Forney [37] and Omura [38] that proposed the use of the Viterbi algorithm as the optimal maximum-likelihood sequence estimator for ISI mitigation. The Viterbi algorithm is a sequential trellis algorithm that reduces the number of sequences tested in the trellis, by eliminating sequences at each stage of the trellis. For example, if the ISI channel has a length of L + 1 symbols and the information symbols are M-ary, the channel is described by an  $M^L$ -state trellis. We begin with L samples, and compute  $M^{L+1}$  metrics and  $M^{L+1}$  which are divided in  $M^L$  groups. In each group, one sequence is selected (the sequence with the largest probability) and M - 1 are discarded, generating  $M^L$  surviving sequences and their metrics. As it can be noticed, the number of computations required by each stage of the algorithm grows exponentially with the length of the ISI channel L, limiting the usage of the Viterbi algorithm for small L.

The BCJR algorithm [39], named after its inventors (Bahl, Cocke, Jelinek, and Raviv), was also originally developed for convolutional codes. It uses a symbol-bysymbol maximum *a posteriori* (MAP) decoding algorithm to decode each input symbol instead of searching for the most likely sequence as the MLSE estimators. In this sense, the BCJR finds the most likely individual bits or symbols in addition to values for the *a posteriori* probability P(x|y), where *x* is the desired bit or symbol and *y* is the received sequence. This probability determines the level of certainty regarding the estimation of the bit or symbol *x* and are called soft outputs; for this reason, the BCJR is also called a *soft-input soft-output* (SISO) decoder. As the Viterbi decoder, the BCJR algorithm's complexity also increases exponentially with the length of the ISI channel [12].

#### **Belief Propagation Detector**

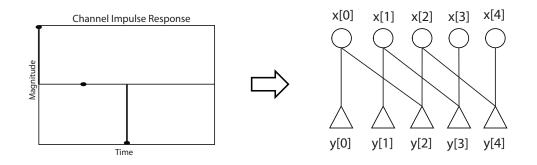

The belief propagation (BP) algorithm is also in the class of message passing algorithms, and is sometimes called the *sum-product algorithm* [25]. It can be used as the Viterbi and BCJR algorithm as symbol detector, compensating for ISI and allowing for correct reception of transmitted information. By representing the ISI channel as a factor graph, we can use the BP algorithm to implement MAP detection by estimating the sequence of symbols that maximizes the joint a posteriori probability mass function. In Figure 2.2, we have an example in which the channel  $h = \begin{bmatrix} 1 & 0 & -1 \end{bmatrix}$  is represented as a factor graph. The graph consists of bit nodes, which represent the channel inputs (x[.]), and check nodes that represent the channel outputs (y[.]). In this example, the output symbols can be written as:

$$y[0] = -1 * x[0] = -x[0]$$

$$y[1] = -1 * x[1] + 0 * x[0] = -x[1]$$

$$y[2] = 1 * x[2] + 0 * x[1] + -1 * x[0] = x[2] - x[0]$$

(2.1)

$$y[3] = 1 * x[3] + 0 * x[2] + -1 * x[1] = x[3] - x[1]$$

$$y[4] = 1 * x[4] + 0 * x[3] + -1 * x[2] = x[4] - x[2].$$

Note that in the graph, the connections between the channel input symbols and the channel output symbols represent the dependencies between the received and transmitted symbols (the negative signs are not represented in the factor graph). For example, check node y[0] is only connected to bit node x[0], since y[0] = -x[0], check node y[1] is connected to bit node x[1], since y[1] = -x[1], check node y[2]is connected to bit nodes x[2] and x[0], since y[2] = x[2] - x[0] and so fourth.

The BP algorithm proceeds iteratively, exchanging information between check nodes and bit nodes [26]. As already mentioned, the algorithm is in the class of message passing algorithm because the probabilist information about the received symbols is passed from check nodes to bit nodes. In this process, log likelihood ratios of the transmitted bits are computed and become more reliable with each iteration. After a sufficient number of iterations, the log likelihood ratios can be used to make bit decisions. In the case of the BP detector, the order in which these message are passed occur according the flooding schedule [25], where nodes pass the information to their neighbors subsequently.

If the BP algorithm proceeds over N total iterations, the total complexity requires on the order of  $N(\mu + 1)M^{\mu+1}$  summations, where M is the size of the source alphabet and  $\mu$  is the number of significant effective channel taps used in the detection. As such, the complexity of the BP is exponential in  $\mu$ , and so the system designer can specify the total complexity by appropriate choice of  $\mu$ . This interesting property is the main reason for this thesis to focus specifically on using the BP algorithm as symbol detector for ISI compensation. Table 2.2 provides a

Figure 2.2: The  $h = \begin{bmatrix} 1 & 0 & -1 \end{bmatrix}$  channel represented as a factor graph. The graph is formed by bit nodes, which are the channel inputs (x[.]) and the check nodes, which are the channel outputs (y[.]). The connections between bit nodes and check nodes represent the dependencies between the received and transmitted symbols.

summary of the presented optimal approaches for ISI compensation.

| Algorithm | Principle | Complexity                           |

|-----------|-----------|--------------------------------------|

| Viterbi   | MLSE      | Exponential on the delay spread      |

| BCJR      | MAP       | Exponential on the delay spread      |

| BP        | MAP       | Exponential on $\#$ of non-zero taps |

Table 2.1: Summary of optimal algorithms for ISI compensation.

#### 2.1.2 Sub-Optimal ISI mitigation

As the MLSE and MAP detectors have computational complexities grows exponentially with the length of the channel time dispersion, their usage with most real-world channels is very limited. Even for the BP detector, which has the advantage of the complexity growing only on the number of non-zero channel coefficients, the computational complexity can be prohibitively costly. For these reasons, suboptimum channel equalization approaches were made necessary to mitigate ISI.

Linear Equalizers, are filters designed with a linear structure. In terms of structure, the linear transversal equalizer (LTE) is formed by tapped delay lines and it can be implemented as a finite impulse response (FIR) filter or as an infinite response (IIR) filter [40], which are the most used structures for linear equalizers. Other possible linear structures are the linear transversal equalizer [41] and the lattice equalizer [42]; these structures have good numerical stability, but also have too complicated structures. In terms of the filter's coefficients, there are different ways of choosing their values, such as the peak distortion criterion and the mean square error criterion [12].

The peak distortion criterion [19,20] seeks the minimization of the worst-case inter-symbol interference effect on the received symbols. This goal is achieved when the equalizer's transfer function is the inverse of the channel's model; the ISI mitigation happens because the filter completely eliminates the effect of the channel on the symbols. This filter is called zero-forcing filter. In other words, if we have a channel with transfer function H(z), the corresponding zero-forcing filter is  $\frac{1}{H(z)}$ , which eliminates the channel's filtering effects leaving only a multiplying constant gain. Although simple to calculate, the zero-forcing presents 2 important issues. The first one is that the inverse of a channel modeled as a FIR filter is an IIR filter, which is not practical to build. The second is that it can potentially enhance the additive noise; if the channel contains a null in its frequency response, the zero-forcing equalizer produces a spike to compensate for the null and will end up amplifying the noise which is also filtered.

For the mean square error (MSE) criterion [21], the filter is designed to minimize

the mean square value of the error signal, which is the signal at the output of the filter minus the transmitted signal. The calculation of the filter coefficients then becomes an optimization problem in which the cost function is [12]:

$$J = E[(y[k] - x[k])^2],$$

(2.2)

where y[k] is the filter output and x[k] are the transmitted symbols. After solving this optimization problem, the minimum of the cost function has the following transfer function:

$$\frac{1}{H(z) + N_0},$$

(2.3)

which is very similar to the zero-forcing expression, with exception of the noise spectral density  $N_0$ . In this sense, the equalizer coefficients are adjusted to minimize both the MSE due to the ISI and the noise power at the filter's output. However, the minimum mean square error equalizer (MMSE) still has the same problem as the zero-forcing regarding the infinite length required for optimal cancellation, which can not be implemented in practice but only approximated by FIR filters.

Other than linear equalization, there are several non-linear structures that are also used in the design of equalizers. The decision-feedback equalizer [22] is one of such filters. This type of equalizer is usually formed by two components: the feedforward and the feedback filters as showed in Figure 2.3. The received symbols are inputed to the feedforward filter and its output is summed to the output of the feedback filter in order for the decision device to provide hard decisions on the symbols. These decisions are delayed and then inputed to the feedback filter; the feedback filter removes part of the ISI on the current symbol using the decisions on previous numbers.

Figure 2.3: Decision-feedback equalizer structure with feedforward and feedback filters and decision device.

In comparison, DFE are able of performing ISI compensation with reduced noise enhancement and may thus provide significantly lower symbol error rates (SER) than a linear equalizer. On the other hand, due to the nonlinear feedback structure of DFE's, symbol errors induced by high noise may cause instability due to the feedback of wrong decisions. This phenomenon called error propagation, although of small probability, may also lead to poor error performance.

The equalizers mentioned so far all have a static structure, which are preset to mitigate channels that are invariant in time. Another category of equalizers are the adaptive equalizers, in which the filter coefficients are updated while the data is being processed [43]. In other words, the coefficients are automatically adapted using a pre-determined optimization metric and known transmitted symbols (for training), to be adjusted to the channel and even adapted to it if the channel is time-varying. There are several well-known algorithms for adaptive equalization, such as the least-mean-square (LMS) [44], the adaptive decision-feedback equalizer [45], the recursive least-squares (RLS) [46] and the Kalman filter [47]. In addition to traditional adaptive filtering, another technique of adaptive equalization was also extensively studied in the literature, the blind equalization. In these algorithms, the transmitted signal is equalized using only signal statistics, and no training symbols. Among many blind equalization algorithms, the most well known is the constant-modulus algorithm (CMA) [48].

Table 2.2: Summary of sub-optimal algorithms for single carrier ISI compensation.

| Equalizer           | Principal Characteristics                                  |

|---------------------|------------------------------------------------------------|

| Linear              | Simple, has problems with noise enhancement                |

| DFE                 | Better performance than linear, error propagation problems |

| LMS, RLS and Kalman | Linear adaptive filtering                                  |

| CMA                 | Blind equalization                                         |

## 2.1.3 Multicarrier Modulation

All the methods presented so far are associated with a single carrier modulation scheme. This means that the information is transmitted using a single slot of frequency; all the information is contained in a specific frequency range. However, with single carriers, higher data rate requirements end-up resulting in problems with ISI. Higher data rates require smaller symbol periods, which in turn result in ISI if the symbol period is smaller than the channel's delay spread ( see Section 1.1). Another way to deal with the ISI problem is to use a multicarrier modulation data transmission scheme [49].

The idea behind multicarrier modulation is to subdivide the available channel in many subchannels so the frequency response in each one of these subchannels is approximately constant [12]. This facilitates the equalization process and provides a solution to the ISI problem for high data rated systems. The multiple carriers allow the symbol period to be larger than the channel's delay spread, still maintaining higher effective rates distributed over non-overlapping frequency bands. Figure 2.4 shows a multicarrier communication system. In the transmitter, the symbols are parallelized and then modulated; after the multicarrier modulation, the information is converted to a serial sequence to be transmitted over-the air. In the receiver, the received symbols are parallelized to pass through demodulation and detection.

Figure 2.4: Block diagram representing a multicarrier transmission system. For the transmission, the information is first parallelized to be modulated and in the receiver, the information is also parallelized to be demodulated and detected.

The orthogonal frequency-division multiplexed (OFDM) scheme [50, 51] is a special type of multicarrier modulation in which the subcarriers are orthogonal to each other. In other words, the information is transmitted using multiple subcarriers in different frequencies; the frequency spacing of the carriers is chosen so the modulated carriers become orthogonal and therefore do not interfere with each other. Figure 2.5 shows the orthogonal subcarriers. Most modern communications systems use the OFDM scheme for digital transmission: the wireless LAN (WLAN) radio interfaces, digital radio systems, the terrestrial digital TV systems DVB-T and ISDB-T, ultra-wideband (UWB) and others. Moreover, the OFDMA [52], a OFDM-based multiple access technology was also used in several cellular networks, specially in the downlink operation.

Figure 2.5: Orthogonal subcarriers in a OFDM scheme. The subcarriers are separated by a  $\Delta f$  frequency spacing.

One of the greatest disadvantages of the OFDM scheme is the fact that it suffers from a high peak-to-average-power-ratio (PAPR), which requires linear circuitry in the transmitter. The problem with this type of circuit is that it is not power efficient and it makes the power manager in small devices, such as mobile handsets, very difficult. For this reason, the uplink operation of cellular communication is implemented in a single carrier scheme; more specifically, the single-carrier frequency division multiplex access (SC-FDMA) scheme [53]. It was adopted in the uplink operation in the 3GPP Long Term Evolution (LTE) and 4G. In this work, we focus on single-carrier schemes to combat the ISI impairment.

## 2.2 Software Defined Radio Technology

Advances and innovation within the wireless sector have always been closely coupled to corresponding improvements in digital technology, including computing devices. Until the 1950s [54–56], wireless systems were exclusively operating in the analog domain, where various communications functions such as modulation and filtering were performed using analog circuits and components. As a result, the process of designing a robust communication system was time-consuming and costly since analog circuit designers were needed to devise systems that met specifications and were difficult to mass produce at a scale that could enable wide-spread penetration within a large consumer market. With the rapid evolution of digital technology, especially analog-to-digital and digital-to-analog converters (ADCs and DACs), it now became possible to perform these same baseband communication functions partially or entirely within the digital domain, greatly reducing cost, enabling mass production of these transceivers, and providing a greater a flexibility and system functionality. Consequently, when communication systems transcended the analog/digital divide, this became a defining moment of the Information Age and the enabler of ubiquitous wireless data access that todays society has grown accustomed to over the years.

The first wireless devices that employed digital technology were based on nonprogrammable, static designs realized using application-specific integrated circuits (ASICs). These implementations enabled wireless devices, such as cellular telephones and wireless local area networking modems, to eventually be produced on a large, commercial scale at a cost that would make these systems reasonably affordable in a consumer market. As various computing technologies began to mature, such as digital signal processors (DSPs), they also began being incorporated into the baseband digital implementation of these wireless systems. However, these computing devices were programmed with a static set of operations to be performed by the wireless system, such as filtering, data compression, modulation, and other baseband operations.

Lately, the widely spread use of wireless mobile devices has presented great potential challenges in the area of wireless services provision as different standards can be used on the same device depending on the circumstances of use. Each of these radio standards require their own specific access terminal and base station infrastructure creating the need for installing and maintaining a plethora of specific equipments. The use configurable radio technologies the rises as a possibility, requiring an evolution from static programmed operations. This new concept permits providing an infrastructure from which service providers can evolve to meet the needs of the users without heavy re-investment in infrastructure.

As mentioned, the evolving wireless networks requirements in reconfigurable technology led in the past few years to the diffusion of the so-called Software Defined Radio (SDR) architectures. To conduct research in this area, it is necessary to possess sufficient knowledge in both hardware platforms and software environments. The background needed includes the different SDR platforms as well as some information on software development environments.

### 2.2.1 A Brief History

The term software radio was introduced by Joseph Mitola in 1992 [57]. However, a SDR prototype had already been presented in 1988 by Hoeher and Lang [58]. The establishment of SDR as a technology came with the first publicly funded SDR development initiative, called SpeakEasy I/II by the U.S. military [59]. The first generation of the SpeakEasy system initially used a Texas Instruments TMS320C40 processor (40 MHz), while the SpeakEasy II platform was the first SDR platform to involve field programmable gate array (FPGA). Later, the U.S. Navy developed the digital modulator radio (DMR), a platform with many waveforms and modes that could be remotely controlled with an Ethernet interface.

As Figure 2.6 shows the timeline of the evolution of both processing technology and SDR technology, it is possible to notice the necessity of developing components with higher computational power and flexibility to enable better SDR platforms. It was only after the year 2000, with powerful FPGAs and DSPs, that most of the existing platforms were developed. More recently, the ARM Cortex A9 opened the possibility of accessible on-board processing, discarding the necessity of a host computer for system development.

In the late 1990s SDR started to spread from the military domain to the commercial sector, with cellular networks being considered the natural area of application [60]. Several Companies such as Vanu [61], Airspan [62] and Etherstack [63] started to develop SDR products for cellular base stations. In 2005, Vanu released in 2005 the first SDR product approved by the software radio regulation: the Anywave<sup>TM</sup> GSM base station. The BTS (base transceiver station), the BSC

Figure 2.6: Processing technology vs. SDR technology. The timeline of the past decades shows how the evolution of different types of processors had a great impact in the development of SDR platforms.

(base station controller), and TRAU (transcoder and rate adaptation unit) modules of the BSS (base station subsystem) were implemented in software in the Anywave base station. Although this successful implementation brought substantial attention to SDR technology and it was thought at the time that SDR base stations would be key for 3G networks, the reality regarding the commercial usage of SDR technology was still somewhat distant.

One of the most commonly used SDR hardware platform is the Universal Software Radio Peripheral (USRP) [29]. Developed by Ettus Research LLC, the USRP is a device that turns general purpose computers into flexible SDR platforms. The core of the USRP is a motherboard with four high-speed ADCs and DACs and a FPGA. The ADCs/DACs are connected to the radio Front-Ends (called daughterboards), while the FPGA is connected to a general purpose computer. In the Universal Software Radio Peripheral - Version 1 (USRP1) this connection is performed by a USB port, while the USRP2 (showed in Figure 2.7) includes a Gigabit ethernet interface. The main principle behind the USRP is that the digital radio tasks are divided between the internal FPGA and the external host CPU. The high speed general purpose processing, like down and up conversion, decimation, and interpolation are performed in the FPGA, while waveform-specific processing, such as modulation and demodulation, are performed at the host CPU. The USRP platform can be used with both GNU radio and MATLAB software development environments. More recently, Ettus Research released the new X Series, a platform that contains more powerful daughterboard slots, 6 GHz with up to 120 MHz of baseband bandwidth, and a large user-programmable Kintex-7 FPGA.

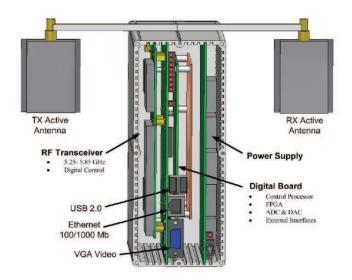

Another SDR hardware platform is the Kansas University Agile Radio (KUAR) [2], showed in Figure 2.8. The KUAR platform was designed to be a low-cost experimental platform targeted at the frequency range 5.25 to 5.85 GHz and a tunable bandwidth of 30MHz. The platform contains a Xilinx Virtex-II Pro FPGA board and a PCI Express 1.4 GHz Pentium-M microprocessor. With these features, almost all processes can be implemented in the platform, instead of the host com-

Figure 2.7: The Universal Software Radio Peripheral 2 (USRP2). The software defined radio platform developed by Ettus Research.

puter, which minimizes the host-interface requirements. In addition, the KUAR utilizes a modified form of the GNU Radio software framework to complete the hardware platform.

With respect to compact SDR platforms, the Maynooth Adaptable Radio System (MARS) [31] was designed to be connected to a personal computer which handles all of the signal processing algorithms. Another objective was to deliver a performance equivalent to a base station and the wireless communication standards in the frequency from 1700 to 2450 MHz. The software framework selected for initial development was the IRiS framework (Implementing Radio in Software).

Some other SDR platforms include:

Figure 2.8: The KUAR radio. Source: [2]

- Berkeley BEE2 [64]: has five Xilinx Virtex-II Pro FPGAs on a custom-built emulation board.

- Japanese National Institute of Information and Communications Technology (NICT) SDR Platform [65]: contains two embedded processors, four Xilinx Virtex2 FPGA, and RF modules that could support 1.9 to 2.4 and 5.0 to 5.3 GHz.

- Rice University Wireless Open Access Research Platform (WARP) [32]: radios include a Xilinx Virtex-II Pro FPGA board as well as a MAX2829 transceiver.

While these SDR platforms are mainly used for research and experimentation, the final goal of developing SDR systems capable of implementing modern communication protocols remains far for reality. The development of new hardware platforms and accompanying software interfaces is key to advances in the area and to better understand the capabilities and limitations of the SDR technology when used in real-life communications systems.

Lately, a few companies have also been developing different SDR solutions for use in academia and industry. For example, Nutaq [33] developed two main SDR products, the ZeptoSDR and the PicoSDR, both of which support RF frequencies between 300 MHz and 3.8GHz and bandwidth of 1.5 to 28 MHz. The ZeptoSDR uses a Xilinx Zynq-7 and an embedded ARM Cortex-A9, and the PicoSDR uses a Xilinx Virtex-6 and an embedded Quad-Core i7. Epiq Solutions [34] also developed two compact SDR products, the Sidekiq and the Matchstiq, as well as another platform called Maveriq.

Analog Devices Inc. (ADI) has been in the SDR market since the 1990s, and serves numerous customers in this area. Consequently, in order to obtain a better understanding of the needs of both current and prospective customers, one approach is to learn more about SDR as an application by exploring the actual application/protocol using the product, to better understand how to optimize the RF front-end and SDR components for a specific application, and to provide the customers with a real working system before they employ it themselves. For these reasons, ADI developed the FMCOMMS1 [4] and FMCOMMS2 [5] RF Front-Ends, which are going to be the focus of this thesis.

### 2.2.2 Anatomy of a Software-Defined Radio

In traditional radios, all radio functionalities are performed by specialized components that execute specific functions, such as modulators/demodulators and coding/decoding. In this case, all signal processing is performed within these spe-

| SDR Platform  | Processing Device          | Sampling and Bandwidth                          |

|---------------|----------------------------|-------------------------------------------------|

| USRP2         | Xilinx Spartan 3A-DSP 3400 | 100  MS/s ADC, $400  MS/s$ DAC                  |

| USRP X Series | Xilinx Kintex-7            | 120 MHz of bandwidth                            |

| Kuar          | Xilinx Virtex-II Pro       | bandwidth of 30MHz                              |

| MARS          | Personal Computer          | 1700 to 2450 MHz $$                             |

| BEE2          | 5 Xilinx Virtex-II Pro     | -                                               |

| NICT          | Xilinx Virtex2             | $1.9$ to $2.4$ and $5.0$ to $5.3~\mathrm{GHz}$  |

| ZeptoSDR      | Zedboard                   | 1.5 to 28 MHz                                   |

| PicoSDR       | Virtex-6                   | $3.8~\mathrm{GHz},28~\mathrm{MHz}~\mathrm{BW}$  |

| Maveriq       | Spartan 6 LX150T           | DAC and ADC 50 MHz                              |

| FMCOMMS1      | ZedBoard                   | $250~\mathrm{MSPS}$ ADC and 1 GSPS DAC          |

| FMCOMMS2      | Zedboard                   | $640~\mathrm{MSPS}$ ADC and $320~\mathrm{MSPS}$ |

Table 2.3: Summary of SDR platforms.

cialized hardware. The software-defined radio technology replaces some of the traditional radio components with components implemented in software.

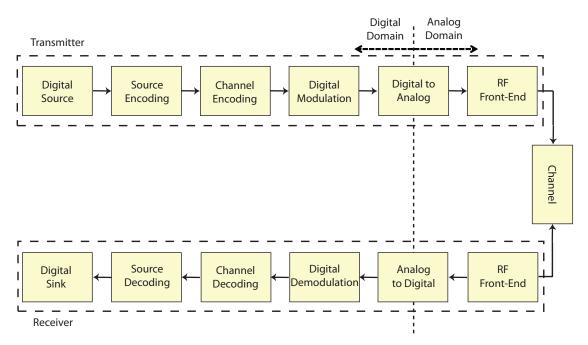

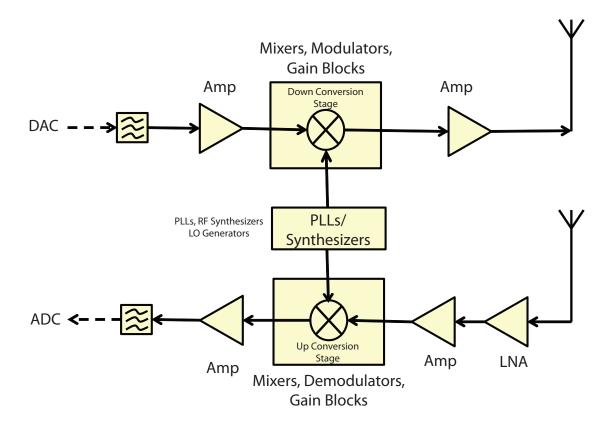

A software-defined radio transceiver is divided into two main parts: (i) an analog Front-End, which performs the narrowband frequency downconversion followed by an Analogue-to-Digital Conversion (ADC), and (ii) the digital signal processing components, which are responsible for the remaining signal processing flow [66]. Thus, operations such as (de)modulation, filtering, and channel (de)coding are performed in the digital domain. Figure 2.9 shows the typical data flow in a software-defined radio system. In this case, nearly the entire baseband signal processing on both the transmission and receiving ends is performed in the software domain.

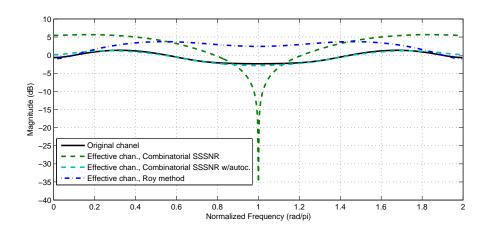

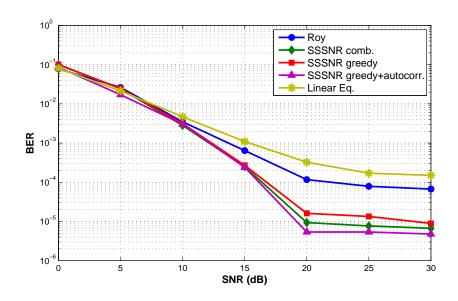

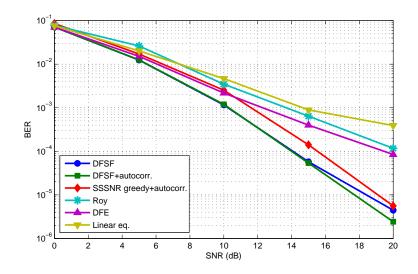

Figure 2.9: Block Diagram showing the Digital and Analog divide in a Software-Defined Radio Platform. The digital signal processing is performed in the digital domain in baseband, while the analog portion of the system performs the RF operations. Based on [3], Figure 5.