# Dynamic Partial Reconfiguration of a Field Programmable Gate Array

A Major Qualifying Project Report

Submitted to the faculty of

Worcester Polytechnic Institute

In partial fulfillment of the requirements for the

Degree of Bachelor of Science

| Submitted By:  |                             |                |                   |

|----------------|-----------------------------|----------------|-------------------|

|                | Michael Kristan             | Brian Loveland | Robert Sazanowicz |

| Sponsored by:  |                             |                |                   |

|                | General Dynamics C4 Systems |                |                   |

|                | 77 A Street                 |                |                   |

|                | Needham, MA 02494           |                |                   |

| Liaisons:      |                             |                |                   |

|                | Brendon Chetwynd            |                |                   |

|                | Orlando Gerardo             |                |                   |

| Submitted To:  |                             |                |                   |

|                | Prof. John McNeill          |                |                   |

| Co-Advised By: | Prof. Berk Sunar            |                |                   |

## **Abstract**

The goal of this project was to develop a prototype of real-time partial re-configuration of a logic circuit. The steps required for completion involved researching possible circuit algorithms, implementing desired functionality in VHDL, and developing a proof of concept. The objective of this project was to lay a foundation for further development in implementing a self-healing triple modular redundant AES encryption system. The project was completed under the guidance of Brendon Chetwynd and Gerardo Orlando of General Dynamics C4 Systems.

## **Authorship**

The completion of this Major Qualifying Project involved a significant amount of time and dedication from each respective team member. This report represents a collaboration of ideas from all members as well as an equal level of time and effort. Throughout the course of this project, several aspects of work were divided among team members. Rob Sazanowicz focused his work on PlanAhead development and the implementation of the Partial Reconfiguration over JTAG designs. Brian Loveland focused his efforts on the implementation of self-reconfiguration through use of the Embedded Development Kit and the on board PowerPC processors. Mike Kristan contributed greatly to the project management aspect as well as working on the integration of Embedded Development Kit and PlanAhead tool flows with Rob. The separation of these tasks allowed us to specialize our work to increase productivity. However, much of the project's success was dependant on peer collaboration. Each team member contributed equally to this project report in all aspects including research, practice, and writing.

## **Executive Summary**

General Dynamics C4 Systems implements several technologies in their development of hardware encryption systems as a US government contractor. One such technology involves the development of encryption systems through the use of a Field Programmable Gate Array (FPGA). First developed in 1984, FPGAs represent a growing technology of which functionality and ease of use are constantly improving. One such development involves dynamic partial reconfiguration, the ability to reprogram a portion of the FPGA without powering down or resetting the chip. This functionality is still considered to be academic in nature and has seen little professional development. This ability opens the door to new applications as well the reduction of size requirements for designs. This is concluded from the idea that larger designs can be broken into smaller, less resource intensive partial designs and then programmed to the chip only when necessary. In addition, with reconfigurable logic such as an FPGA, there is a possibility that it could inadvertently loose or change its configuration. Partial reconfiguration, tied with the necessary circuitry, would allow the FPGA to identify these issues and reconfigure itself only where the faults occur. Xilinx, the original developers of the FPGA, have pushed development of partially reconfigurable designs.

The Xilinx Virtex II Pro series FPGAs allow for support of partial reconfiguration through the use of an enhanced toolset. The primary objective of this Major Qualifying Project was a proof of concept for a partially reconfigurable design. To accomplish this, the team began development on a Memec Design XC2VP30 – FFII152 development board. The on board Virtex II Pro FPGA supports dynamic partial reconfiguration and contains an embedded IBM PowerPC processor to control self-reconfiguration. The secondary objective of this project is to implement a self-healing design through the use of one of these embedded processors. The PowerPC has the ability to control reconfiguration of the FPGA through the Internal Configuration Access Port (ICAP). Ideally, a PR design would be able to detect a need for and control partial reconfiguration creating a self-sustaining system. Eliminating the need for an external processor lowers costs and size requirements while simplifying the overall design and increasing reliability by not relying on external interconnects. The third major goal of this project is the creation of a base for future development with partial reconfiguration. One such development includes the integration of a Triple Modular Redundant (TMR) system with partially reconfigurable capabilities. TMR has been widely used to increase the reliability of FPGA circuits and is used to avoid corruption due to environment hazards and side channel attacks.

In order to complete our primary objective, the development of a proof of concept for partial reconfiguration, it was first necessary to gather the required software and hardware tools and create a design flow. A handful of third party tutorials as well as Xilinx provided documentation was used to develop a design flow which functioned properly with the toolset available to us. The partial reconfiguration design flow follows closely the

modular design flow most commonly used by industry professionals with the addition and modification of a few software tools. Once the necessary research was completed to collect and learn these tools, the team began creation of an initial PR design. This basic circuit was programmed through the use of an external PC over the JTAG connection. Functionality of the design was simple; a single reconfigurable module which could be implemented as either an addition or subtraction unit and a single static module which controlled the function of 4 on board light emitting diodes (LEDs) were written in VHDL and synthesized following the modular design flow. The design was created such that proof of reconfiguration could be tested and monitored with the use of an oscilloscope. The team was successful in the development of a proof of concept for partial reconfiguration.

Development of a self-reconfiguring system, the secondary objective of this project, proved to be a much more complex task. Similarly to the primary objective, development of this system required the use of a new design flow and toolset. The integration of PowerPC peripherals to the design required the integration of two separate design methodologies. The PowerPC design (using the Xilinx Embedded Development Kit) would need to be merged with the previous PR design (using Xilinx PlanAhead) to create a self reconfiguring system. Although the completion of a self-reconfiguring system was not realized, several milestones were achieved during development. The team was able to demonstrate the ability to program and load a PowerPC design to the development board. Also, the ability to write and read from an external flash component was demonstrated. This is required because a significant amount of memory is needed to store the configuration files handled by the PowerPC. Unfortunately, the integration of a PowerPC design and the previous PR design was not completed as many complications prevented successful combination of the two design flows. The team is confident however that with more time and the development of a more integrated tool flow, this design could be accomplished.

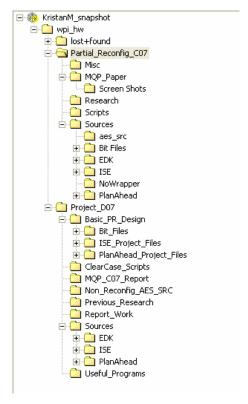

The third and final objective of this project was to create a project base for which future students can branch off of. This included the use of a Version Object Base (VOB), using the Rational ClearCase tool, which all research and work material was stored on. The VOB for this project was initially created by General Dynamics and will be made available for any future project to view and work from. In order to allow for a smooth transition to the subsequent project, the team needed to setup a directory structure as well as make significant documentation of steps taken throughout the process. The development of the first two objectives was monitored and noted throughout the project so the following project(s) could minimize transition time. With the addition of code and project notes, useful reading and tutorials used were provided as well as research examples which were found to be helpful in understanding the Partial Reconfiguration design process.

Overall, the completion of these objectives proved to be taxing as the software available did not always function as promised. Partial Reconfiguration is still a fairly underused practice and the tools for creating these types of designs have not yet caught up with the hardware's full capabilities. However, the primary goal, a proof of concept for Dynamic Partial Reconfiguration was realized. In doing so, a basic foundation for future projects to branch from was created, opening the doors for further advances in partial reconfiguration design.

## Acknowledgements

We would like to thank General Dynamics C4 Systems as well as Worcester Polytechnic Institute for providing us with the opportunity to complete this Major Qualifying Project. Furthermore, we would like to thank Brendon Chetwynd for his constant support on site at General Dynamics. Brendon proved to be a constant motivator and never failed to supply us with a sometimes never-ending request for software and hardware tools. We would also like to thank Gerardo Orlando for his technical advice and support throughout the course of the project. We also thank Chris Chalifoux of General Dynamics and Natalie Chin (WPI '01) for providing ClearCase assistance and technical support.

Finally, we would like to thank Professor John McNeill for advising this project and keeping this opportunity open to us in the absence of Professor Berk Sunar. This project would not have been completed without his guidance during the preparation phase or willingness to take on an advising role normally outside his scope of interest.

## **Table of Contents**

| Α  | Nbstract                                              | ii   |

|----|-------------------------------------------------------|------|

| Α  | Authorship                                            | iii  |

| E  | xecutive Summary                                      | iv   |

| Α  | Acknowledgements                                      | vii  |

| T  | able of Contents                                      | viii |

| T  | able of Figures                                       | xii  |

| 1: | : Introduction                                        | 1    |

| 2: | : Background                                          | 3    |

|    | 2.1: Field Programmable Gate Arrays (FPGA)            | 3    |

|    | 2.2: Partial Reconfiguration (PR)                     | 3    |

|    | 2.2.1: Types of partial reconfiguration               | 4    |

|    | 2.2.2: PR example and benefits                        | 4    |

|    | 2.3: Available Tools                                  | 4    |

|    | 2.3.1: Memec Virtex II – Pro FF1152 Development Board | 4    |

|    | 2.3.2: Xilinx ISE 8.2i                                | 5    |

|    | 2.3.3: Xilinx iMPACT                                  | 6    |

|    | 2.3.4: Xilinx PlanAhead 8.2.7                         | 6    |

|    | 2.3.5: Xilinx Embedded Development Kit (EDK)          | 7    |

|    | 2.3.6: Rational ClearCase                             | 8    |

|    | 2.4: Previous Work                                    | 10   |

|    | 2.5 : General Dynamics C4 Systems (GDC4S)             | 10   |

|    | 2.6: Advanced Encryption Standard (AES)               | 11   |

|    | 2.7: Triple Modular Redundancy (TMR)                  | 12   |

|    | 2.8: TMR, AES, and PR Together                        | 13   |

| 3  | : Design Requirements                                 | 15   |

|    | 3.1: Modular Design Flow                              | 15   |

|    | 3.2: Modular Partial Reconfiguration Flow             | 16   |

|    | 3.3: Test Circuit Overview                            | 16   |

|    | 3.3.1: Preliminary Requirements                       | 16   |

|    | 3.3.2: Programming Methods                            | 17   |

|    | 3.4: Process Overview                                 | 18   |

|    | 3.4.1: Design and Synthesis                           | 18   |

|    | 3.4.2: Budgeting and Constraints                      | 19   |

|    | 3.4.3: Implementation and Assembly                     | 1 |

|----|--------------------------------------------------------|---|

|    | 3.4.4: Download and Testing                            |   |

| 4: | Implementation – Basic Circuit                         |   |

| 4  | .1: Software Requirements                              |   |

| 4  | .2: HDL Design and Synthesis                           |   |

|    | 4.2.1: Design Overview                                 |   |

|    | 4.2.2 Design Intent                                    |   |

|    | 4.2.3: Top Level                                       |   |

|    | 4.2.4: Module Level                                    |   |

|    | 4.2.5: Bus Macros                                      | 2 |

| 4  | .3: Implementation with PlanAhead                      | 2 |

|    | 4.3.1: Project Creation                                | 2 |

|    | 4.3.2: Budgeting and Constraints                       |   |

|    | 4.3.3: Partial Re-config Tool                          |   |

| 4  | .4: Programming                                        | 2 |

|    | 4.4.1: Configuration over JTAG                         | 2 |

| 4  | .5: Creation of a PR AES Implementation                | 2 |

|    | 4.5.1: Design Overview                                 | 2 |

|    | 4.5.2: Limitations                                     | 3 |

|    | 4.5.3: Steps Required                                  | 3 |

|    | 4.5.4: Feasibility                                     | 3 |

| 4  | .6: Testing and Results – Basic Circuit                |   |

|    | 4.6.1: Overview                                        |   |

|    | 4.6.2: Bit Stream Differences                          |   |

|    | 4.6.3: Desired Functionality – Configuration over JTAG |   |

|    | 4.6.4: Results – Configuration over JTAG               |   |

| 5: | Self-Partial Reconfiguration Implementation            |   |

| 5  | .1: Overview                                           |   |

|    | 5.1.1: Advantages over JTAG Partial Reconfiguration    |   |

|    | 5.1.2: PowerPC vs. Custom Logic                        |   |

| 5  | .2: Design Procedure                                   |   |

|    | 5.2.1: Overview                                        | 3 |

|    | 5.2.2: BRAM vs. Flash Memory                           |   |

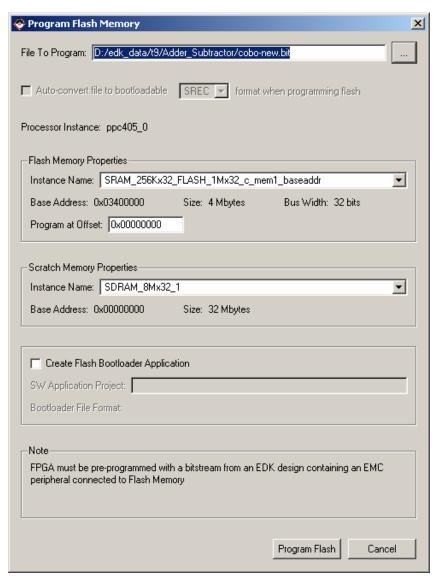

|    | 5.2.3: Programming Flash Memory                        | 5 |

|    | 5.2.4: Programming - Configuration over ICAP / PowerPC | : |

| 5.2.5: PlanAhead Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.2.6: Flow Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41       |

| 5.3: Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42       |

| 5.3.1: Lack of design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42       |

| 5.3.2: Removal of DCM wrappers                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42       |

| 5.3.3: EDK Makefiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43       |

| 5.3.4: Synthesis parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43       |

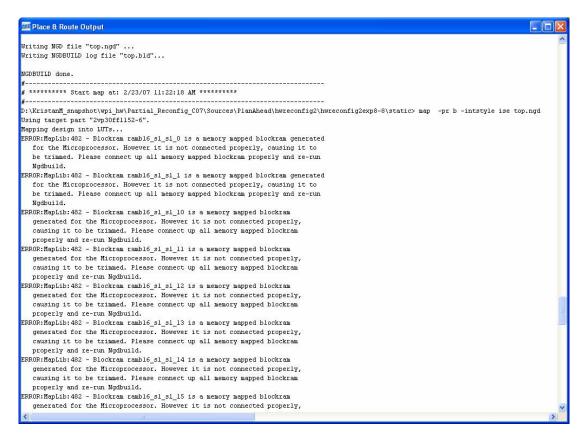

| 5.3.5: AREA_GROUP errors when mapping bus macros                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43       |

| 5.3.6: Memory mapping errors on static implementation                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43       |

| 5.4.7: ClearCase check-in errors for binary files                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44       |

| 5.4: Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44       |

| 5.4.1: Successes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44       |

| 5.4.2: Failures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45       |

| Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46       |

| Goal Completion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46       |

| Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47       |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48       |

| Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50       |

| Appendix A - Basic Circuit – PR over JTAG Design                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54       |

| A.1: Top Level - VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54       |

| A.2: Reconfigurable Module – Addition Logic - VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| A.3: Reconfigurable Module – Subtraction Logic - VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56       |

| A.3: Reconfigurable Module – Subtraction Logic - VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57       |

| A.4: Static Module – LED Display – VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57<br>58 |

| A.4: Static Module – LED Display – VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57<br>58 |

| A.4: Static Module – LED Display – VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 575860   |

| A.4: Static Module – LED Display – VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| A.4: Static Module – LED Display – VHDL  A.5: Clock Converter Module  Appendix B – Self Reconfiguration – PR over ICAP design  B.1: XST synthesis parameter file (system_xst.scr)  B.2: Sample ICAP test program                                                                                                                                                                                                                                                                                 |          |

| A.4: Static Module – LED Display – VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| A.4: Static Module – LED Display – VHDL  A.5: Clock Converter Module  Appendix B – Self Reconfiguration – PR over ICAP design  B.1: XST synthesis parameter file (system_xst.scr)  B.2: Sample ICAP test program  B.3: HWICAP User-defined tools – Header file  B.4: HWICAP User-defined tools – Implementation code                                                                                                                                                                             |          |

| A.4: Static Module – LED Display – VHDL  A.5: Clock Converter Module  Appendix B – Self Reconfiguration – PR over ICAP design  B.1: XST synthesis parameter file (system_xst.scr)  B.2: Sample ICAP test program  B.3: HWICAP User-defined tools – Header file  B.4: HWICAP User-defined tools – Implementation code  B.5: Bit file to array Perl tool                                                                                                                                           |          |

| A.4: Static Module – LED Display – VHDL  A.5: Clock Converter Module  Appendix B – Self Reconfiguration – PR over ICAP design  B.1: XST synthesis parameter file (system_xst.scr)  B.2: Sample ICAP test program  B.3: HWICAP User-defined tools – Header file  B.4: HWICAP User-defined tools – Implementation code  B.5: Bit file to array Perl tool  B.7: Bitstream Combiner Script                                                                                                           |          |

| A.4: Static Module – LED Display – VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| A.4: Static Module – LED Display – VHDL  A.5: Clock Converter Module  Appendix B – Self Reconfiguration – PR over ICAP design  B.1: XST synthesis parameter file (system_xst.scr)  B.2: Sample ICAP test program  B.3: HWICAP User-defined tools – Header file  B.4: HWICAP User-defined tools – Implementation code  B.5: Bit file to array Perl tool  B.7: Bitstream Combiner Script  B.8: Diff on customized system.vhd based on generated file  Appendix C: Basic PR – Troubleshooting Guide |          |

| E.1: VOB directory structure                                         | 73 |

|----------------------------------------------------------------------|----|

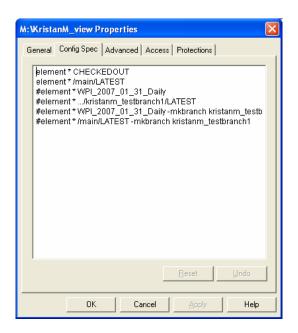

| E.2: ClearCase config spec                                           | 73 |

| E.3: Add to source control recursive script (add-to-src-control.bat) | 74 |

| E.4: Timestamp label generator (datelabel.sh)                        | 76 |

| E.5: Miscellaneous recursive commands                                | 76 |

| E.5.1: Revert checked out files to the VOB version (revert.bat)      | 76 |

| E.5.2: Push changes to VOB but keep elements checked out (push.bat)  | 77 |

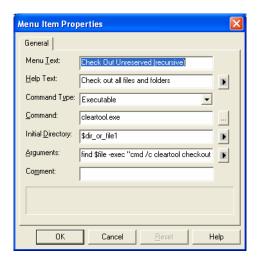

| E.5.3: Recursive unreserved check out                                | 77 |

| E.5.4: Recursive check in                                            | 77 |

| E.6: ClearCase Menu Administrator                                    | 77 |

| E.7: Snapshot views vs. Dynamic views                                | 78 |

|                                                                      |    |

## **Table of Figures**

| Figure 2.1 – Memec Virtex II Pro ff1152 Dev. Board                   | 5  |

|----------------------------------------------------------------------|----|

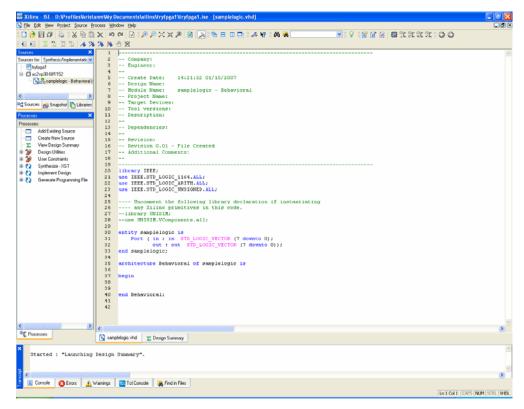

| Figure 2.2 – ISE Design Environment                                  | 5  |

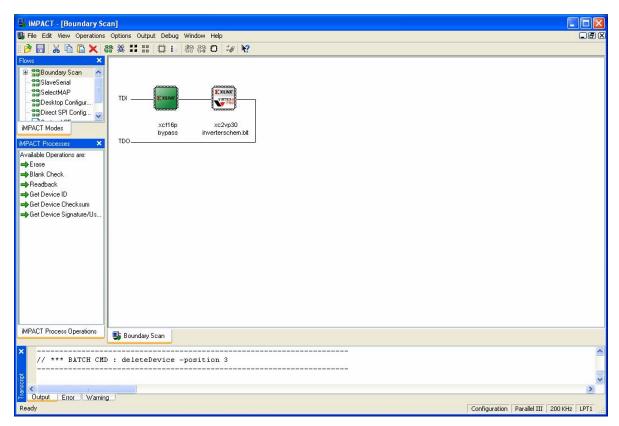

| Figure 2.3 – Xilinx Impact Software                                  | 6  |

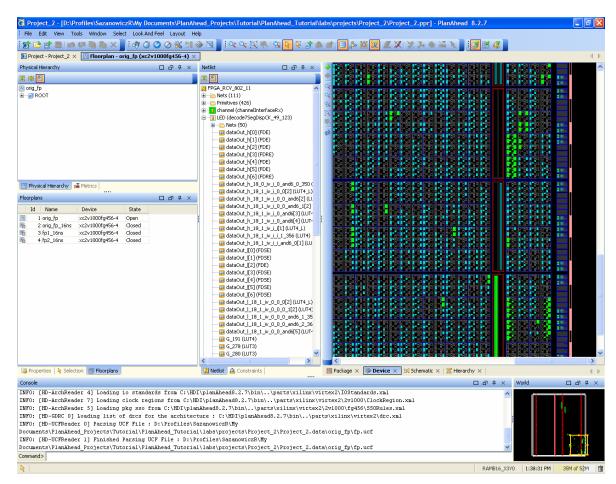

| Figure 2.4 – PlanAhead Design Environment                            |    |

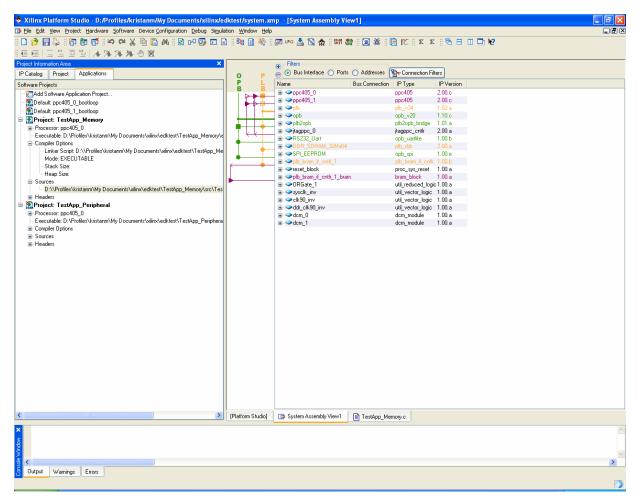

| Figure 2.5 – Xilinx EDK Design Environment                           | 8  |

| Figure 2.6 - Version tree of an element                              | 9  |

| Figure 2.7 - Diff viewer showing changes between versions            | 10 |

| Figure 2.9 – Triple Modular Redundancy Description                   | 12 |

| Figure 2.10 – Triple Modular Redundant System Description            | 12 |

| Figure 3.1 – Modular Design Flow                                     | 15 |

| Figure 4.1 – Top Level Design Hierarchy                              | 2  |

| Figure 4.2 – XST Process Properties                                  | 23 |

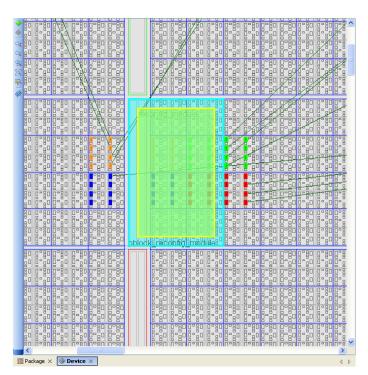

| Figure 4.3 – Reconfigurable Module (Yellow) in PlanAhead Device View | 25 |

| Figure 4.4 – Bus Macro Placement (Various Colors)                    | 26 |

| Figure 4.5 – Partial Reconfig GUI                                    | 28 |

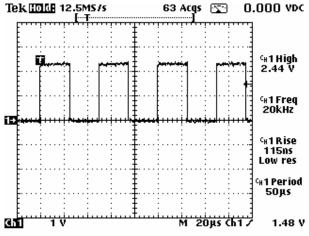

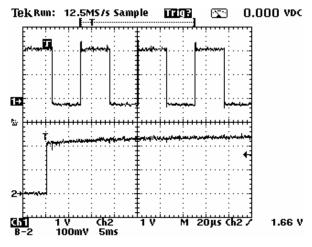

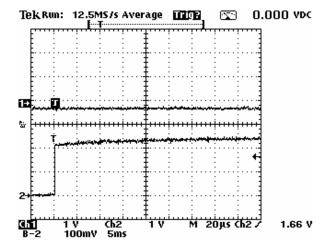

| Figure 4.6 – 2Hz LED                                                 | 32 |

| Figure 4.7 – 20KHz LED                                               | 32 |

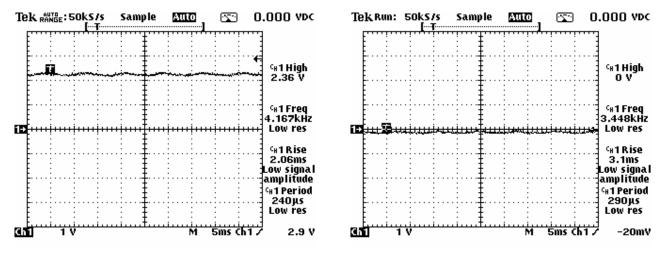

| Figure 4.8 – Solid LED in Off State                                  | 33 |

| Figure 4.9 – Solid LED in ON State                                   | 33 |

| Figure 4.10 – 20Khz LED w/ Reconfiguration                           | 34 |

| Figure 4.11 – Solid ON LED w/ Reconfiguration                        | 34 |

| Figure 5.1 – Top Level Design Hierarchy                              | 37 |

| Figure 5.2 – Flash Memory Programmer                                 | 38 |

| Figure 5.3 – Flash Combination Script                                | 39 |

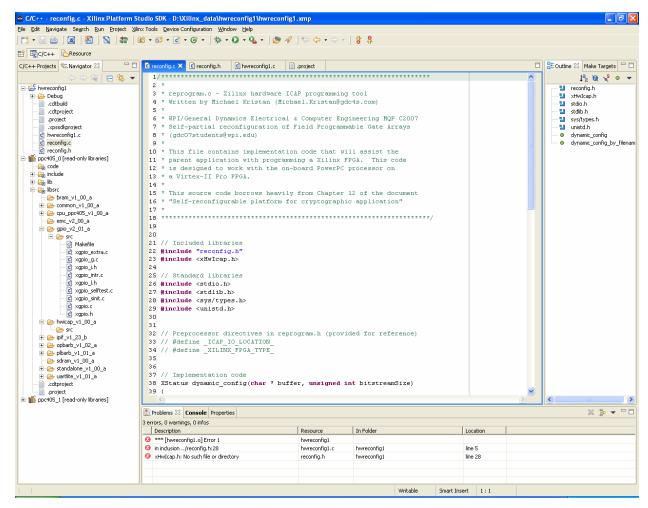

| Figure 5.4 – Xilinx SDK Screen Shot                                  | 40 |

| Figure 5.5 - Map error on Static Implementation                      | 44 |

| Figure 5.6 - PowerPC is unreachable via ITAG and the Xilinx debugger | Δ. |

#### 1: Introduction

As the protection of digital data becomes more important to society, reliable encryption systems are needed in order to properly safeguard confidential information. It has been shown that most failures of modern encryption systems are due to implementation failures, rather than algorithm failures, and therefore it is critical to ensure that the implementation is not compromised. Implementing an encryption system on reconfigurable logic such as a field programmable gate array (FPGA) is desirable for its ability to be easily reprogrammed like a microcontroller, but allows for the performance advantages of custom digital hardware like an application specific integrated circuit (ASIC). There is also a significantly lower cost for custom digital hardware of an FPGA when prototyping and for production in small quantities compared to an ASIC. The major disadvantage of FPGA devices is that they may be left vulnerable to side channel attacks or even accidental configuration changes, due to the fact that the configuration of the digital hardware can be altered. Fortunately, when the configuration is accidentally or maliciously changed, it is often the case that only a portion of the design becomes unusable. Therefore, in cooperation with General Dynamics C4 Systems, this project investigates designing a system which uses the partial reconfiguration feature of Xilinx FPGAs to repair or update portions of a circuit without disrupting normal operating activity.

Advances in FPGA hardware and software design tools for the FPGA hardware allow for on the fly reconfiguration of programmable logic. This ability allows programmers to design a chip which can be reconfigured without disrupting operation and can be used to recover a compromised device. Partial reconfiguration can also be used to allow larger complex designs to be implemented on devices with fewer resources than would normally be required for a complete implementation. The most common method for implementation of partial reconfiguration is one in which a modular design approach is used. The logic is configured in a manner such that one module is dynamically reconfigured while another module is retained in a static configuration for performing operations which do not change. With this approach, a portion of the chip is continuously being reconfigured to its original condition or to a new configuration regardless if an error is detected. Partial reconfiguration may also be implemented in conjunction with Triple Mode Redundancy (TMR) to create a system with increased reliability. TMR utilizes a voting circuit to detect differences in output from three identical systems. Often, this voting system is replicated three times as well, to further increase dependability. The ultimate goal is to develop a TMR system which utilizes partial reconfiguration to repair damaged modules in the background, offering seamless, reliable operation of a secure system.

The first step in the creation of a secure, redundant, self-reconfiguring system is the development of the partial reconfiguration module. In order to implement a partially reconfigurable encryption algorithm, a proof of concept of partial reconfiguration must be completed using a smaller, simpler system. The simple test system

includes the design of an arithmetic logic unit which allows the user to switch between operations causing the operation module to be reconfigured. This setup can be tested and easily interfaced with the available I/O ports on the development board. Upon successful completion of a partially reconfigurable circuit, the goal is to implement an advanced encryption algorithm with partially reconfigurable characteristics. Successful completion of this task will allow future project teams to integrate this algorithm with a TMR system.

## 2: Background

This project investigates the use of several technologies, some of which are still considered fairly academic and therefore are not standard digital logic nomenclature (specifically Partial Reconfiguration). In addition, there are some related technologies, which will not be implemented in our project due to time constraints, however they will be implemented in future projects based on our project, including TMR and AES.

### 2.1: Field Programmable Gate Arrays (FPGA)

FPGAs were invented in 1984 by Ross Freeman, co-founder of Xilinx [24]. FPGAs provide users with an environment were the user is able to quickly develop and implement a circuit or module at low cost and fast turnaround time. FPGAs are developed using simple circuitry that is meshed together to provide the same complex circuitry that a traditional circuit board provides. The drawback to using an FPGA is that unlike traditional application specific integrated circuits (ASICs), FPGA circuits have a high propagation delay and therefore a slower processing time [11].

Despite the drawbacks to using an FPGA over a traditional circuit board, FPGAs can be used quite easily with Triple Modular Redundancy circuits. Quick reprogramming and scrubbing techniques provide the end user with a reliable output that allows the circuit to be automatically reprogrammed without any end user maintenance.

## 2.2: Partial Reconfiguration (PR)

Partial reconfiguration is the practice of reprogramming only a portion of an FPGA. More specifically, dynamic partial reconfiguration denotes the ability to reprogram a portion of a circuit while it is operating. This is done without a need for the chip to power down or be reset. For the sake of brevity, dynamic partial reconfiguration will be considered the same as partial reconfiguration in the reamainder of this report. Partial reconfiguration can be accomplished with the aid of an external device such as a JTAG connector or can be managed by an on-board processor. Partial reconfiguration can be implemented through the use of the Xilinx ISE tools either stand alone or in conjunction with PlanAhead software. Dependant on design intent, partial reconfiguration generally requires the use of a modular design flow. Modular design requires additional procedures for synthesis and implementation and adds complexity not found when utilizing the basic design flow. In general, modular design allows for simultaneous development of different modules which together complete the design of an FPGA. This design procedure is most commonly used by engineering and programming teams who must coordinate efforts to save time and money. Modular design also allows a team to modify non-working or unstable modules without affecting those which are functioning properly. The

modular design flow consists of two phases. Phase 1 incorporates Design Entry and Synthesis in which the team leader completes a top level design and each team member completes the design entry and synthesis for their particular module. Phase 2 incorporates the creation of top level constraints, implementation of each module, and final assembly.

#### 2.2.1: Types of partial reconfiguration

There are two types of partial reconfiguration, modular and difference-based. These design procedures hold certain advantages to each other, and each is limited in ability. Modular partial reconfiguration allows for portions of the FPGA to be recreated or even redesigned. This is most commonly used to implement large designs on smaller and less expensive chips. This is generally accomplished by splitting the design and reconfiguring one module over another in order to save resources. Modular reconfiguration can also be used to repair "broken" chip modules without affecting the operation of other areas of the chip when seamless operation is crucial to the application. Difference-based partial reconfiguration follows a different design flow. This approach requires the creation of a bit stream file which only includes design differences from one design to another. The initial design is created and then the Xilinx FPGA editor can be used to design logic changes directly on the FPGA. A partial bit stream file is then created which when loaded only makes changes based on the difference in the two designs. This flow allows for extremely quick transitions between the two designs but is limited in scope to what It can be used for.

#### 2.2.2: PR example and benefits

An example of a system that could benefit from partial reconfiguration would be a basic arithmetic logic unit (ALU). The idea would be to make the math and logic operations modular in design so that depending on the function that is needed, the appropriate module could be inserted into the FPGA. Although this process is essentially unnecessary for such a simple circuit, in the case of larger and more demanding circuits a smaller FPGA could be used as opposed to one that could store all logic circuits at the same time. Creation of a simple ALU is the first process for a proof of concept of partial reconfiguration and will lay the groundwork for development of a more advanced encryption algorithm with partial reconfigurability.

## 2.3: Available Tools

#### 2.3.1: Memec Virtex II – Pro FF1152 Development Board

The Memec Development board used for this project includes a Xilinx XCVP30 FPGA. This board is designed for extreme flexibility in high end applications. The development board includes two 32mb SDRAM blocks as well

as 2 integrated PowerPC processors. Xilinx 8.2i ISE software allows for programming through either Parallel or USB to JTAG connections. [14]

Figure 2.1 - Memec Virtex II Pro ff1152 Dev. Board

#### 2.3.2: Xilinx ISE 8.2i

The primary tool used to design circuits is the Xilinx ISE. ISE allows users to design circuits in both schematics and VHDL [26]. Basic simulation can be done in Xilinx before it is sent to the board. Xilinx provides a number of tutorials and a large number of online resources that serve as an excellent reference.

Figure 2.2 – ISE Design Environment

#### 2.3.3: Xilinx iMPACT

iMPACT is the tool that is used to program the FPGA [25]. iMPACT can be used in a direct SPI configuration or in a boundary scan configuration. iMPACT also provides the user with the ability to erase, program, and verify the FPGA itself or the PROM on the board. The advantage to programming the PROM is that changes are retained after the device shuts off so that there is no need to reprogram the device after hitting the reset button or by turning on the power. Aside from providing options for downloading to the Xilinx device, iMPACT also provides the capability of merging bit streams with block memory maps provided by the EDK development.

Figure 2.3 - Xilinx Impact Software

#### 2.3.4: Xilinx PlanAhead 8.2.7

PlanAhead is another component of the Xilinx Design Studio. PlanAhead's main purpose is to customize the way circuits designed in ISE are laid out on the FPGA as well as providing timing and placement analysis to improve circuit function [19]. By using this tool, users can group circuits and modules. The benefit of this is that if each module is in its own area, the task of partial reconfiguration becomes much easier as only one area is being programmed and will not affect any of the other sections. This task is known as floor planning. Separation of modules and implementation of bus macros is facilitated within the software as the numerous

tools required to complete these procedures are integrated into a single platform. These tasks can be completed in Xilinx ISE tools however it is more difficult to coordinate these changes as scripting may be required. PlanAhead also provides a useful set of design rule checks which can be used to improve designs and provide suggestions to the designer. The integration of several features into a single piece of software allows the designer to use a simplified set of tools which are better designed to work with each other. DRC allows for error checking to save time further in the design flow.

Figure 2.4 - PlanAhead Design Environment

#### 2.3.5: Xilinx Embedded Development Kit (EDK)

The Embedded Development Kit (EDK) provides users with a way of programming and using the onboard microprocessors that are on the development board [20]. The Vertex-II comes with two IBM PowerPC processors as well as the required cores for development of a MicroBlaze controller. The EDK allows for development on either platform. Use of the Xilinx EDK will be required for any microcontroller development related to self – reconfiguration. Although self reconfiguration may be completed through the development of custom logic, use of the PowerPC allows for an added level of scalability for project changes. The EDK is used

to synthesize all peripherals required for operation of the PowerPC as well as the development of embedded applications. This software operates as a separate entity but provides the possibility to export its designs in a format readable by Xilinx ISE as well as PlanAhead. The EDK significantly raises the complexity of the design flow and is expected to cause difficulties with the integration of different flows. A screen shot of the EDK environment is shown below in Figure 2.5.

Figure 2.5 - Xilinx EDK Design Environment

#### 2.3.6: Rational ClearCase

ClearCase is a source control management and revision system that is very popular in large development environments with multiple people contributing. With ClearCase, files are stored on a server in a repository. Users can then check files in and out of the repository and make changes. If a user does not want to work on the main development line and instead isolate him or herself from other check-ins a branch can be created. Once work is done in a particular branch, those changes can be merged back into the main line, or the branch

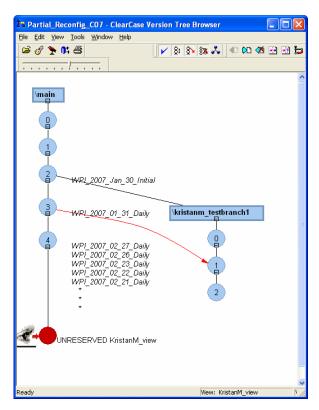

can be abandoned. Figure 2.6 shows how ClearCase graphically shows relationships between each branch and each checked-in element.

Figure 2.6 - Version tree of an element

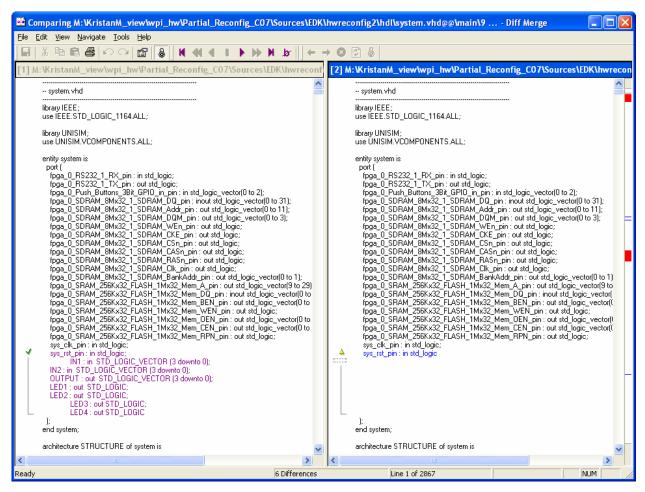

ClearCase is powerful because in addition to controlling check-ins and check-outs, it will merge changes that happen between multiple users should multiple copies of a document be checked out at the same time. The differential viewer utility in figure 2.7. highlights changes between versions of a file within ClearCase.

Figure 2.7 - Diff viewer showing changes between versions

### 2.4: Previous Work

This project draws from coursework and previous Major Qualify Projects completed with General Dynamics C4 Systems. Most notably, the project entitled "Efficient AES Implementation with Modes of Operation" completed in March of 2002 and "A Self Healing Circuit Implementing TMR" completed in April of 2006. Although this project does not directly deal with Triple Modular Redundancy, it is meant to lay a foundation for future work in that area. Partial Reconfiguration and TMR can be implemented together for increased reliability and stability of an logic system. Ultimately, the implementation of a modern encryption algorithm, such as AES, within a TMR Partial Reconfigurable system is the goal. This project however is limited in scope to the creation of a partially reconfigurable design.

## 2.5: General Dynamics C4 Systems (GDC4S)

General Dynamics C4 Systems is a subsidiary of General Dynamics Corporation in Falls Church, Virginia. C4 Systems falls under General Dynamics Information Systems & Technology line of business. General Dynamics

C4 Systems is a leading integrator of network-centric solutions. Their leadership credentials come from applying world-class capabilities to create high-value, low risk solutions for use on land, at or under the sea, in the air and in space. Based in Scottsdale, Arizona, General Dynamics C4 Systems employs approximately 11,000 people worldwide and is focused on the development, design, manufacturing and integration of secure communication, information and technology solutions [7].

General Dynamics is the sponsor of this research and has graciously provided office space, software, and hardware in order to complete this project. Although General Dynamics is a government contractor and deals with classified information on a daily basis, all of this work was conducted in the public domain.

### 2.6: Advanced Encryption Standard (AES)

Advanced Encryption Standard (AES) was adopted by the United States government on November 21, 2001 and became effective as of May 26, 2002 [6]. AES effectively replaced the previous Data Encryption Standard (DES). Initially designed by Joan Daemen and Vincent Rijmen, the Rijndael algorithm was chosen by the National Institute of Standards and Technology (NIST) to be used for AES. AES has seen widespread use and is an extremely common form of encryption among software and hardware applications. Unlike its 56 bit predecessor DES, AES utilizes a 128 bit block structure with key sizes in 128, 192, and 256 bit forms [5]. In perspective, the 128 bit key size AES algorithm provides over 10<sup>21</sup> more possible keys than a 56 bit key size DES algorithm [1]. This large key size causes AES to be extremely difficult to crack when using brute force methods. In its 4 years of existence as the government encryption standard, AES has been utilized all over the nation and world for both government and non-governmental use. AES owes its success due to its low cost, high speed, high security and low memory requirements.

Dating to 2006, the only successful attempt at breaking an AES system has involved side channel attacks [10]. A side channel attack is different from an attack based on a weakness in the algorithm itself and instead utilizes leaked information from the system itself. This type of attack is often based on timing information or transmission of leaked electromagnetic data and may require internal knowledge of the hardware system. Timing and power monitoring attacks involve physical monitoring of data flow and power usage through a system CPU and can be used to determine the size of the key being used for encryption. Data can also be leaked through radio waves generated from the encryption system. This vulnerability however can be easily safeguarded by the use of physical shielding for the device. In all cases of side channel attacks, physical access to the system is often required and can be defeated with better computer security procedures. Advances in hardware technology continually strengthen the security of these systems and allows AES to remain a secure cryptographic system.

### 2.7: Triple Modular Redundancy (TMR)

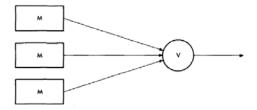

Triple Modular Redundancy or TMR is the concept of duplicating a black box circuit three times and using the output that appears in a majority of the black boxes. TMR was first proposed by Von Neumann in digital circuits that have binary output and is shown in Figure 2.9. TMR systems are setup by having a black box circuit or module (denoted M) replicated three times [21]. These outputs are then fed into a voting circuit. The voting circuit (denoted V) compares the three outputs and determines the winning result by taking the most popular result. The result from the circuit V is then passed along to the next device that relies on the output of M.

Figure 2.9 – Triple Modular Redundancy Description

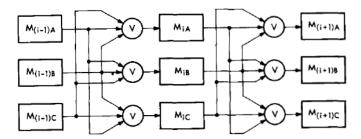

There is one big assumption to this using a basic TMR system as described above. According to [21], the major assumption is that the voting circuit V is perfect and will not fail. In order to mitigate the risk of the failure of the voting circuit, the voting circuit must also be tripled and made redundant. Figure 2.10 shows a TMR system where the voting system is also redundant. The result of each voting circuit is then uniquely fed into the next component which is also replicated three times. The process continues throughout the entire system passing from one module to the next.

Figure 2.10 – Triple Modular Redundant System Description

By using a redundant system, the risk of an overall system failure is reduced because a TMR system can withstand an individual failure of a component. If a black box circuit has a reliability of R, a TMR system's reliability can be shown as:

$3R^2 - 2R^3$  [21]

As long as the reliability has a probability of .5 or greater, the reliability of the TMR system will be greater than the individual system as described [21]. An odd number of replications are chosen because this allows for a majority to always occur in a vote. Having an even number of components introduces the risk of having a tie [21].

TMR is a chosen solution for implementing a highly reliable circuit because it has been has been in widespread use long enough to prove that it is useful. Furthermore, the use of TMR has been successfully implemented in systems that are exposed to harsh environments and situations where circuits are very likely to fail and cannot be maintained easily. Examples of these circuits can be found in the PANSAT satellite systems designed by Worcester Polytechnic Institute. Given that systems in space need to work without any user intervention, a reliable system needs to be in place to ensure that data is processed correctly.

The other argument for TMR's use is that TMR is easy to implement. Once a module has been designed, it simply has to be replicated three times. Even though there is a small time investment associated with building the voting circuit, TMR designs are quick to build at least in theory.

#### 2.8: TMR, AES, and PR Together

The basic foundation of this project as well as future projects involves the coordination of Partial Reconfiguration with Triple Modular Redundancy design methodologies. Ideally, these two technologies could be used to implement a stable, self healing AES implementation as well as any other useful encryption algorithm. Through use of an internal or external microprocessor, the system could be designed such that when the TMR voting circuit detects an error, the FPGA will partially scrub itself without interrupting the flow of data. This could eliminate encryption errors altogether as well as any downtime or need for human interference. The ideal result would be a completely self sustained system with extraordinarily high reliability.

Although TMR could be realized without the implementation of PR, system downtime would be required in order to scrub the circuit. In some cases, downtime may be an extremely undesirable circumstance. For example, if a non – PR, TMR design begins abnormal operation, the voting circuit would detect the bad output and discontinue use of that circuit. The entire design could then be realized to either scrub entirely at a certain time interval through use of the internal configuration port or set for scrubbing via user I/O. If a PR design were realized, the system would then only need to scrub the "broken" logic when necessary. This would eliminate the need for user I/O or a regular scrubbing interval. Although, both of these features could still be implemented if desired.

Partial Reconfiguration brings these new advantages to encryption implementation with the use of an FPGA. Increased reliability and the implementation of a self – sustaining system are further evidence that hardware encryption techniques are further evolving for any algorithm type.

## 3: Design Requirements

The basic design requirements for the initial working prototype are a direct result of thorough background research and identification of a basic project. The requirements serve as an abstract methodology that lays a foundation for proceeding forward. Initially, modular design flow had to be investigated, along with its relation to partial reconfiguration. Next, the design of the test circuit and the ways which self-partial configuration will be implemented had to be identified. Finally, the overall design flow for synthesis and implementation is investigated.

#### 3.1: Modular Design Flow

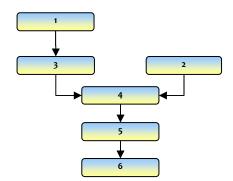

Creation of a partially reconfigurable circuit within the Xilinx ISE development environment requires the designer to use a modular design flow [17]. Modular design is often used when a project requires multiple team members to implement a design. More importantly, it permits for development of several pieces of a design simultaneously, saving time, and avoiding problems associated with more complicated circuits [15]. Separate modules can be designed, repaired, and implemented separately. This allows the designer to change one module without affecting another and creating a chain of unwanted dependency problems. The required modular design flow is described below. Steps diagrammed in parallel can be completed simultaneously [17].

- Top Level Design and Synthesis

- 2. Module Design / Synthesis

- 3. Top Level Budgeting

- 4. Active Module Implementation

- 5. Assembly

- 6. Device Download

Figure 3.1 - Modular Design Flow

This design flow must be followed in order to successfully complete a modular design. Basic steps must also be followed during each design phase for a successful design. The lead designer must create the top level design as well as initial budgeting and assembly steps. A top level design provides the input and output requirements for each module as well as allows the designer to move ahead with timing, location, and physical area constraints for the final design [9]. This can greatly reduce the amount of time required for a start to finish design.

#### 3.2: Modular Partial Reconfiguration Flow

Similarly to the modular design requirements previously described, partial reconfiguration also requires designers to utilize a specific modular design flow. This modular partial reconfiguration flow is very similar to the modular design flow described above with some added design requirements. These added requirements are detailed below [4].

- Area range constraints for reconfigurable modules must be applied

- Bus macros are required communication across reconfigurable modules

- Implementation must occur for each version of a reconfigurable module

- Assembly must occur for each combination of reconfigurable and static modules

- Full and partial bit files must be created for device download

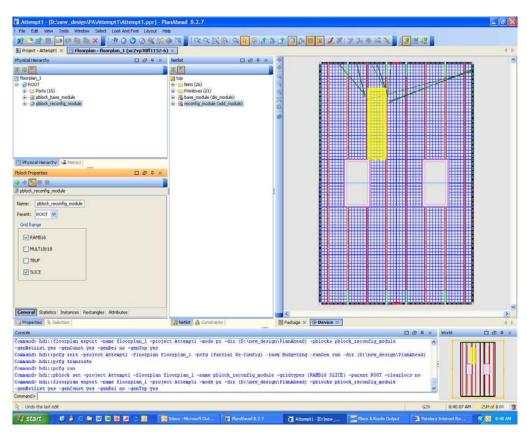

When creating a partially reconfigurable design, it is necessary to assign specific area constraints to any reconfigurable modules. This is done in order to differentiate which area of the FPGA will be rewritten by a partial bit file [4]. This task is traditionally completed with the aid of Xilinx Floorplanner. However, the Xilinx PlanAhead software has integrated floor planning, macro placement, module implementation, and assembly into a single GUI. The difficulty in creating a partially reconfigurable design is greatly reduced by the integration of these tasks into a single tool. PlanAhead replaces the use of Floorplanner, Pace, Constraints Editor, and FPGA Editor, as well as provides a GUI for NGDBuild, Map, and Par commands [13]. The PlanAhead software allows the user to avoid using multiple programs while scripting the more complicated assembly and implementation stages.

### 3.3: Test Circuit Overview

#### 3.3.1: Preliminary Requirements

Currently, partial reconfiguration is mostly limited to academic use and is only beginning to gain entrance in commercial applications. Xilinx ISE 8.2i does not officially support the partial reconfiguration design flow. However, there exists an early access toolset through Xilinx's protected website http://www.xilinx.com/support/prealounge/protected/. Because partial reconfiguration is a relatively unused practice, there exists little documentation on successful designs. In order to minimize errors and simplify troubleshooting, a preliminary test circuit should be designed for partial reconfiguration implementation. The test circuit must be able to limit complexity, provide I/O for testing, and be reconfigurable in nature. The development board provides eight DIP switches, eight output LEDS, and four push button switches which are ideal for basic testing. The design should include at least one reconfigurable and static module, both of which should provide output to the user and be independent of each other. For example, a static module with constant output to an LED would allow the user to test for errors while a separate module is reconfigured. The reconfigurable module would only need to provide different operations depending on which version is downloaded to the board. Adder and subtractor modules are ideal for this as they can utilize the same I/O ports and complete recognizable operations for the user.

#### 3.3.2: Programming Methods

Once the initial design is completed, there exist several methods of programming the full and partial bit files to the FPGA. The simplest involves programming over the JTAG chain like any standard (not using partial reconfiguration) design. Initially, a full design is loaded which includes any one version of the reconfigurable module. When a change is required, a new partial bit file is then downloaded which only changes the reconfigurable module while leaving the remaining modules operation uninterrupted. This method should be used for initial programming and testing as it reduces the complexity of the project.

Unfortunately, partial reconfiguration over JTAG is not feasible in a final product as it requires both a full computer and a specialized JTAG tool. Although almost all Xilinx FPGAs support partial reconfiguration, we need to develop a system where the FPGA can reload its own configuration, either from external memory or from data within the bit stream itself. Therefore, we will use the ICAP (internal configuration access port) port, which is available on Virtex series devices. Although it may be possible to perform a JTAG scrub using the platform flash, controlled reconfiguration is preferred. This allows for several configurations to be loaded, rather than simply scrubbing the circuit with the already existing configuration.

To accomplish this, it is necessary to develop an embedded system within the FPGA itself and use the ICAP to reconfigure it with pre-stored configuration files. There are two directions that may be taken, either using custom logic or through the use of a microprocessor system. The microprocessor has the distinct advantage of the fact that Xilinx provides the custom logic necessary to interface with the ICAP, so working with it is done at a high level using the C programming language. The disadvantage of the microprocessor system is the added complexity and system overhead that may not be necessary for this design. However, the microprocessor also allows the design to be far more scalable to larger reconfiguration designs than the custom logic design, and allows for a simple interface to many additional peripherals (such as SDRAM, Flash and RS-232) without requiring the time to write the VHDL for the custom logic implementations. In addition, the Virtex-II Pro device includes two hardware core 32-bit PowerPC microprocessors built in. Therefore, the processor itself does not require any FPGA resources; only the interface peripherals will use FPGA resources.

In addition to the choice between custom logic and microprocessor control for the ICAP, a decision must be made on where to store the partial reconfiguration bit files. The two primary choices are within the FPGA bit stream itself, or in external flash memory. The Memec Virtex II – Pro XC2VP30 – FF1152 development board includes a P160 Communications Module 2 add-on. This additional module includes 4 MB of flash memory and can be used to store the partial bit files. Use of the FPGA bit stream is much simpler, as it does not require programming the on-board flash memory or the expansion module. Additionally, it will work on any board using this FPGA. However, there is a distinct disadvantage to using the FPGA bit stream – in that it uses up the FPGA's resources. This eliminates one of partial reconfigurations major design advantages of implementing large configurations on less capable FPGA's. However, the 4 MB flash memory provided with the P160 module is able to hold at least 2 complete FPGA configurations (and many smaller partial configuration modules). The flash memory can also be used for storage of the code for the microprocessor. This further reduces the FPGA resource requirements because the only code required in the bit stream is a boot-loader to load the code out of flash memory.

#### 3.4: Process Overview

#### 3.4.1: Design and Synthesis

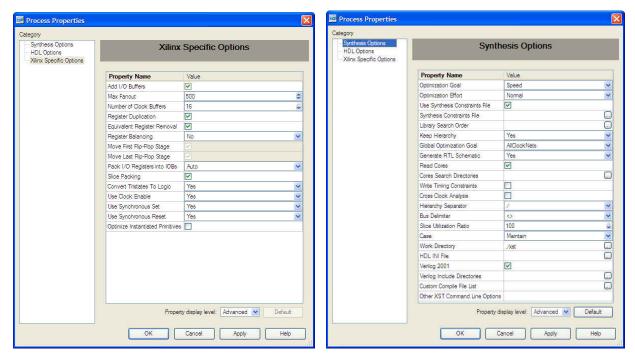

Modular partial reconfiguration requires the user to follow a specific design flow. This flow is similar to the more common modular flow but has added requirements for partial reconfiguration. The earliest step for PR design involves HDL design and synthesis. The designer may use his or her preferred design method and synthesis tool for this task.

Design and synthesis involves several added requirements. When coding at the top level it is necessary that all logic be constrained to "black boxes". This means that the top level must only include I/O logic, "black boxed" modules, and bus macro instantiations. Creating a "black box" module in VHDL means that the designer neglects to include the source VHDL for the module during top level synthesis. This step is important for the following initial budgeting stage. Each module must be synthesized separately in its own project and each reconfigurable module must use the same number of input and output ports. Reconfigurable modules must pass all I/O data through bus macros, ensuring that no data paths are lost during reconfiguration. Before synthesis, it is necessary that the designer include Bus Macro sources, and remember to not include any other module source. Finally the designer must ensure that the synthesis tool does not add I/O buffers during module synthesis and that hierarchy is preserved at all levels. Completion of this step produces top level and module net lists which will be used in subsequent steps.

#### 3.4.2: Budgeting and Constraints

The following steps can created with a number of different tools. Xilinx ISE provides command line tools and scripts which can be used to complete the following steps. However, Xilinx PlanAhead integrates many of these tools into a single GUI interface. Once a new project is created in PlanAhead it is only necessary to import the top level net lists as well as all static and one reconfigurable net list to begin initial budgeting. PlanAhead must also be configured to utilize the PR functionality. This can be done by entering the console command:

```

hdi::param set -name project.enablePR -bvalue yes

```

Constraints may be added manually via a text editor or graphically in PlanAhead. There are several items which must be remembered when budgeting a partially reconfigurable design. These steps are outlined below and our required for successful PR implementation.

- 1) All static logic must be confined to a single base p\_block with no range defined

- 2) PR regions must be confined to separate p blocks and assigned a range

- 3) PR p blocks must be rectangular and include the following constraints:

- a) Mode = Reconfig

- b) Min x and Min y coordinates must be positioned on an even slice

- c) Max x and Max y coordinates must be positioned on an odd slice

- d) BRAM ranges must also be assigned

- 4) Bus macros must be placed across PR region boundaries

- 5) I/O ports must be mapped to desired pins

- 6) DRC checks may be run to uncover planning errors

- 7) Floor-planned net list must be exported to a new (empty) directory.

Following these requirements will allow the designer to advance to the implementation stage of the design. Note that these steps only budget for an initial design. To budget subsequent reconfigurable designs, the user most only update the net list of the reconfigurable module they wish to change and export again to a new directory. The remaining design steps must then be carried out for each design.

#### 3.4.3: Implementation and Assembly

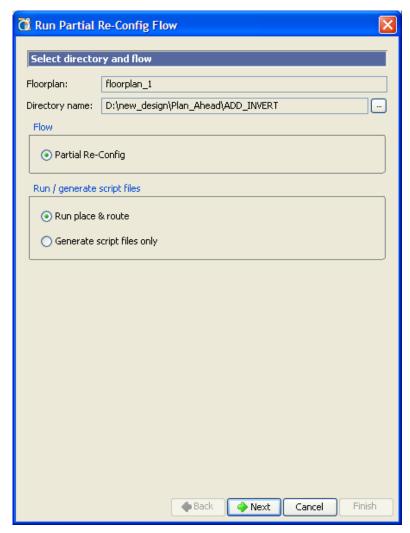

The remaining design steps can be completed by running the "Run Partial Reconfig" tool in PlanAhead. The user is provided with the option of generating a batch file to complete all remaining steps or the user may run through each step graphically. When running the "build all" command it is not possible to provide separate parameters inside of PlanAhead, instead the designer must edit the batch file manually. This process is

generally faster and requires less input. However, more complex designs may require significant changes, in which case the graphical interface may be more suited for the task. As the implementation and assembly steps are run, PlanAhead creates a directory structure. Full and partial bit files for each design are provided and the designer can then download the files to their development board and proceed with testing. It is important to remember that these steps must be run for each version of a reconfigurable module to create all desired partial bit files.

#### 3.4.4: Download and Testing

Successful completion of the previous steps results in the creation of full and partial bit files. Any full bit file can be downloaded to the Xilinx FPGA as the initial design. Similarly, any of the reconfigurable versions can be downloaded at any time. The number of bit files and file sizes is entirely dependant on the design. For an initial proof of concept, significant testing will be required to ensure no glitches occur. Functionality can then be observed by the user depending on the type of circuit created. As an initial proof of concept, it is important to implement a design which can be easily tested and repaired.

## 4: Implementation - Basic Circuit

#### 4.1: Software Requirements

Creation of a partially reconfigurable circuit requires that the designer follow a set of strict guidelines for modular design. Proper synthesis of the design also requires that the software be properly configured for the partial reconfiguration design flow. Due to the intricacies of software variations, it is important to note that this design was created using Xilinx ISE 8.2i with Service Pack 1 and Early Access PR tools installed. Following synthesis, implementation of the design was completed using PlanAhead version 8.2.7 with Partial Reconfiguration tools enabled. While it is certainly possible to implement this design using other software versions, changes in design approach would be inevitable.

### 4.2: HDL Design and Synthesis

#### 4.2.1: Design Overview

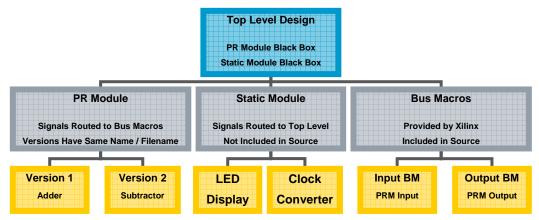

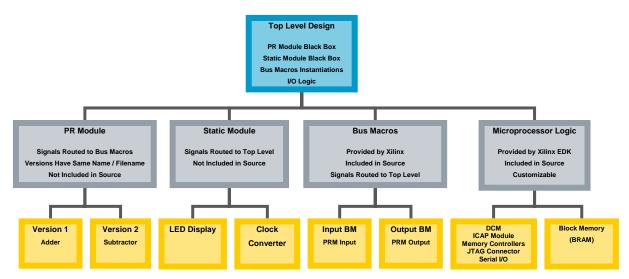

The partial reconfiguration design flow requires that the designer implement any static design separately than any reconfigurable portion. This can be done by separating logic into modules and using a top down approach for design. For this design, only two versions of the PR module and a single static module were created. It is possible however to implement several static modules and PR modules as well as multiple versions of each PR module. The top level design and each module must be created in a separate project and synthesized separately. Note that in this design 4 bus macros were used to ease routing from the reconfigurable module to I/O ports. This will be further explained later. This creates a separate net list for each module which will be used later during budgeting and implementation. VHDL code for the top level and subsequent modules are available in Appendix A. A basic overview of this design is shown below.

Figure 4.1 - Top Level Design Hierarchy

#### 4.2.2 Design Intent

This partially reconfigurable design was developed as a proof of concept. The intent of this design was to create a partially reconfigurable circuit which is easily tested and would limit design problems. A design was chosen which would utilize only one reconfigurable and static module. A basic ALU would provide an easily testable design which could be written in a partially reconfigurable manner. In the interest of time the design was limited to only two operations, addition and subtraction. Each operation would be contained within its own reconfigurable module and a partial bit file would be loaded to the board to switch between the two. For testing purposes, a static module would control otherwise unused LEDs to test for errors during reconfiguration. Overall, this would require creation of four separate Xilinx ISE projects. The top level, static module, and PR modules would each require their own synthesis.

#### 4.2.3: Top Level