# FPGA-Based Co-processor for Singular Value Array Reconciliation Tomography

Jack Coyne

September 5, 2007

#### Abstract

This thesis describes a co-processor system that has been designed to accelerate computations associated with Singular Value Array Reconciliation Tomography (SART), a method for locating a wide-band RF source which may be positioned within an indoor environment, where RF propagation characteristics make source localization very challenging. The co-processor system is based on field programmable gate array (FPGA) technology, which offers a low-cost alternative to customized integrated circuits, while still providing the high performance, low power, and small size associated with a custom integrated solution. The system has been developed in VHDL, and implemented on a Virtex-4 SX55 FPGA development platform. The system is easy to use, and may be accessed through a C program or MATLAB script. Compared to a Pentium 4 CPU running at 3 GHz, use of the co-processor system provides a speed-up of about 6 times for the current signal matrix size of 128-by-16. Greater speed-ups may be obtained by using multiple devices in parallel. The system is capable of computing the SART metric to an accuracy of about -145 dB with respect to its true value. This level of accuracy, which is shown to be better than that obtained using single precision floating point arithmetic, allows even relatively weak signals to make a meaningful contribution to the final SART solution.

#### Acknowledgements

I would like to thank my advisor, Professor Jim Duckworth for giving me the opportunity to partake in research that is as useful, interesting, and groundbreaking as the Precision Personnel Locator project. I would like to thank all the PPL team members for making this research effort possible. Each member plays a vital role, and I am confident that the fruits of their labor will help to save the lives of many. I would like to pay my respects to emergency responders who have given their lives in the line of duty, and to those who continue to risk their own lives despite these tragedies, and despite the lack of adequate tracking technology. I would like to thank the Department of Justice for funding this project, and helping to provide the best possible safety measures for those who protect the public. Most importantly, I would like to thank my family for providing love, support, and encouragement throughout my life, and for being so understanding during the times when I have neglected all things other than this work. I dedicate this work to my grandfather, John William Wolf, who seeded my interest in engineering.

# Contents

| 1 | Intr | roduction                                   | 10 |

|---|------|---------------------------------------------|----|

|   | 1.1  | Indoor Tracking                             | 11 |

|   | 1.2  | The Precision Personnel Locator System      | 12 |

|   | 1.3  | Outline                                     | 13 |

| 2 | Sing | gular Value Array Reconciliation Tomography | 14 |

|   | 2.1  | Overview                                    | 14 |

|   | 2.2  | Signal Propagation                          | 17 |

|   | 2.3  | The SART Signal Matrix                      | 18 |

|   | 2.4  | SART Scan Rephasing                         | 19 |

|   | 2.5  | Singular Value Decomposition                | 20 |

|   |      | 2.5.1 QR Decomposition                      | 22 |

|   |      | 2.5.2 Householder Method                    | 22 |

|   |      | 2.5.3 Givens Rotations                      | 24 |

|   |      | 2.5.4 The CORDIC Algorithm                  | 27 |

|   |      | 2.5.5 Bidiagonalization                     | 28 |

|   |      | 2.5.6 Diagonalization                       | 30 |

|   | 2.6  | Quantified SART Computational Requirements  | 30 |

| 3 | Sys  | tem Platform                                | 34 |

|   | 3.1  | Field Programmable Gate Arrays              | 34 |

|   | 3.2  | Prototyping Platform                        | 35 |

|   | 3.3  | Virtex-4 FPGAs                              | 36 |

|   |      | 3.3.1 Configurable Logic Blocks             | 36 |

|   |      | 3.3.2 Digital Signal Processing Blocks      | 38 |

|   |      | 3.3.3 Block RAM                                        | 39         |

|---|------|--------------------------------------------------------|------------|

|   |      | 3.3.4 Resource Availability Constraints                | 39         |

| 4 | SAF  | RT Co-processor Architecture                           | 41         |

|   | 4.1  | Design Approach                                        | 41         |

|   | 4.2  | Algorithm Partitioning                                 | 42         |

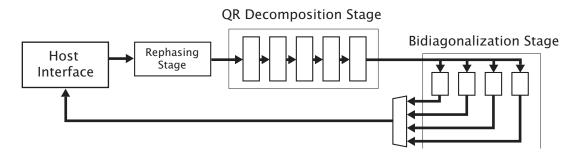

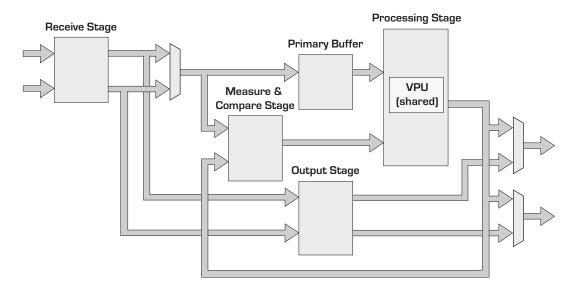

|   | 4.3  | Top-Level Architecture                                 | 44         |

|   | 4.4  | Fundamental Operations                                 | 45         |

|   | 4.5  | Vector Processing Unit                                 | 46         |

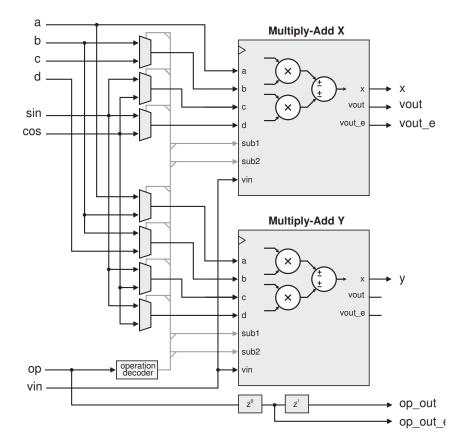

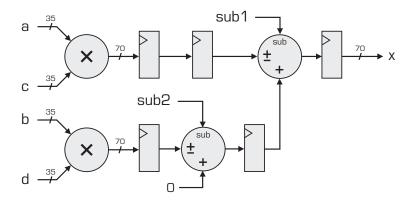

|   |      | 4.5.1 Multiply-Add Module                              | 48         |

|   | 4.6  | CORDIC Module                                          | 53         |

|   |      | 4.6.1 Implementation Considerations                    | 54         |

|   |      | 4.6.2 CORDIC Implementation                            | 56         |

|   | 4.7  | Host Interface                                         | 61         |

|   | 4.8  | Rephasing Stage                                        | 61         |

|   |      | 4.8.1 Rephasing Matrix Compression                     | 62         |

|   |      | 4.8.2 Input Interface                                  | 63         |

|   |      | 4.8.3 Rephasing Matrix Decompression and Application   | 63         |

|   | 4.9  | QR Decomposition Stage                                 | 65         |

|   |      | 4.9.1 Algorithm                                        | 67         |

|   |      | 4.9.2 Processing Element Architecture                  | 68         |

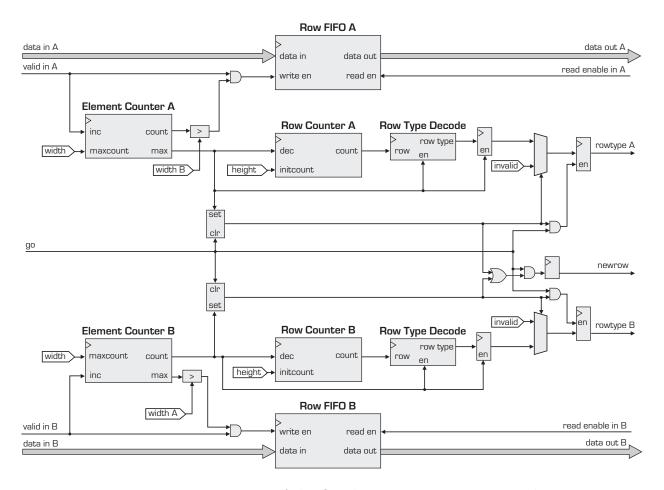

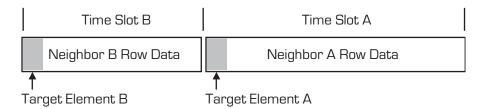

|   |      | 4.9.3 Receive stage                                    | 71         |

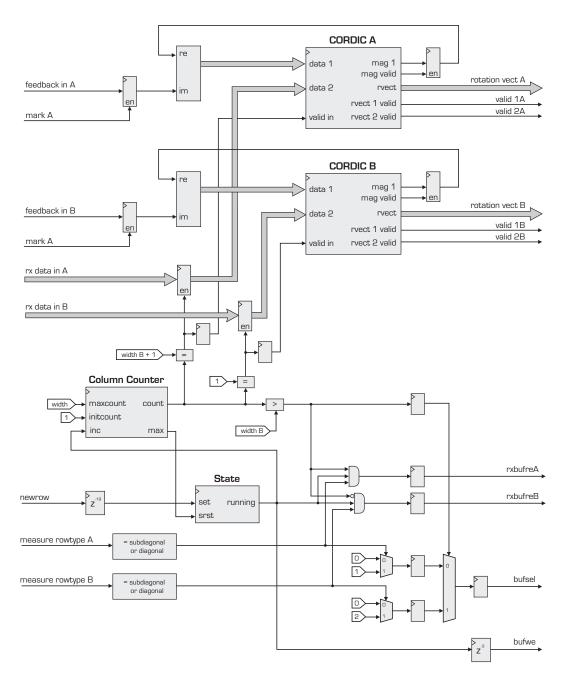

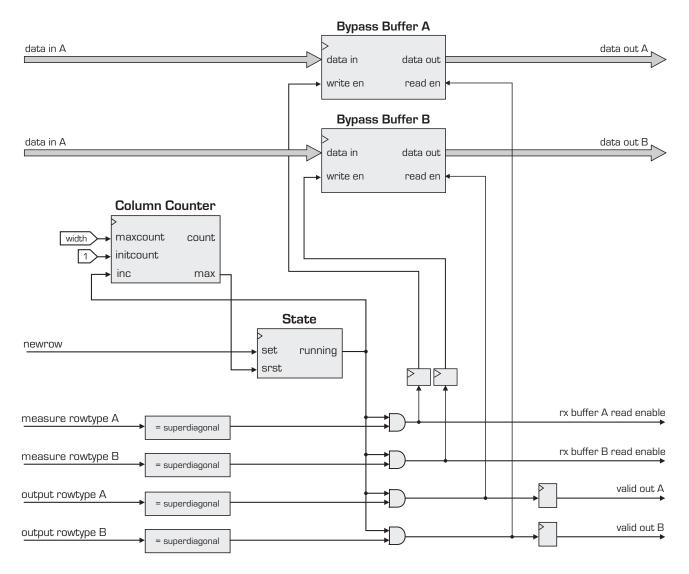

|   |      | 4.9.4 Measure and Compare stage (CORDIC stage)         | 73         |

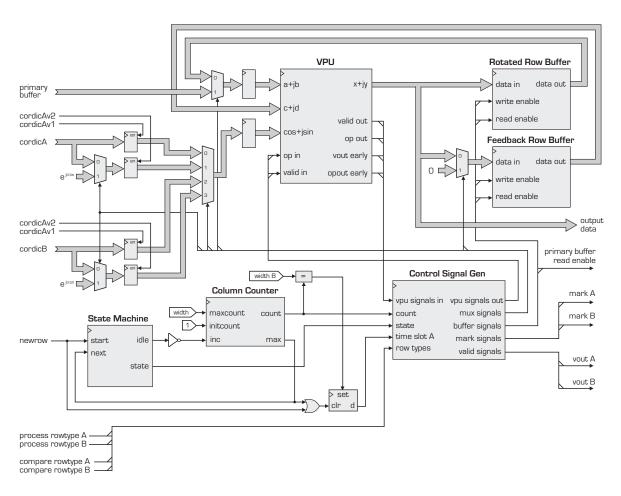

|   |      | 4.9.5 Processing stage (VPU stage)                     | <b>7</b> 5 |

|   |      | 4.9.6 Output Stage                                     | 78         |

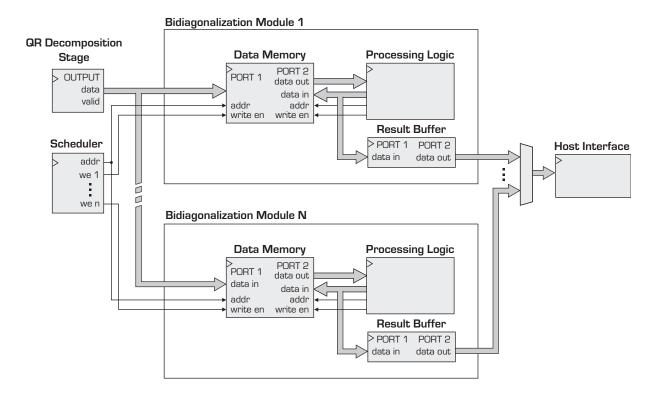

|   | 4.10 | Bidiagonalization Stage                                | 80         |

|   |      |                                                        | 82         |

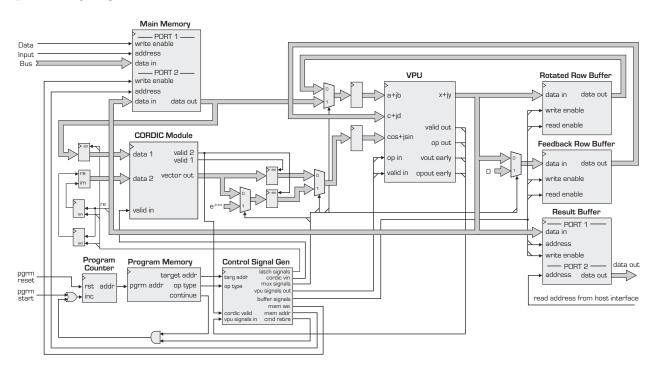

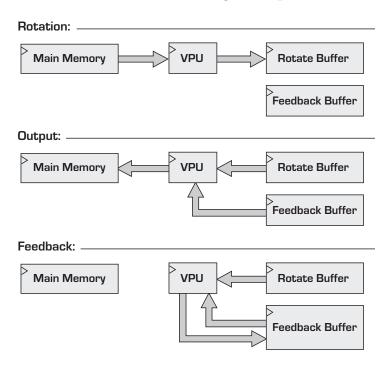

|   |      | 4.10.2 Bidiagonalization Module Architecture           | 83         |

|   |      | 4.10.3 Processing Program and Command Sequencing Macro | 84         |

| 5 | Ope  | ration 8                                               | 87         |

|   | 5.1  |                                                        | 87         |

|   | 5.2  |                                                        | 88         |

|   | 5.3  |                                                        | 89         |

|   | 5.4  |                                                        | 90         |

|   | 5.5  | Diagoi | nalization              | 92  |

|---|------|--------|-------------------------|-----|

| 6 | Peri | formar | nce                     | 93  |

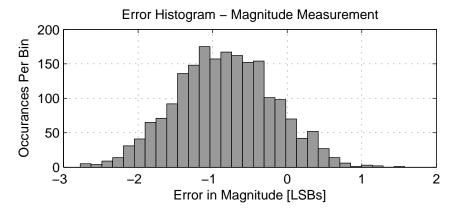

|   | 6.1  | Accura | acy                     | 94  |

|   |      | 6.1.1  | Vector Processing Unit  | 94  |

|   |      | 6.1.2  | CORDIC Module           | 97  |

|   |      | 6.1.3  | Rephasing               | 100 |

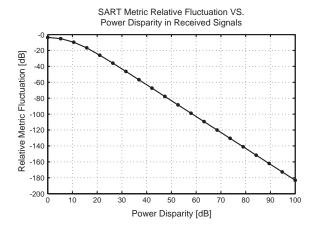

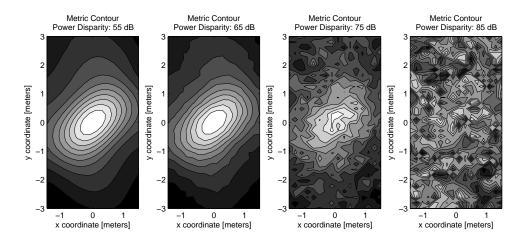

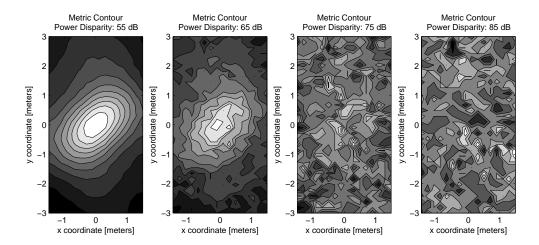

|   |      | 6.1.4  | SART Metric Solution    | 101 |

|   | 6.2  | Speed  | up                      | 108 |

|   |      | 6.2.1  | Vector Processing Unit  | 108 |

|   |      | 6.2.2  | CORDIC Module           | 108 |

|   |      | 6.2.3  | QR Decomposition Stage  | 108 |

|   |      | 6.2.4  | Bidiagonalization Stage | 110 |

| _ | ~    |        |                         |     |

| 7 | Con  | clusio | n                       | 111 |

|   | 7.1  | Future | e Work                  | 112 |

# List of Tables

| 1   | List of acronyms used in this document                      | 9   |

|-----|-------------------------------------------------------------|-----|

| 2.1 | Operation and data output counts for SART processing stages | 32  |

| 3.1 | Available Resources in Virtex-4 Family FPGAs                | 40  |

| 4.1 | Address ranges for various memory mapped system elements    | 61  |

| 5.1 | Memory layout: scan-grid rephasing matrices                 | 88  |

| 5.2 | Memory layout: signal matrix data                           | 89  |

| 5.3 | Control and status register layout                          | 90  |

| 5.4 | Memory layout: result buffer addresses                      | 91  |

| 6.1 | SART metric accuracy: RMS error, test one                   | 102 |

| 6.2 | SART metric accuracy: relative error (dB), test one         | 102 |

| 6.3 | SART metric accuracy: error standard deviation, test one    | 102 |

| 6.4 | SART metric accuracy: RMS error, test one                   | 103 |

| 6.5 | SART metric accuracy: relative error (dB), test two         | 103 |

| 6.6 | SART metric accuracy: error standard deviation, test two    | 104 |

# List of Figures

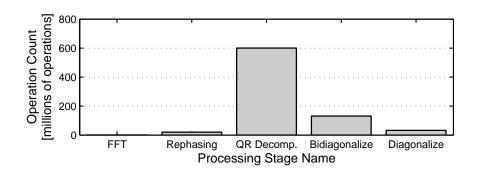

| 2.1  | Operation count graph for SART processing stages                        | 32 |

|------|-------------------------------------------------------------------------|----|

| 2.2  | Data count graph for SART processing stages                             | 32 |

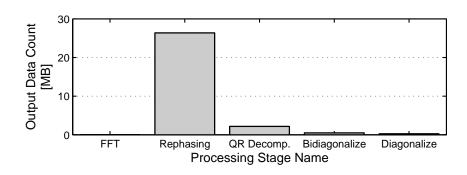

| 3.1  | Diagram of prototyping platform                                         | 36 |

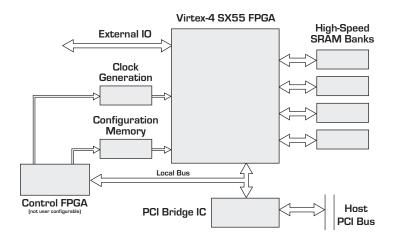

| 3.2  | Structure of FPGA configurable logic block (CLB)                        | 37 |

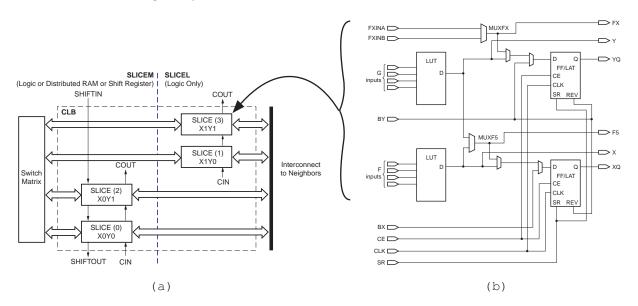

| 3.3  | Structure of FPGA arithmetic (DSP) block                                | 38 |

| 4.1  | Top-level diagram of the SART co-processor system                       | 44 |

| 4.2  | Top-level diagram of vector processing unit (VPU)                       | 48 |

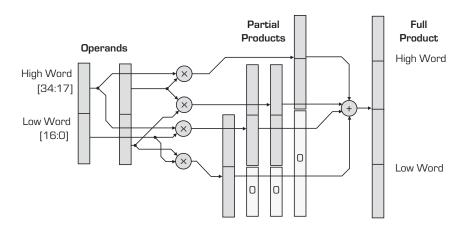

| 4.3  | Parallel sum of products                                                | 49 |

| 4.4  | 35-bit multiplication by sum of 18-bit partial products                 | 50 |

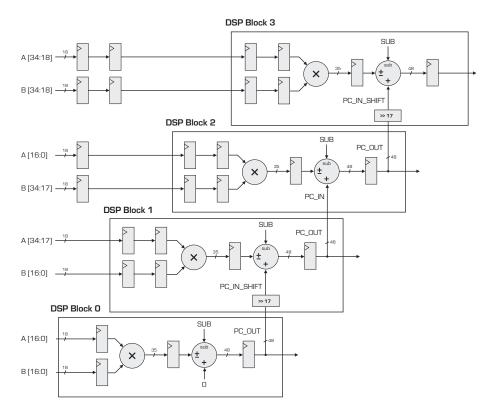

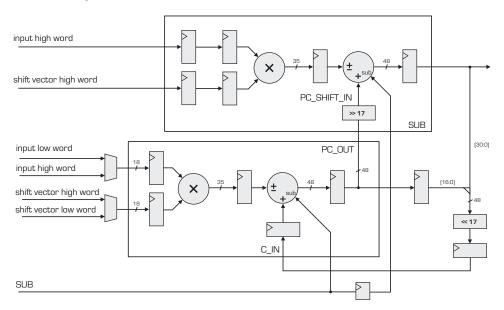

| 4.5  | 35-bit multiplication mapped to four DSP blocks                         | 51 |

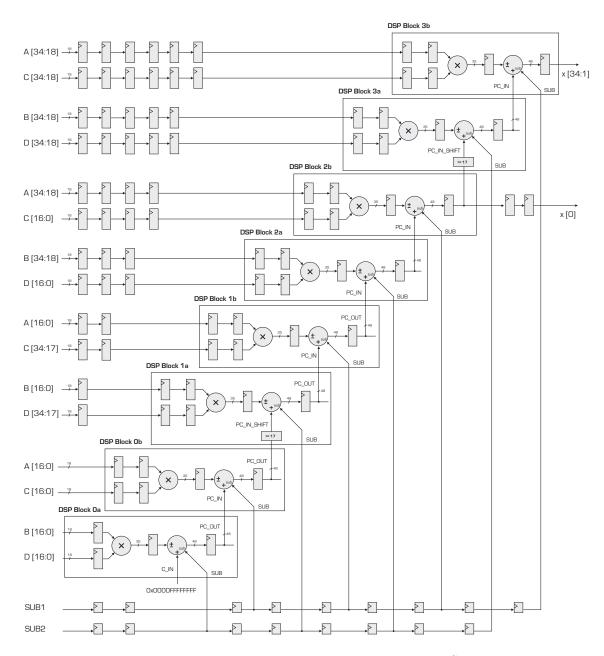

| 4.6  | 35-bit multiply-add mapped to eight DSP blocks                          | 52 |

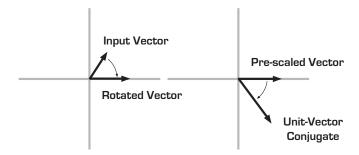

| 4.7  | Generation of a unit vector using coordinated CORDIC rotations          | 54 |

| 4.8  | Resource consumption of Xilinx IP CORDIC module                         | 55 |

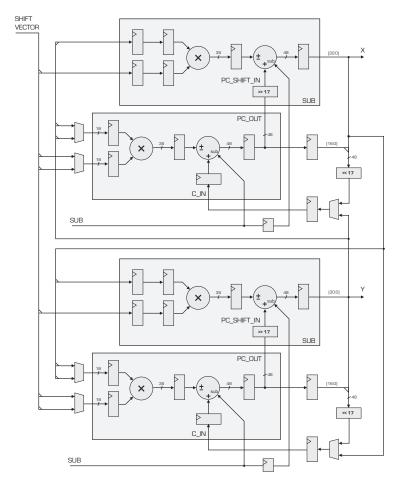

| 4.9  | CORDIC shift-accumulate operation implemented using two DSP blocks      | 56 |

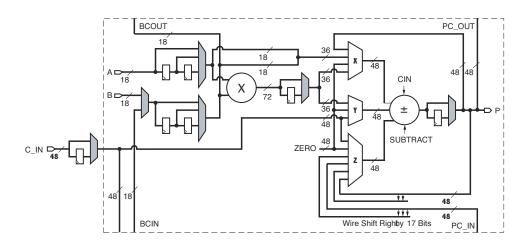

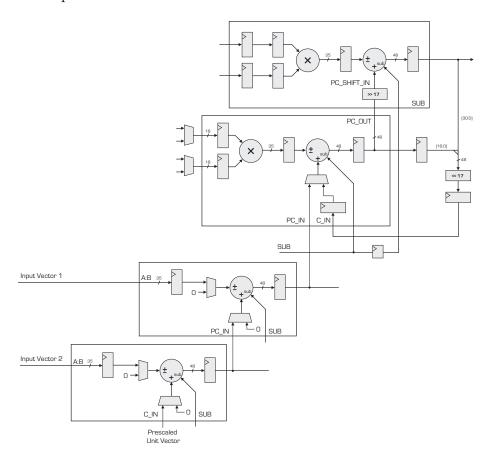

| 4.10 | CORDIC rotation circuit implemented using two shift-accumulate circuits | 57 |

| 4.11 | CORDIC module input multiplexing                                        | 58 |

| 4.12 | Resource consumption of custom CORDIC module                            | 59 |

| 4.13 | Processing schedule for CORDIC module                                   | 60 |

| 4.14 | Rephasing stage input interface                                         | 64 |

| 4.15 | Rephasing stage decompression and application circuit                   | 65 |

| 4.16 | QR decomposition stage: resource sharing                                | 68 |

| 4.17 | QR decomposition stage: processing element top-level                    | 70 |

| 4.18 | QR decomposition processing element: processing schedule                | 70 |

| 4 19 | OR decomposition processing element: Receive stage                      | 72 |

| 4.20 | QR decomposition processing element: Measure and compare stage     | 74  |

|------|--------------------------------------------------------------------|-----|

| 4.21 | QR decomposition processing element: Processing stage              | 76  |

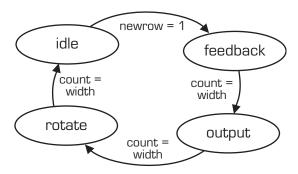

| 4.22 | Processing stage state-flow diagram                                | 77  |

| 4.23 | Processing stage resource sharing schedule                         | 77  |

| 4.24 | QR decomposition processing element: Output stage                  | 79  |

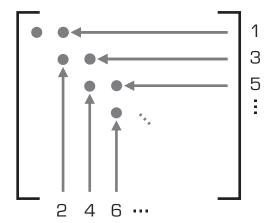

| 4.25 | Bidiagonalization reduction-operation ordering                     | 80  |

| 4.26 | Bidiagonalization module processing schedule                       | 81  |

| 4.27 | Bidiagonalization stage: Top-level                                 | 82  |

| 4.28 | Bidiagonalization module                                           | 83  |

| 4.29 | Bidiagonalization module: Data flow diagram                        | 84  |

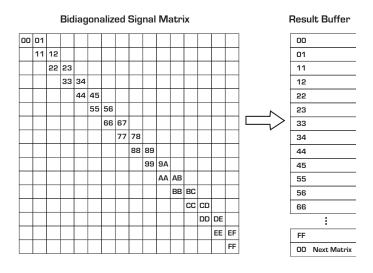

| 5.1  | Mapping of bidiagonalized matrix into the result buffer            | 91  |

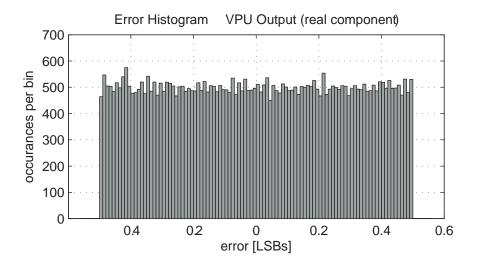

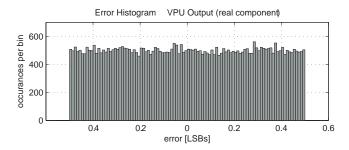

| 6.1  | VPU accuracy: rotate operation, real component                     | 95  |

| 6.2  | VPU accuracy: rotate operation, imaginary component                | 95  |

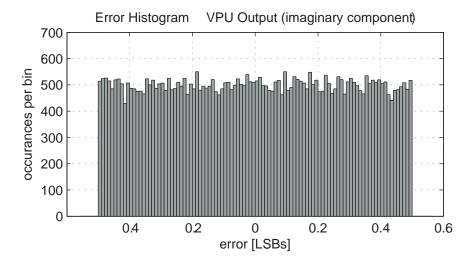

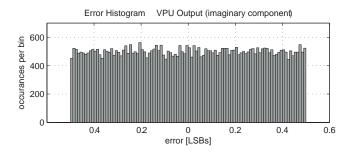

| 6.3  | VPU accuracy: output operation, real component                     | 96  |

| 6.4  | VPU accuracy: output operation, imaginary component                | 96  |

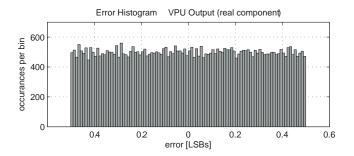

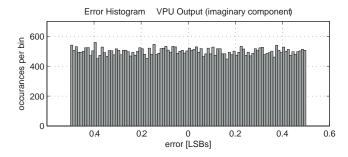

| 6.5  | VPU accuracy: feedback operation, real component                   | 96  |

| 6.6  | VPU accuracy: feedback operation, imaginary component              | 96  |

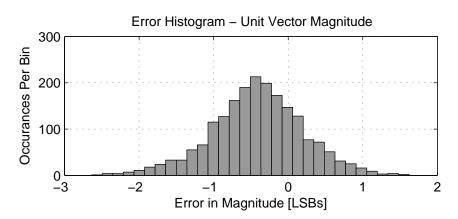

| 6.7  | CORDIC accuracy: unit vector magnitudes                            | 98  |

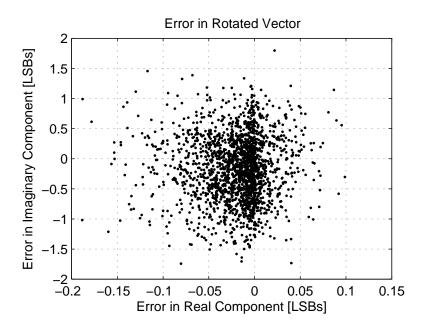

| 6.8  | CORDIC accuracy: vector rotation                                   | 99  |

| 6.9  | CORDIC accuracy: vector magitudes                                  | 99  |

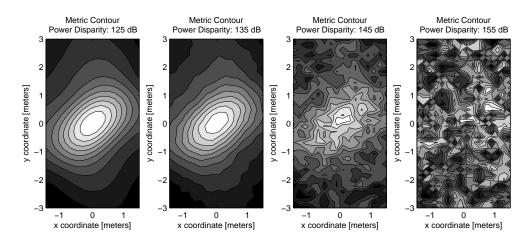

| 6.10 | Effect of power disparity on metric value relative fluctuation     | 105 |

| 6.11 | SART metric accuracy: power disparity test, using co-processor     | 106 |

| 6.12 | SART metric accuracy: power disparity test, using single precision | 106 |

| 6.13 | SART metric accuracy: power disparity test, using double precision | 107 |

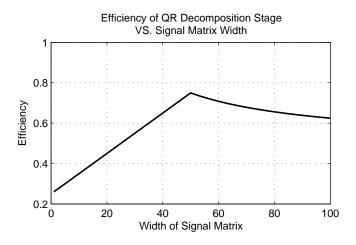

| 6.14 | Efficiency curve for QR decomposition stage                        | 109 |

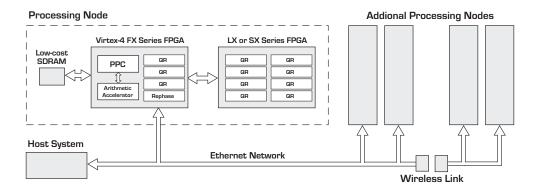

| 7.1  | Next-generation SART processing system                             | 114 |

Table 1: List of acronyms used in this document

| Table 1: List of acronyms used in this document |                                                |  |  |

|-------------------------------------------------|------------------------------------------------|--|--|

| ADC Analog to Digital Converter                 |                                                |  |  |

| ASIC                                            | Application Specific Integrated Circuit        |  |  |

| BRAM                                            | Block RAM                                      |  |  |

| CLB                                             | Configurable Logic Block                       |  |  |

| CORDIC                                          | Coordinate Rotation Digital Computer           |  |  |

| CPU                                             | Central Processing Unit                        |  |  |

| DAC                                             | Digital to Analog Converter                    |  |  |

| DFT                                             | Discrete Fourier Transform                     |  |  |

| DSP                                             | Digital Signal Processing                      |  |  |

| FFT                                             | Fast Fourier Transform                         |  |  |

| FIFO                                            | First-In First-Out memory structure            |  |  |

| FPGA                                            | Field Programmable Gate Array                  |  |  |

| LSB                                             | Least Significant Bit                          |  |  |

| MAC                                             | Media Access Controller                        |  |  |

| PC                                              | Personal Computer                              |  |  |

| PCI                                             | The Peripheral Component Interconnect          |  |  |

| PPL                                             | The WPI Precision Personnel Locator project    |  |  |

| RAM                                             | Random Access Memory                           |  |  |

| RF                                              | Radio Frequency                                |  |  |

| RMS                                             | Root Mean Square                               |  |  |

| SART                                            | Singular Value Array Reconciliation Tomography |  |  |

| SDRAM                                           | Synchronous Dynamic RAM                        |  |  |

| SRAM                                            | Synchronous RAM                                |  |  |

| SVD                                             | Singular Value Decomposition                   |  |  |

| SX55                                            | A specific FPGA device sold by Xilinx Inc.     |  |  |

| VHDL                                            | VHSIC Hardware Description Language            |  |  |

| VHSIC                                           | Very High Speed Integrated Circuit             |  |  |

| VPU                                             | Vector Processing Unit                         |  |  |

| WPI                                             | Worcester Polytechnic Institute                |  |  |

# Chapter 1

### Introduction

The ability to track the locations of personnel deployed within a building is desirable in many situations, especially those wherein individuals may become lost or debilitated and require assistance in egress. In an emergency first-response situation, rescue operations often must be carried out within a very short time frame. This is particularly true during fire fighting missions, when a person in need of assistance will almost certainly be located in an environment without breathable air, where temperatures can exceed 300 degrees Celsius, and where the integrity of the surrounding structure is deteriorating rapidly. These factors can reduce the time available for rescue to just minutes. Tracking must therefore occur in real time, with location updates occurring at least every second, regardless of the size of the structure. Furthermore, location estimates must be very accurate such that, for example, a person under egress assistance may be guided to the correct door when presented with many adjacent avenues, and subject to zero-visibility conditions. Obtaining this level of accuracy has been the goal of many efforts world wide, and is the main objective of the project for which this work serves as a component. The goal of this particular component is to obtain the aforementioned real-time performance despite the computational complexity of the proposed location estimation algorithm.

### 1.1 Indoor Tracking

Tracking of personnel located within a building using a system that requires no preexisting infrastructure is a goal that has been addressed by research teams from academic, government, and commercial institutions all over the world [1] [2] [3] [4] [5]. Despite these efforts and the millions of dollars invested, no system with the required accuracy, reliability, and affordability has been demonstrated, let alone brought to market. Many tracking techniques have been investigated, but the two most promising are radio-based tracking and inertial navigation.

Radio based systems attempt to extract time-of-flight information from radio signals that have propagated through a building, from the object being tracked to externally located reference units, or visa versa. The major challenge posed by this technique results from the fact that radio-frequency electromagnetic waves are reflected and diffracted by metallic structural members and metallic objects within the building. These phenomena result in a received signal that can be defined as the sum of the direct-path component and the reflected, "multi-path", components. Solving for the range to the object being tracked requires isolating the direct-path component. Separating this component from the undesired portion of the received signal is not a trivial task and presents the most significant challenge to research teams developing radio-based location systems [5].

Inertial navigation systems rely on sensors capable of measuring linear and rotational acceleration in order to determine velocity and position. The adoption of this technique is inhibited mainly by the cost of a functional system, as well as regulations that control the availability of high-precision sensors. Affordable inertial sensors do not have the accuracy required for long-duration tracking. Small amounts of bias and drift in the outputs of these sensors lead to the accumulation of large errors as these outputs are integrated over time to obtain the final position estimate [4]. Highly accurate sensors are not only larger and more expensive, but they are also subject to export restrictions imposed by the government due to their suitability to weapons applications, such as missile guidance systems [6].

### 1.2 The Precision Personnel Locator System

The Worcester Polytechnic Institute Precision Personnel Location (PPL) project began in December, 1999, prompted by the tragic loss of six firefighters in the Worcester Cold Storage Warehouse fire. The deaths of these men have been attributed in part to the inability to determine their locations within the burning structure [7]. The goal of the PPL project is to develop a system capable of providing sub-meter accuracy in the location and tracking of personnel situated within hazardous indoor environments. The system is primarily radio-based due to the limitations of available inertial sensors, and requires no pre-existing infrastructure so that it may be used in any location [8].

Over a dozen faculty and student team members, participating in seven years of research efforts, have produced four generations of prototype hardware, and many more generations and refinements of the signal processing algorithms developed for estimating location using the received radio signals. The performance of the system has matured from coarse outdoor tracking using 15 MHz of bandwidth [9], to a 150 MHz system that enables indoor tracking with errors on the order of one meter [8]. In early 2006 it was apparent that the final project goal was within reach, and the time came to consider the deployment of the system, and how this would be made feasible.

One of the most evident obstacles on the path towards deployment was the burden imposed by the computational complexity of the position estimation algorithm, known as Singular Value Array Reconciliation Tomography (SART). The amount of computation associated with the SART algorithm is so great that scanning a 20m by 20m room for a single target takes approximately 1 second using a Pentium 4 CPU running at 3GHz. Using this figure, and assuming that a structure consists of many rooms and many floors, and that there could potentially be dozens of personnel that need to be located or tracked, a complete scan could easily take many minutes.

Acceleration of the SART algorithm could be accomplished using a cluster of PCs working in parallel, but this solution would be physically too large for a mobile application, and needlessly power hungry. A smaller more efficient solution would be one that uses custom hardware instead of the generalized architecture of a personal computer. For customizable high-speed signal processing, Field Programmable Gate Arrays (FPGAs) are the industry

standard hardware. They are second in performance only to Application Specific Integrated Circuits (ASIC), which can easily cost millions dollars to design and test, yet FPGAs cost only a few thousand dollars [10]. An FPGA-based system was chosen as the platform for the SART accelerator system described here.

#### 1.3 Outline

This thesis begins with the presentation of the SART technique for indoor tracking in Chapter 2. The algorithm is broken into stages so that it may be easily partitioned into tasks that are appropriate for hardware and software implementation. The number of computations involved in each stage are quantified to motivate the need for hardware-based acceleration, and provide a basis for intelligent partitioning decisions. The FPGA development platform, which was used for prototyping, is described in Chapter 3. An overview of FPGA technology and the architectural details of the selected FPGA are presented, along with some important architecture related design considerations. The implementation of the SART co-processor system is presented in Chapter 4. Chapter 5 contains a description of how the SART co-processor system is operated. In Chapter 6, the performance of the SART co-processor system is analyzed in terms of accuracy, and speedup. The final chapter presents conclusions, and avenues for future work.

# Chapter 2

# Singular Value Array Reconciliation Tomography

This chapter contains a description of a new technique for radio-based indoor location. The technique was developed at WPI for the purpose of tracking first-response personnel such as firefighters. An overview of the technique is presented first. Later sections provide a more detailed description of the algorithm, and quantify the number of computations associated with each processing stage.

#### 2.1 Overview

Singular value Array Reconciliation Tomography (SART) [11] is a source localization technique developed as part of the PPL project. The SART algorithm was developed as a means for locating the origin of a wide-band multi-tone signal using a receiver array with arbitrary recieve-element geometry. The performance of the SART technique is described only briefly here, because ultimately, this thesis is not concerned with why or how well SART works, but only with accomplishing it quickly. A more through explanation and performance analysis of SART can be found in documents that deal specifically with algorithm development [12].

The location process begins with the transmission of a multi-tone signal by the device that is to be located. The transmission is recorded at multiple receiving elements, which ideally surround the transmitter. For the PPL project application of SART, these receiving elements correspond to antennas located on fire-trucks and other vehicles located around the outside of a building in which personnel are being tracked. The received signals are digitized using an analog to digital converter and stored in memory so that they may be used as inputs to the SART algorithm. The remaining inputs to the algorithm are the relative coordinates of the receive elements, which are assumed to be known.

The SART algorithm is an imaging technique (hence the use of the term tomography). Given the algorithm inputs at any given instance, the physical area of interest is scanned at regular spatial intervals, where it is assessed in terms of the SART metric. This set of scan locations is known as the scan-grid. The location of maximum metric value indicates the estimated location of the transmitter. Scanning is accomplished by applying negative time delays to the received signals. These delays corresponding to the light-speed travel time between the current scan location and each receive element. Because the locations of the receive elements are known, these time delays can be easily calculated for each location on the scan-grid. Time delay application is accomplished by imposing a linear (with frequency) phase shift to the signals from each receive element.

If the exact location of the transmitter is scanned, then the application of the negative time delays will counter-act the actual time delays associated with the propagation of the multitone signal from the transmitter to the receive elements. The result of this will be temporal alignment of all of the received signals, thereby maximizing their linear dependence in the ideal, zero multi-path case. For this reason, the imaging metric chosen for SART is the level of linear dependence between the rephased signals. The level of linear dependence is measured by assigning each rephased input signal to a different column in a matrix, performing singular value decomposition of that matrix, and observing the first singular value [12].

Using the process of Singular Value Decomposition (SVD), any matrix can be broken down into a set of unitary column and row vectors, and a corresponding set of scalar values. These components contain all of the information necessary to reconstruct the original matrix. The singular vectors serve as an orthonormal basis for the matrix, while the singular values contain information about the amplitudes of these vectors in their role as components within the original matrix. Together, the singular values provide an indication of matrix rank [13].

For example, if a matrix is composed of multiple linearly dependent columns (or rows), then the matrix is said to have a rank of one (i.e. all but the first singular value will be zero). If there are small dissimilarities between columns then the SVD will reveal more non-zero singular values, with magnitudes corresponding to the amplitudes of the components that impart these dissimilarities. Larger dissimilarities will be reflected in larger rank supporting singular values.

If dissimilarities arise due to the application of linear phase, as they do in the SART scanning procedure, then the increase in the lesser singular values occurs with a corresponding decrease in the first (largest) singular value. This is because the Frobenius norm of a matrix (which can be calculated as the square-root of the sum of the squares of all the singular values) is maintained during such an operation [12]. Leveraging this property of singular values, the SART algorithm uses singular value decomposition to obtain a measure of linear dependence between columns of the signal matrix in the form of the first singular value.

In SART, the assumption is that each receive element will see the direct-path component of the transmitted signal and various multi-path components. The hope is that different receive elements will collect multi-path components that are of lower linearly dependence and/or amplitude than the collected direct-path components, when analyzed according to the scanning procedure. If this assumption holds, then the SART metric will be maximized in the region of the transmitter. Many rounds of simulation and live testing have been conducted, producing good results that have verified the validity of the SART method [12]. The major disadvantage of the SART algorithm is its computational complexity, most of which arises due to the application of the SVD.

The following sections provide a detailed description of the SART algorithm in an attempt to reveal the large computational burden it presents, and partition it into a manageable set of tasks. This will serve to motivate and outline the work described in this document, which represents an effort to accelerate this algorithm using custom digital signal processing hardware. The description will include an enumeration of the singular value decomposition process because it represents a substantial portion of SARTs computational complexity, and because (as will be revealed in later sections) the partitioning of the algorithm between the accelerator and the host PC was chosen such that the SVD is computed partially in each partition.

### 2.2 Signal Propagation

As mentioned in the SART overview section, any person being tracked using the PPL system must wear a radio transmitter that broadcasts a multi-tone signal. The signal is generated in baseband by playing a predefined waveform through a digital-to-analog converter (DAC), upconverted to radio frequency (RF), and then filtered to obtain a single side-band transmission of the form

$$s(t) = \sum_{i=1}^{m} e^{j(2\pi f_i t + \theta_i)}$$

(2.1)

where  $f_i$  and  $\theta_i$  represent the frequency and initial phase of the  $i^{th}$  RF tone (or subcarrier).

The RF signal propagates from the transmitter, through the building, to each of the receivers. The travel-time associated with propagation can be calculated from the distance of travel and the speed of light in the propagation medium. Assuming the propagation occurs primarily in air, the propagation velocity may be approximated with the propagation velocity in a vacuum, 299,792,458 meters per second. If multi-path components are ignored, then the received signal is identical to the transmitted signal, but delayed by the travel-time. The signal received at a distance, d, from the transmitter can be represented as

$$s(t) = \sum_{i=1}^{m} e^{j(2\pi f_i(t - \frac{d}{c}) + \theta_i)}$$

(2.2)

where c is the speed of propagation.

At each receive element the received signal is down-converted to baseband, digitized using an analog-to-digital converter (ADC), and stored for processing. This is where the application of the SART algorithm begins.

#### 2.3 The SART Signal Matrix

The first step in the SART algorithm is to obtain the frequency-domain representation of the received signal. This allows the sub-carrier tones to be isolated from each other, and from noise components at other frequencies. The conversion is accomplished using the Discrete Fourier Transform (DFT), implemented using the Fast Fourier Transform (FFT) algorithm. The sub-carrier tones are placed at even intervals, which coincide with the frequency bins of the transform. This prevents leakage of the sub-carrier energy into adjacent frequency bins [12]. The output of the FFT is an array of complex values that represent the amplitudes and phases of the frequency components that comprise the input time-domain signal. The values that correspond to the transmitted sub-carrier frequencies are saved. Values from other frequency bins represent noise and interfering signals and are therefore discarded.

The transmitted signal can be represented as an array of complex values that encode the magnitude and phase each of the sub-carrier tones. Each received signal can be represented as this same signal with the application of a time delay associated with propagation. In the frequency domain, this time delay appears in the form of a phase shift that decreases linearly with frequency. If the transmitted signal is represented in the form

$$S = \left[ \begin{array}{ccccc} s_1 & s_2 & s_3 & \dots & s_m \end{array} \right] \tag{2.3}$$

where m equals the number of sub-carrier tones, and  $s_i$  encodes the arbitrary phase of the transmitted signal for the  $i^{th}$  sub-carrier, then the received signal at a distance, d, from the transmitter can be represented as

$$S = \begin{bmatrix} s_1 e^{-j2\pi\Delta f \frac{d}{c}} & s_2 e^{-j4\pi\Delta f \frac{d}{c}} & s_3 e^{-j6\pi\Delta f \frac{d}{c}} & \dots & s_m e^{-j2m\pi\Delta f \frac{d}{c}} \end{bmatrix}$$

(2.4)

where  $\Delta f$  represents the frequency spacing between sub-carrier tones (and for convenience the frequency of the first tone), and the exponential factors encode the frequency-dependent phase shift undergone by each of the m sub-carriers due to propagation delay. Since there are many receivers, each at a different distance from the transmitter, the group of received signals can be formed into a matrix, with each column representing the signal recorded at one receive element. The SART signal matrix has the form

$$\mathbf{S} = \begin{bmatrix} s_{1}e^{-j2\pi\Delta f\frac{d_{1}}{c}} & s_{1}e^{-j2\pi\Delta f\frac{d_{2}}{c}} & \cdots & s_{1}e^{-j2\pi\Delta f\frac{d_{n}}{c}} \\ s_{2}e^{-j4\pi\Delta f\frac{d_{1}}{c}} & s_{2}e^{-j4\pi\Delta f\frac{d_{2}}{c}} & \cdots & s_{2}e^{-j4\pi\Delta f\frac{d_{n}}{c}} \\ s_{3}e^{-j6\pi\Delta f\frac{d_{1}}{c}} & s_{3}e^{-j6\pi\Delta f\frac{d_{2}}{c}} & \cdots & s_{3}e^{-j6\pi\Delta f\frac{d_{n}}{c}} \\ \vdots & \vdots & \ddots & \vdots \\ s_{m}e^{-j2m\pi\Delta f\frac{d_{1}}{c}} & s_{m}e^{-j2m\pi\Delta f\frac{d_{2}}{c}} & \cdots & s_{m}e^{-j2m\pi\Delta f\frac{d_{n}}{c}} \end{bmatrix}$$

$$(2.5)$$

where  $d_k$  represents the distance from the transmitter to the  $k^{th}$  receiver. It is this signal matrix that is rephrased according to the scan-grid and evaluated in terms of the SART metric.

### 2.4 SART Scan Rephasing

After the signal matrix has been constructed, the SART scanning procedure begins. It is this exhaustive imaging approach that leads to the immense number of computations required to produce a single location estimate. The spatial resolution, or density, of the scan-grid is chosen based on bandwidth [12], and is typically 0.25 to 0.5 meters for the current 150 MHz implementation. Therefore, even a modest 20m-by-20m-by-20m volume will contain 8000 scan locations. As a more realistic example, a standard street block in the Manhattan has a footprint of about 80m-by-270m, and assuming a modest height of about 25m, this volume would contain over 500,000 scan locations. It is true that the number of locations being scanned can be reduced if the previous location of a target is known, and only the surrounding region is searched. However, the number of scan locations will remain high when tracking dozens of independent targets, and will grow larger when using the higher bandwidths needed for better accuracy.

Scanning is accomplished by applying a linear phase shift to each column of the signal matrix. The phase slope is calculated according to the propagation delay between the receiver corresponding to that column and the current scan location. This delay is easily obtained, if the geometry of the receivers is known, by calculating the Euclidean distance between the receiver and the scan location and then dividing by the speed of propagation. Using the

received signal matrix form from (2.5), the rephrased signal matrix has the form:

$$\mathbf{S} = \begin{bmatrix} s_{1}e^{-j2\pi\Delta f\frac{d_{1}}{c}}e^{j2\pi\Delta f\frac{d_{s_{1}}}{c}} & s_{1}e^{-j2\pi\Delta f\frac{d_{2}}{c}}e^{j2\pi\Delta f\frac{d_{s_{2}}}{c}} & \cdots & s_{1}e^{-j2\pi\Delta f\frac{d_{n}}{c}}e^{j2\pi\Delta f\frac{d_{s_{n}}}{c}} \\ s_{2}e^{-j4\pi\Delta f\frac{d_{1}}{c}}e^{j4\pi\Delta f\frac{d_{s_{1}}}{c}} & s_{2}e^{-j4\pi\Delta f\frac{d_{2}}{c}}e^{j4\pi\Delta f\frac{d_{s_{2}}}{c}} & \cdots & s_{2}e^{-j4\pi\Delta f\frac{d_{n}}{c}}e^{j4\pi\Delta f\frac{d_{s_{n}}}{c}} \\ s_{3}e^{-j6\pi\Delta f\frac{d_{1}}{c}}e^{j6\pi\Delta f\frac{d_{s_{1}}}{c}} & s_{3}e^{-j6\pi\Delta f\frac{d_{2}}{c}}e^{j6\pi\Delta f\frac{d_{2}}{c}} & \cdots & s_{3}e^{-j6\pi\Delta f\frac{d_{n}}{c}}e^{j6\pi\Delta f\frac{d_{s_{n}}}{c}} \\ \vdots & \vdots & \ddots & \vdots \\ s_{m}e^{-j2m\pi\Delta f\frac{d_{1}}{c}}e^{j2m\pi\Delta f\frac{d_{s_{1}}}{c}} & s_{m}e^{-j2m\pi\Delta f\frac{d_{2}}{c}}e^{j2m\pi\Delta f\frac{d_{s_{2}}}{c}} & \cdots & s_{m}e^{-j2m\pi\Delta f\frac{d_{n}}{c}}e^{j2m\pi\Delta f\frac{d_{s_{n}}}{c}} \end{bmatrix} (2.6)$$

where  $d_{sk}$  is the distance between receiver k and the scan location.

If the distance to the scan location equals the true distance between a receiver and the transmitter (i.e.  $d_{sk} = d_k$ ), then the two exponential factors will cancel for that receiver. Furthermore, if the true location of the transmitter is scanned, then cancellation will happen for all receivers. In this case, the columns of the rephrased signal matrix will become identical, apart from any multi-path or noise components. Ideally, this will lead to a maximization of the first singular value at the scan location corresponding to the true location of the transmitter.

### 2.5 Singular Value Decomposition

Through the process of singular value decomposition, a matrix,  $\mathbf{A}$ , is broken-down into two orthonormal matrices,  $\mathbf{U}$  and  $\mathbf{V}$ , and a diagonal matrix  $\mathbf{\Sigma}$ , such that

$$\mathbf{U}\mathbf{\Sigma}\mathbf{V}^H = \mathbf{A}$$

where  $\mathbf{V}^H$  indicates the complex conjugate transpose of  $\mathbf{V}$ .

The columns of  $\mathbf{U}$  and  $\mathbf{V}$  contain the left and right singular vectors for  $\mathbf{A}$ , which form an orthonormal basis for  $\mathbf{A}$ . The diagonal of  $\Sigma$  contains the singular values of  $\mathbf{A}$ , which hold magnitude or scaling information. In this way, the SVD allows  $\mathbf{A}$  to be re-expressed as a diagonal matrix through a change of basis, revealing important information about the composition of  $\mathbf{A}$  [13]. In the SART application, the singular values reveal information about the rank of the signal matrix.

The SART imaging metric is the first singular value of the rephased signal matrix. Therefore, singular value decomposition must be performed once for each location on the scan-grid. The complexity of the SVD algorithm for an m-by-n matrix is  $O(4nm^2 + 22n^3)$  operations [13], so the computational burden presented by this workload is quite large, and grows rapidly with the size of the matrix. Fortunately, because the SART algorithm requires only the singular values, and not the singular vectors, this work load can be substantially decreased to  $O(2mn^2 + 2n^3)$  operations [13]. The process of computing the singular values of a matrix is described below.

The singular values of a matrix may be obtained through the process of diagonalization, where all but the diagonal elements of the matrix are reduced to zero (or annihilated). This is typically accomplished through unitary transformations, which preserve matrix rank and the energy possessed by each linearly independent component. Most frequently, these are either Householder transformations, or Givens rotations [13]. The diagonalization process can be divided into three stages [13]:

- QR decomposition, wherein the matrix,  $\mathbf{A}$ , is factored into an orthogonal matrix,  $\mathbf{Q}$ , and an upper triangular matrix,  $\mathbf{R}$ , such that  $\mathbf{Q}\mathbf{R} = \mathbf{A}$ . The matrix  $\mathbf{R}$  retains the same singular values as  $\mathbf{A}$  while having fewer total non-zero elements.

- Bidiagonalization of the matrix **R**, such that the resulting matrix, **B**, contains non-zero values in only its diagonal elements, and the elements just above the diagonal. The singular values of **A** are still retained.

- Diagonalization of **B** is the final step of reducing the input to its diagonal form,  $\Sigma$ , in which the singular values of the original input matrix lie along the diagonal.

This is a convenient division of the process for two reasons.

- For rectangular matrices, especially where  $m \gg n$  or  $n \ll m$ , the QR decomposition stage results in a substantial reduction in the total size of the input matrix, particularly when only singular values are desired and  $\mathbf{Q}$  can be discarded. This is advantageous because it reduces the amount of computer memory needed to store the matrix elements, and eliminates needless computations during bidiagonalization.

- QR decomposition and bidiagonalization both require a deterministic number of op-

erations, which can be calculated based on the size of the input matrix. Diagonalization, on the other hand, is an iterative process which terminates based on convergence conditions. Therefore diagonalization has a non-deterministic run-time, which is influenced by the content of the matrix. Separating the deterministic stages from the non-deterministic stages is an important design consideration when partitioning the SVD process between custom parallel hardware and the sequential host CPU.

#### 2.5.1 QR Decomposition

QR decomposition is the process of factoring a matrix,  $\mathbf{A}$ , into an orthogonal matrix,  $\mathbf{Q}$ , and an upper-triangular matrix,  $\mathbf{R}$ , such that  $\mathbf{QR} = \mathbf{A}$ . When performing the decomposition in order to compute the singular values of  $\mathbf{A}$ , only  $\mathbf{R}$  is needed [13]. In this case it may be more appropriate to call the process triangularization, or unitary triangularization [14]. The term QR decomposition is maintained here because its use appears to be more widespread. Two common methods for obtaining the QR decomposition are by use of Householder reflections and by use of Givens rotations.

#### 2.5.2 Householder Method

Using a Householder transformation [14], a vector may be reflected about an arbitrary plane (in the 3-dimentional case), or hyperplane in the N-dimensional case. If this hyperplane is chosen correctly, then the resulting vector can be made to lie directly along one axis of the coordinate system, or have components along some dimensions but not others. This kind of transformation can also be applied to a matrix, where each column of the matrix corresponds to a different vector. In this case all vectors are reflected about the same hyperplane, and because the orientations of the vectors relative to each other are maintained, the singular values of the matrix will be preserved.

In order to perform QR decomposition, a group of vectors comprising a matrix may be successively reflected about a sequence of hyperplanes. The first hyperplane may be chosen such that the reflection operation causes the vector corresponding to the first column of the matrix to be aligned along the dimension corresponding to the first row of the matrix, thereby

causing all elements in the first column that lie below the first row to be annihilated. Likewise, the second Householder transformation may be chosen in a way that causes the vector in the second column to be reflected such that it has components in only two dimensions, those corresponding to the first two rows of the matrix. This process may continue until all sub-diagonal elements in the matrix are zero, and the matrix is upper-triangular [14].

In terms of implementation, the Householder method is typically considered the most efficient for implementation on a sequential processor, because it involves fewer total operations than methods using Givens rotations [15][16]. Unfortunately the algorithm involves data dependencies and other characteristics that make the method difficult to implement using parallel processing techniques [13]. Consideration of the Householder method for use in the SART co-processor system revealed two such problems that would have hindered an FPGA-based QR decomposition implementation employing this method.

The first problem lies in the fact that one reflection operation must be performed before the Householder transformation matrix for next reflection operation can be computed, thereby forcing a linear sequence of: compute Householder matrix, perform transformation, compute Householder matrix, perform transformation, et cetera. In some cases, a dependency such as this can be overcome through pipelining techniques, whereby the first transformation is applied to the input matrix while the second transformation is being applied to the previous input matrix, and the third transformation is being applied to the matrix before that, et cetera. Unfortunately there are problems with this approach towards the Householder method on an FPGA.

The main concern relates to the amount of memory available to each stage in the pipeline. That is, each stage must store the entire contents of the matrix, apart from the elements annihilated by previous stages. This may not be a problem for multiprocessor computer systems, but even in modern FPGAs, memory resources can be quite limited. The use of off-chip memory may be a solution, but this would lead to a requirement for very large IO bandwidth, which is impractical. The second flaw in the pipeline solution is a lack of balance between the loads on each stage. The nature of the Householder method is such that each stage would be required to work on a smaller matrix than the previous stage, meaning that some stages would finish their computations more quickly than other stages, and would be left idle for some time, wasting hardware resources.

Another characteristic of the Householder method that makes its implementation less practical is its requirement for the computation of square-roots and division operations when calculating vector norms, and unit vectors. While not impossible to implement on an FPGA, these operations typically involve more hardware and latency than multiplication and addition operations, and should be avoided. For the reasons outlined above, QR decomposition methods involving Givens rotations are typically preferred for parallel implementations, despite the fact that the Householder method requires fewer total operations.

#### 2.5.3 Givens Rotations

During a Givens rotation, an N-dimensional vector is rotated such that its components in only two dimensions are changed. Similar to a Householder transformation, the Givens rotation angle may be chosen such that the vector being rotated is left in an orientation where one of its components is zero, while its overall length remains unchanged. If the vector is part of a matrix, and all vectors in the matrix are rotated by the same angle, then one element of the matrix may be reduced to zero without effecting the singular values of the matrix. The Givens method for QR decomposition of a matrix involves a sequence of rotations, with each rotation eliminating one element of the matrix [15].

A Givens rotation is performed by premultiplication with a rotation matrix of the form

$$G = \begin{bmatrix} 1 & \cdots & 0 & \cdots & 0 & \cdots & 0 \\ \vdots & \ddots & \vdots & & \vdots & & \vdots \\ 0 & \cdots & \cos(\theta) & \cdots & -\sin(\theta) & \cdots & 0 \\ \vdots & & \vdots & \ddots & \vdots & & \vdots \\ 0 & \cdots & \sin(\theta) & \cdots & \cos(\theta) & \cdots & 0 \\ \vdots & & \vdots & & \vdots & \ddots & \vdots \\ 0 & \cdots & 0 & \cdots & 0 & \cdots & 1 \end{bmatrix}$$

$$(2.7)$$

Because the rotation matrix is sparse, the entire matrix multiplication need not be implemented. Instead, only the rows or columns involved in the operation are altered. For

example,

$$\begin{bmatrix} a_{11} & a_{12} & a_{13} & a_{14} \\ a'_{21} & a'_{22} & a'_{23} & a'_{24} \\ a_{31} & a_{32} & a_{33} & a_{34} \\ a'_{41} & a'_{42} & a'_{43} & a'_{44} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & \cos(\theta) & 0 & -\sin(\theta) \\ 0 & 0 & 1 & 0 \\ 0 & \sin(\theta) & 0 & \cos(\theta) \end{bmatrix} \begin{bmatrix} a_{11} & a_{12} & a_{13} & a_{14} \\ a_{21} & a_{22} & a_{23} & a_{24} \\ a_{31} & a_{32} & a_{33} & a_{34} \\ a_{41} & a_{42} & a_{43} & a_{44} \end{bmatrix}$$

(2.8)

becomes

Decomes

$$\begin{bmatrix} a'_{21} & a'_{22} & a'_{23} & a'_{24} \end{bmatrix} = \cos(\theta) \begin{bmatrix} a_{21} & a_{22} & a_{23} & a_{24} \end{bmatrix} - \sin(\theta) \begin{bmatrix} a_{41} & a_{42} & a_{43} & a_{44} \end{bmatrix}$$

$$and$$

$$\begin{bmatrix} a'_{41} & a'_{42} & a'_{43} & a'_{44} \end{bmatrix} = \cos(\theta) \begin{bmatrix} a_{41} & a_{42} & a_{43} & a_{44} \end{bmatrix} + \sin(\theta) \begin{bmatrix} a_{21} & a_{22} & a_{23} & a_{24} \end{bmatrix}$$

For the Givens rotation to eliminate  $a_{42}$ ,  $\theta$  must be chosen such that

$$\cos(\theta)a_{42} = -\sin(\theta)a_{22} \tag{2.10}$$

Therefore,

$$\theta = tan^{-1}(\frac{-a_{42}}{a_{22}}) \tag{2.11}$$

A Givens rotation may also be applied by post-multiplication with a rotation matrix. In this case, the operation involves two columns of A instead of two rows.

In the case of a matrix containing complex values, the phase of one or both rows must be adjusted such that element annihilation still occurs. For example, the previous result becomes

Decomes

$$\begin{bmatrix} a'_{21} & a'_{22} & a'_{23} & a'_{24} \end{bmatrix} = \cos(\theta)e^{-j\phi_{22}} \begin{bmatrix} a_{21} & a_{22} & a_{23} & a_{24} \end{bmatrix} - \sin(\theta)e^{-j\phi_{42}} \begin{bmatrix} a_{41} & a_{42} & a_{43} & a_{44} \end{bmatrix}$$

$$= and$$

$$\begin{bmatrix} a'_{41} & a'_{42} & a'_{43} & a'_{44} \end{bmatrix} = \cos(\theta)e^{-j\phi_{42}} \begin{bmatrix} a_{41} & a_{42} & a_{43} & a_{44} \end{bmatrix} + \sin(\theta)e^{-j\phi_{22}} \begin{bmatrix} a_{21} & a_{22} & a_{23} & a_{24} \end{bmatrix}$$

where  $\phi_{22}$  is the phase angle of  $a_{22}$  and  $\phi_{42}$  is the phase angle of  $a_{42}$ .

Order is critical when implementing the sequence of rotations. Rotations must be performed in a manner that avoids reintroducing energy into a matrix element that was reduced to zero by a previous rotation. This can be accomplished by performing the rotations starting from the left most column of the input matrix, and moving to the right only after all sub-diagonal elements in the current column have been eliminated. For example if the input matrix is

$$\mathbf{A} = \begin{bmatrix} a_{11} & a_{12} & a_{13} \\ a_{21} & a_{22} & a_{23} \\ a_{31} & a_{32} & a_{33} \end{bmatrix}$$

(2.13)

and a rotation is performed to move energy from element  $a_{31}$  to element  $a_{11}$ , then the top and bottom rows must be altered, and the result is

$$\mathbf{A} = \begin{bmatrix} a'_{11} & a'_{12} & a'_{13} \\ a_{21} & a_{22} & a_{23} \\ 0 & a'_{32} & a'_{33} \end{bmatrix}$$

(2.14)

If the next rotation attempts to move energy from element  $a'_{32}$  to element  $a'_{12}$ , then the bottom row will again be altered. In the process, energy from  $a'_{11}$  may be transferred back to the lower left element. Instead, energy from  $a_{21}$  should be transferred to element  $a'_{11}$ , in order to obtain

$$\mathbf{A} = \begin{bmatrix} a_{11}'' & a_{12}'' & a_{13}'' \\ 0 & a_{22}' & a_{23}' \\ 0 & a_{32}' & a_{33}' \end{bmatrix}$$

(2.15)

Now, energy from  $a'_{32}$  may be moved to element  $a'_{22}$ . Because the two sub-diagonal elements in the left column are both zero, there is no danger of reintroducing energy into either of them. After this rotation, the example 3-by-3 matrix will be triangular. This process may be extended to perform triangularization of larger matrices. The total number of rotations required is equal to the number of sub-diagonal elements in the matrix.

The most attractive aspect of the Givens rotation method of QR decomposition is its suitability for parallel implementation. Because only two rows or two columns of the matrix are altered during any one rotation, multiple rotations may occur in parallel provided they do not involve any of the same matrix elements. Furthermore, square-root and division operations may be avoided in a hardware implementation by employing the COordinate Rotation DIgital Computer (CORDIC) algorithm for calculating 2-D vector magnitudes, and unit-length rotation vectors.

#### 2.5.4 The CORDIC Algorithm

The COordinate Rotation DIgital Computer (CORDIC) algorithm is widely used for digital signal processing systems implemented in hardware [17]. The algorithm allows trigonometric functions to be computed without square-root or division operations. Instead, the algorithm employs a series of shift and add operations to iteratively rotate an input vector to zero, or through some arbitrary angle [18].

Consider a two-dimensional rotation of the form

$$\begin{bmatrix} a_1' \\ a_2' \end{bmatrix} = \begin{bmatrix} \cos(\theta) & -\sin(\theta) \\ \sin(\theta) & \cos(\theta) \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(2.16)

Division by  $cos(\theta)$  gives

$$\frac{1}{\cos(\theta)} \begin{bmatrix} a_1' \\ a_2' \end{bmatrix} = \begin{bmatrix} 1 & -\tan(\theta) \\ \tan(\theta) & 1 \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

(2.17)

If the rotation angle is chosen such that  $tan(\theta) = 2^{-n}$ , then multiplication by  $tan(\theta)$  can be

implemented as a binary shift, and a vector rotation becomes

$$\frac{\frac{1}{\cos(a\tan(2^{-n}))}a'_1 = a_1 \mp a_2(2^{-n})$$

$$and$$

$$\frac{1}{\cos(a\tan(2^{-n}))}a'_2 = a_2 \pm a_1(2^{-n})$$

(2.18)

where the  $\pm$  operations are used to encode the direction of rotation.

Using this method for rotation, an input vector may be rotated by successively smaller angles, until the desired angle is reached. Rotation towards zero may be achieve by observing the sign of x and y, and choosing the rotation direction accordingly. Correction for the  $\frac{1}{\cos}$  scale factor may be neglected until the end of the series of rotations, at which time the compounded correction factor may be applied as multiplication by a pre-computed constant

$$K(n) = \prod_{i=0}^{n} cos(atan(2^{-i}))$$

(2.19)

where n is the number of so called mirco-rotation iterations. Typically, one micro-rotation is needed for each bit of angular precision.

#### 2.5.5 Bidiagonalization

After QR decomposition has been performed in order to obtain an upper-triangular matrix, bidiagonalization may begin. The purpose of bidiagonalization is to bring the matrix as close its diagonal form as possible while still employing an algorithm with a deterministic run-time. Another benefit of bidiagonalization is the elimination of phase information. That is to say, a complex matrix may be bidiagonalized such that all non-zero elements are strictly real. This simplifies the subsequent diagonalization process, and reduces the amount of data transferred between the two processing stages.

The bidiagonalization is very similar to the QR decomposition process in that it can be performed using a sequence of Givens rotations to reduce all but the diagonal and superdiagonal

elements to zero. As in the QR decomposition case, reintroduction of energy into previously annihilated elements must be avoided. This may be accomplished by alternating between column elimination and row elimination.

The process of bidiagonalizing a upper-triangular matrix begins with the elimination of the upper-rightmost matrix element using a Givens rotation from the right. This corresponds to an operation involving two matrix columns. The energy from the upper-right may be rotated into any column other than the left-most column, which contains zeros below the diagonal (due to the QR decomposition stage) that should not be corrupted. Unfortunately, rotation operations that seek to eliminate elements in the first row will re-introduce energy into the sub-diagonal elements of other columns of the matrix, but this counter-productivity is unfortunately necessary. Rotations continue in this fashion until all elements in the top row, apart from the two leftmost elements, are annihilated. At this point the matrix should have the form

$$\mathbf{A} = \begin{bmatrix} a_{11} & a_{12} & 0 & \cdots & 0 \\ 0 & a_{22} & a_{23} & \cdots & a_{2n} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & a_{m2} & a_{m3} & \cdots & a_{mn} \end{bmatrix}$$

(2.20)

The next phase is the elimination of the sub-diagonal elements in the second column. When these elements have been annihilated, the second row may be targeted. All elements in the second row apart from the diagonal element and the element just to the right of the diagonal element may be eliminated without introducing energy into the previously annihilated elements. The algorithm proceeds with the elimination of sub-diagonal elements in column three and elements to the right of the super-diagonal in row four, and continues until the matrix is bidiagonal.

#### 2.5.6 Diagonalization

Diagonalizing the bidiagonal matrix is the final step in determining the singular values of the original input matrix. Many methods may be employed, but the simplest one involves the same Givens rotations as the QR decomposition and bidiagonalization algorithms. More efficient methods have been developed in [19], [20], and others. Regardless of which method is used, diagonalization is an iterative process. Each time an off-diagonal is annihilated, a non-zero value is reintroduced into a previously annihilated element. Fortunately, the process converges after several iterations [13].

### 2.6 Quantified SART Computational Requirements

The computational burden associated with the SART algorithm may be described as the number of arithmetic operations required for a single SART scan. This figure can be itemized into a list of operation counts for each stage. Another important metric is the amount of data transferred between stages, which has implications related to memory and interface bandwidth requirements. These operations counts and bandwidth requirements, which are discussed below, will be functions of the size of the signal matrix, m-by-n, where n is the number of receive elements, and m is the number of sub-carrier tones in the transmitted signal. Some of them will also be functions of the number of locations in the SART scangrid, G, or the number of ADC samples, N, collected at each receive element.

Fast Fourier Transform (FFT): The FFT algorithm for performing a Discrete Fourier Transform (DFT) has a complexity of  $O(Nlog_2(N))$  [21], where N is the length of the input array. For the SART application this length is equal to the number of time samples collected at each receive element. Because an FFT must be performed for each receiver, a factor of n must be included, resulting in a total complexity of  $O(nNlog_2(N))$ . The amount of data that flows into this stage of the algorithm is nN. Because only the frequency bins corresponding to sub-carrier tones are used, the amount of data flowing out of this stage equals the number of elements in the signal matrix, mn.

**Signal Matrix Rephasing:** The rephasing stage involves element-wise multiplication of the signal matrix with a different rephasing matrix for each scan-grid location. Assuming each complex multiplication requires 6 operations, the complexity of this stage is O(6Gmn). The amount of data in is mn. The amount of data out is Gmn.

QR Decomposition: Using a figure from [13], the complexity of QR decomposition using Givens rotations is  $O(12n^2(m-n/3))$ . Multiplying by the number of locations in the SART scan-grid gives a total complexity of  $O(12Gn^2(m-n/3))$ . The amount of data in is Gmn. The amount of data out is less, due to the elimination of the lower portion of the matrix. The amount of data flowing out of this stage is G multiplied by number of non-zero elements in an n-by-n upper triangular matrix,  $G(n^2 + n)/2$ .

**Bidiagonalization:** The number of operations required to compute bidiagonalization using Givens rotations is approximately twice the complexity of QR decomposion of an equally sized matrix. The total complexity of the bidiagonalization stage is  $O(16Gn^3)$ . The amount of data in is  $G(n^2 + n)/2$ . The amount of data out is equal to one diagonal and one super diagonal for each scan-grid location, or G(2n-1).

**Diagonalization:** According to [13], the complexity of diagonalization is O(54n) per iteration, assuming single precision, and approximately 12 operations per square-root (Intel processors generate 2 bits of precision each clock cycle for square root calculations [22]). For a scan-grid with G scan locations, and assuming a conservative 20 interations, the total complexity is O(1000Gn). The amount of data in is G2n-1. The amount of data out is Gn.

#### **Totals**

In the current implementation of SART, sixteen receive elements are used, and 103 subcarrier tones are transmitted. The signal matrix therefore has dimensions m-by-n equals 103-by-16. A moderately sized scan-grid, perhaps for a small home, consists of G = 10,000points. The number of samples collected for each receive element is N = 8192. Using these figures, the operation and data counts from above can be calculated. Table 2.6 summarizes these values, which are also represented visually in Figures 2.1 and 2.2.

| Processing Stage Name  | Operations [millions] | Data Out [MB] |

|------------------------|-----------------------|---------------|

| Fast Fourier Transform | 0.1065                | 0.0132        |

| Rephasing              | 19.78                 | 26.37         |

| QR Decomposition       | 600.1                 | 2.176         |

| Bidiagonalization      | 131.1                 | 0.496         |

| Diagonalization        | 32.00                 | 0.256         |

Table 2.1: Operation and data output counts for SART processing stages

Figure 2.1: Operation count graph for SART processing stages

Figure 2.2: Data count graph for SART processing stages

It is clear that the processing associated with the FFT is negligible compared to the rest of the algorithm. This is mainly because FFT computations only happen once per SART scan, whereas all other operations happen once for each scan location. The rephasing stage also has a relatively low complexity. However rephasing generates a lot of output data, which could lead to data transfer bottlenecks. The QR decomposition stage presents the largest computational burden because of the large signal matrix height, m, and is an excellent candidate for acceleration. The bidiagonalization stage is less complex than the QR stage, but still has high relative complexity and is a good candidate for acceleration. The diagonalization stage has lower complexity, and a good speed up (of 600/30 = 20 times) could be obtained even if its implementation remains in software.

These figures will be used in Section 4.2, when the SART algorithm is partitioned between hardware and software. The following chapter describes the hardware platform, which was selected for prototype development.

# Chapter 3

# System Platform

This chapter provides a description of the platform that was used to develop the SART coprocessor system prototype. The benefits of field programmable gate array (FPGA) technology are discussed in general terms. The selected development platform is then presented, followed by more detailed description of the FPGA device on which the platform is based.

### 3.1 Field Programmable Gate Arrays

The highest performance digital signal processing systems available today are based on custom manufactured application-specific integrated circuits (ASICs). Photo lithographic manufacturing processes provide complete flexibility, allowing almost any digital circuit to be implemented using raw semi-conductor materials. These structures may be highly optimized so that very high clock rates, in the gigahertz, may be achieved. Unfortunately, ASIC manufacturing costs currently reach into the millions of dollars for complicated digital signal processing ICs [23].

Field programmable gate arrays (FPGAs) provide a lower cost solution for custom digital signal processing systems, and are often used for ASIC prototyping. FPGAs are produced using the same manufacturing process employed for application specific circuits, but are designed such that the function of the IC is not fixed. Each FPGA contains many small blocks

of digital logic that may be configured and interconnected by specifying the contents of the FPGAs configuration memory. In this way an FPGA provides a general purpose platform for constructing custom digital systems, which may consist of many sub-systems that operate in parallel. Unfortunately, FPGAs cannot achieve the same clock rates as ASICs; they are typically about 10 time slower [24]. This is because the routing network that provides interconnection amongst the elements within an FPGA is reconfigurable and not optimized like the routing within an ASIC. Furthermore, digital logic functions that would be implemented in an ASIC using logic gates must be implemented using small look-up tables (or memory elements) within an FPGA. Because these memory elements are slower than the equivalent combinations of gates, this also limits the clock rate of an FPGA implementation. Despite these limitations, FPGAs are widely used for implementation of digital signal processing systems, especially when the flexibility of a reconfigurable platform is advantageous. FPGAs are particularly popular in the production of specialized systems, when only a few units are produced and ASIC manufacturing costs cannot not be recouped.

### 3.2 Prototyping Platform

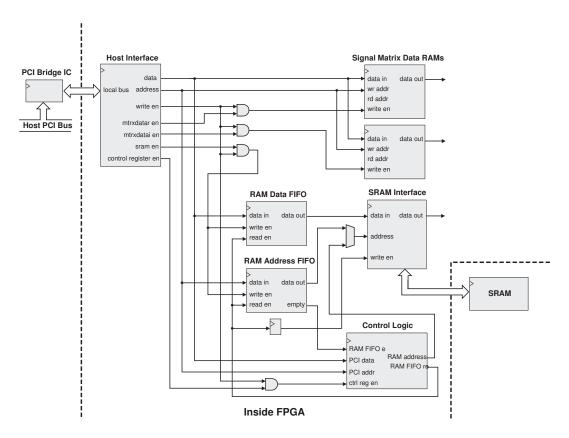

Although the final version of the SART co-processor will be implemented on a custom printed circuit board, an off-the-shelf development platform was selected for prototyping. The chosen platform is sold by Alpha Data, and is based on the Xilinx Virtex-4 SX55 FPGA. The SX55 is the largest in the SX series, which is geared towards digital signal processing applications. The Alpha Data platform is designed for compatibility with a standard PCI or PCI-X interface, and can be installed directly into a host PC. Alpha Data provides drivers and a programming interface that allow access to the FPGA using a memory-mapping scheme. In addition to the FPGA, the platform includes a PCI bridge for the host interface, and multiple banks of SRAM for data storage. A diagram of the platform is shown in Figure 3.1. The Alpha Data platform is relatively expensive, at about \$5000. However, this is because it is general purpose, and contains components that will not be necessary in the final co-processor system. For example, the high-speed SRAM ICs cost a few hundred dollars each. Because the co-processor system was designed to minimize external memory requirements, this could be replaced with one inexpensive SDRAM IC.

Figure 3.1: Diagram of the general purpose FPGA development platform from Alpha Data.

### 3.3 Virtex-4 FPGAs

When designing for an FPGA target, the architectural details of the device must be constantly considered, as they will heavily influence the final design. For example, the amount of memory available within the device will limit data storage and buffering, and the number of internal RAM banks will limit the rate at which internally buffered data can be accessed. The Virtex-4 series FPGAs are based on three types of building blocks: configurable logic blocks (CLBs), digital signal processing blocks (DSPBs), and memory blocks or "block RAM" (BRAM). In this section, these architectural elements are described. Various design challenges that arise due to the nature of these elements are noted along the way.

# 3.3.1 Configurable Logic Blocks

CLBs comprise the fundamental fabric of the FPGA. They can be used to implement all types of digital logic, including: logic gates, flip-flops, registers, state machines, and arithmetic functions. Each CLB contains four smaller blocks, known as "slices". Every slice contains two small 4-input look-up tables (LUTs), and two flip-flops. At runtime, the LUTs are configured in order to define their desired logic functions. For example, if a 4-input AND-gate is desired, then one LUT should be configured such that it outputs a logic-1 for an input consisting of four logic-1s, and a logic-0 for all other input combinations. The flip-flops may be used to register the output of the LUTs, or one of the slice inputs. Each

slice also contains additional logic for implementing a high-speed carry chain, which may be used in the implementation of binary adders or counters, and multiplexer circuitry for signal selection and dynamic routing. Multiple CLBs may be connected, using configurable routing resources, to form larger logic functions. The structures of a CLB and a logic slice are shown in Figure 3.2. The SX55 FPGA contains more than 55,000 CLBs.

In practice, the configurations of individual CLBs are almost never manually assigned. Instead, an engineer may use hardware description language (HDL) code to describe a digital circuit behaviorally or at a register transfer level. Powerful synthesis tools provided by the FPGA manufacturer, or third-party vendors, may be used to 'compile' the HDL code so that each function is automatically mapped into CLBs. However, despite this automation, the designer must always be considering the CLB architecture, and predicting how each line of code will be mapped to these functional blocks. For example, in an ASIC design, a 5-input AND-gate will have a propagation delay that is only fractionally larger than that of a 4-input gate. Whereas in an FPGA, the larger gate must be implemented using multiple LUTs, combined with multiplexer circuit to select one of the two LUT outputs. If more than two LUTs are needed for some logic function, then multiple slices or CLBs will be required, and additional routing delays must be considered.

Figure 3.2: (a) Structure of a configurable logic block (CLB) [25]. Each CLB contains four logic "slices" which are connected to neighboring slices, and to the routing network through a reconfigurable switch matrix. (b) Structure of a logic slice. Each slice contains two 4-input look-up tables, two flip-flops (or latches), multiplexers, and other supporting logic.

#### 3.3.2 Digital Signal Processing Blocks

FPGA based designs typically involve arithmetic operations. This is especially true for signal processing applications. For this reason, Virtex-4 FPGAs contain arithmetic circuit blocks, so that CLBs need not be used to implement arithmetic operations. These so called DSP blocks are highly optimized, and may be operated at higher clock rates compared to functionally equivalent CLB-based circuits. Each DSP block contains a 18-bit signed multiplier circuit, and a 48-bit adder/subtractor/accumulator circuit. Each circuit has a selectable output register, and various multiplexers and control lines are available for controlling the over-all behavior of the DSP block. Multiple DSP blocks may be cascaded to implement higher-precision operations. A simplified diagram of the Virtex-4 DSP block is shown in Figure 3.3. The SX55 contains 512 of these blocks, making it capable of highly-parallel signal processing.

Figure 3.3: Structure of a DSP Block [26]

#### 3.3.3 Block RAM

In order to allow storage and buffering of data, each Virtex-4 contains multiple blocks of dual-port SRAM. Each block has a capacity of 18kbits, and has configurable data port widths of up to 36 bits. The dual-port nature of the RAM allows simultaneous access to two memory locations, enabling the construction of first-in first-out (FIFO) type buffers, and shared memories. In fact, all necessary FIFO logic is included in each block so that CLBs need not be used. The SX55 contains 320 blocks of RAM, giving it a total of more than 5 Mbit of storage capacity, and an internal memory bandwidth greater than 9,000 Gbit/sec.

#### 3.3.4 Resource Availability Constraints

The resources available in an FPGA are fixed in both quantity and location. This leads to an additional challenge when designing a digital system that targets an FPGA. The design must be a good match to the constraints imposed by resource abundance and distribution within the targeted device. For example, if a design targeted for the SX55 consists of two sub systems, one of which consists mostly of DSP blocks, and one that is composed purely of CLBs, then each subsystem is potentially wasting half of its available resources. This is because the DSP blocks are distributed amongst the CLBs, and a module consisting only of CLBs will potentially surround one or more DSP blocks, obscuring access to their ports. It is therefore beneficial to seek a match between the resource availability ratio, and the resource consumption ratio. Achieving this balance in the SX55 can be difficult because it contains many DSP blocks, and mapping functions into these blocks can be difficult and is not fully automated in the synthesis tools.

The SX55 was selected because of its suitability to high-performance DSP applications. However, due to tight constraints on CLB resources, this selection may not be completely appropriate. Section 7.1 contains a discussion about how other devices may be used in future versions of the SART accelerator. Table 3.1 contains information about the resource availability on various Virtex-4 devices. The current low-volume cost per device is also shown.

|        | Resources Available |      |      |              |

|--------|---------------------|------|------|--------------|

| Device | DSP Blocks          | CLBs | BRAM | Approx. Cost |

| LX60   | 64                  | 60k  | 160  | \$600        |

| LX80   | 80                  | 80k  | 200  | \$1000       |

| LX100  | 96                  | 110k | 240  | \$1600       |

| LX160  | 96                  | 152k | 288  | \$3200       |

| LX200  | 96                  | 200k | 336  | \$6000       |

| SX35   | 192                 | 35k  | 192  | \$550        |

| SX55   | 512                 | 55k  | 320  | \$1100       |

| FX40   | 48                  | 41k  | 144  | \$600        |

| FX60   | 128                 | 56k  | 232  | \$1000       |

| FX100  | 160                 | 94k  | 376  | \$2000       |

| FX140  | 192                 | 142k | 552  | \$4800       |

Table 3.1: Available resources on various devices in the Xilinx Virtex-4 family FPGAs. Note: the FX series devices include additional features such as PowerPC processing cores, Ethernet MACs, and high-speed IO transceivers.

# Chapter 4

# SART Co-processor Architecture

The purpose of this work was to design a digital system capable of accelerating computations associated with the SART algorithm. The system needed to provided a solution that was compact and low-power compared to a cluster of general purpose computers. The accuracy of the output needed to be comparable to the existing solution, which employs single-precision floating point arithmetic. The system also needed to be scalable in order to accommodate larger signal matrices in the likely event that the number of receive elements or sub-carriers was increased. This chapter begins with a discussion of the design approach that was used to meet these goals. The SART algorithm is then partitioned into tasks suitable for hardware and software implementations. Remaining sections contain a description of the SART co-processor system, and all of its sub components.

# 4.1 Design Approach

The power and size requirements were satisfied by selecting FPGAs as the main processing elements. FPGAs consume less space and power than a PC with equivalent signal processing capabilities [24]. Like PCs, additional FPGAs may be used in parallel to obtain any processing performance required. An FPGA-based design also has the added benefit of being readily portable to an ASIC process [23]. Once optimized and implemented as an ASIC the design will run at clock frequencies up to 10 times higher, and consume even less power. Almost any